# Semiconductor industry – Challenges and Opportunities

Yogesh S. Chauhan

Assistant Professor and Ramanujan Fellow Nanolab, Department of Electrical Engineering IIT Kanpur

Email: <a href="mailto:chauhan@iitk.ac.in">chauhan@iitk.ac.in</a>

Homepage — <a href="http://home.iitk.ac.in/~chauhan/">http://home.iitk.ac.in/~chauhan/</a>

## Outline

- Hyperconnected Age

- Role of semiconductors

- What is semiconductor

- MOSFET and Scaling

- Multigate Transistors

- FinFET

- Thin-Body Transistor

- Compact Modeling of FinFET and UTB FET

- What next?

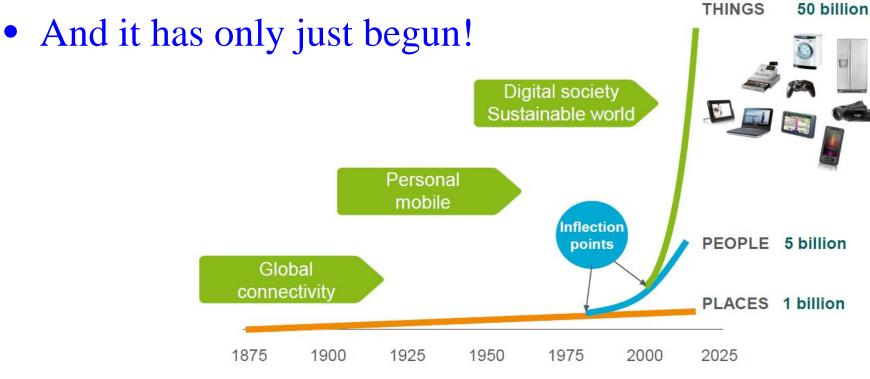

## Hyperconnected Age

We are living in an unprecedented era of hyperconnectivity that is redefining our societies, cultures, and communications.

## Hyperconnected Age

#### Present

- Facebook has more than 1.4

billion users worldwide,

creating a hyperconnected,

global social network

- Human to Device interaction

#### Future

- Device to Human interaction

- Device to Device interaction

CISCO – By 2020, there will be 50 billion networked devices.

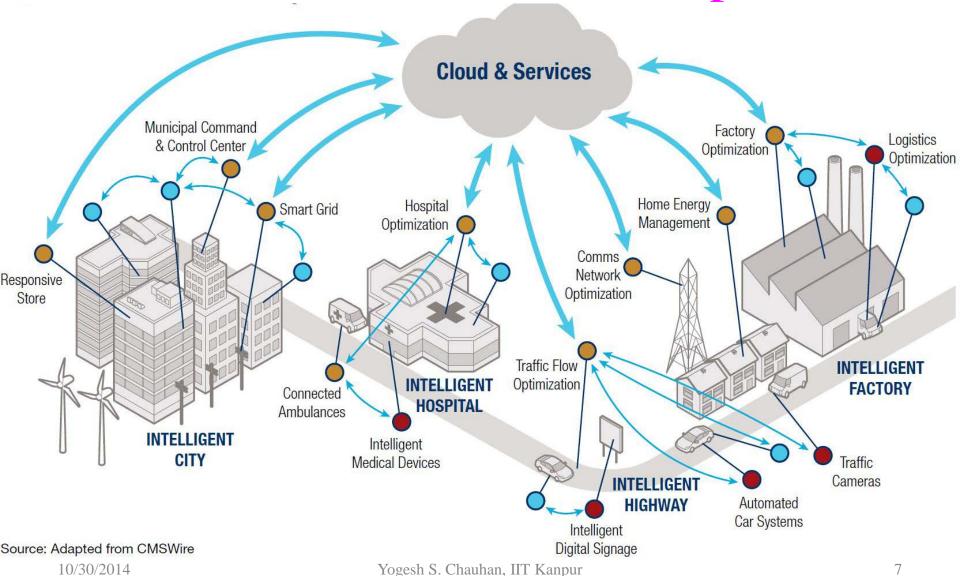

## Electronics industry

- Playing important role in making this planet smarter!

- Key enabling technologies

- Internet of things

- Cloud

- Healthcare

- Robotics

- Automobile

- Food

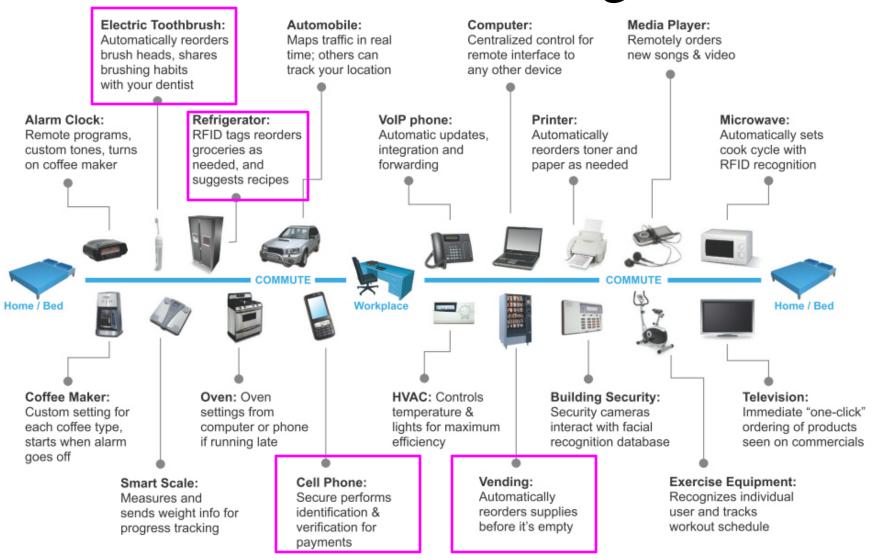

## Internet of things

## IoT & Cloud – Data and Computation

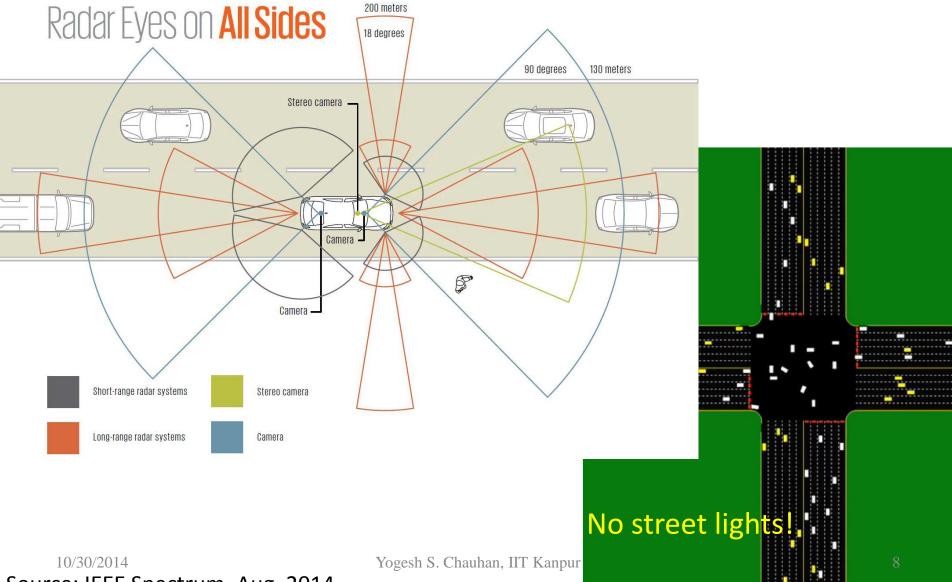

## Automobile – Driverless car

Source: IEEE Spectrum, Aug. 2014

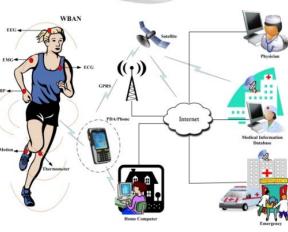

## Wearable Electronics

#### **Smart Watch**

With chips shrinking and sensors becoming cheaper, personal computing is moving from that smartphone in your pocket to your arm, your wrist, right out to your fingertips.

#### Wristbands With the Nike+ Fuel Band, your gym workout just got more

High-tech fabric Items such as knee socks from Uniqlo convert evaporating moisture on your body to heat

transparent

#### Google Glass

#### ST analog portfolio Wardrobe change on the go for wearable Clothes can light up, advertise, change colors or become

Need ultra-low power devices and sensors

© 2013 MCT

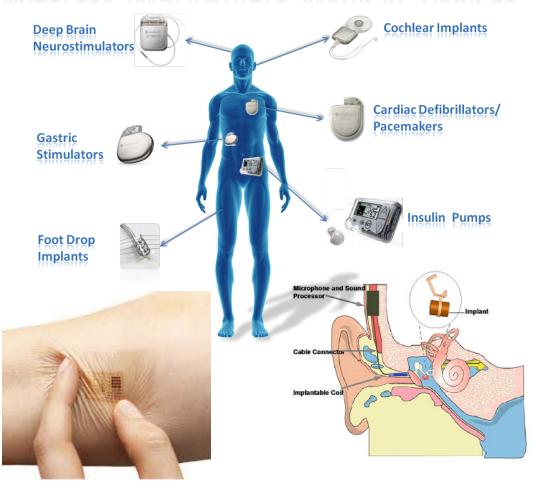

## Healthcare – Implantable Electronics

# Description of the second of t

#### WIRELESS IMPLANTABLE MEDICAL DEVICES

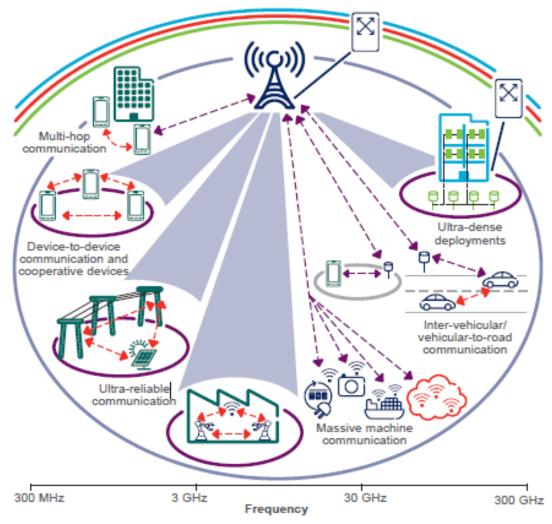

## 5G – Machine communication

- Communication

- Device to device

- Machine to machine

- Vehicle to vehicle

- UHD live video

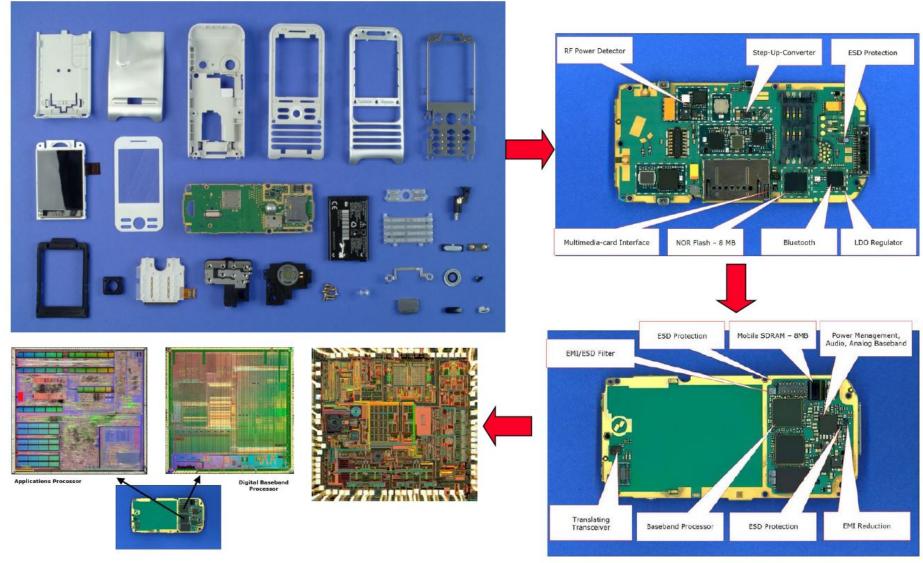

## The Deconstructed Cell Phone

**Hint: It's All About the Microelectronics!**

# Semiconductors – Heart of technological progress and innovation

• The semiconductor is one of the most pervasive and powerful inventions in human history.

Nobel Prize in Physics 2014 "invention of efficient blue LEDs"

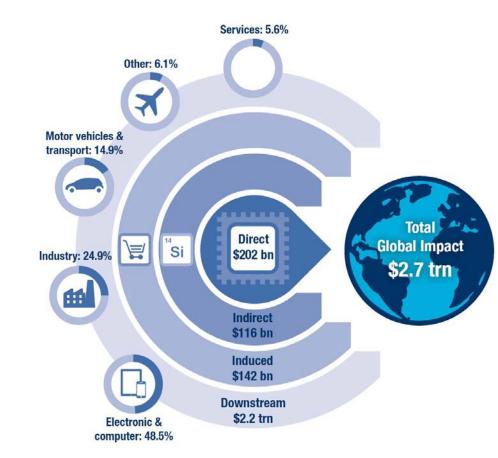

## Economic impact of semiconductors

- Semiconductors touch every sphere of economic activity.

- Direct: ~\$300 bn

- Indirect

- Material/equipment

- Induced

- consumer market

- Downstream

- Other industry

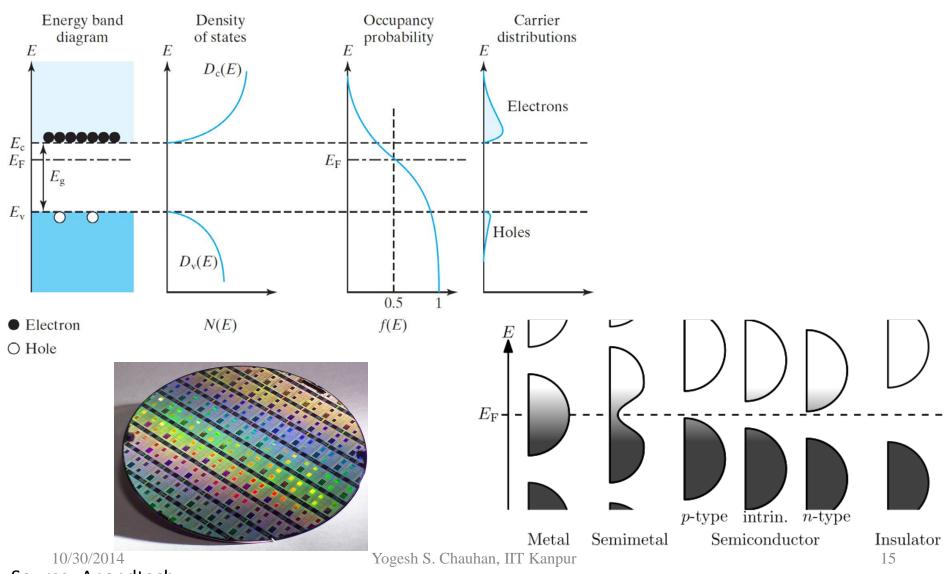

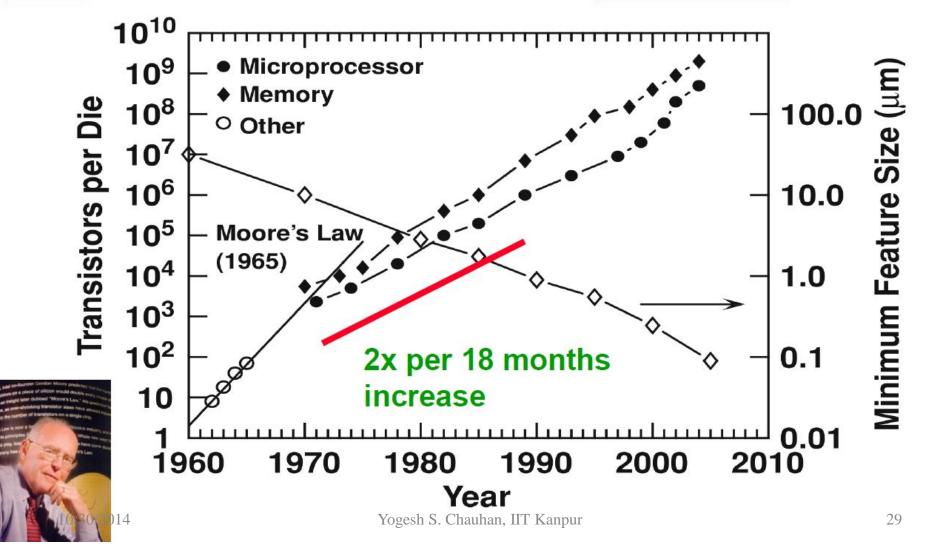

## What is semiconductor?

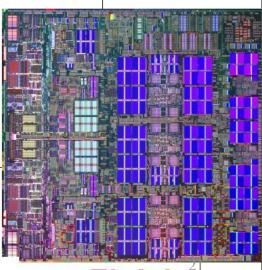

Source: Anandtech

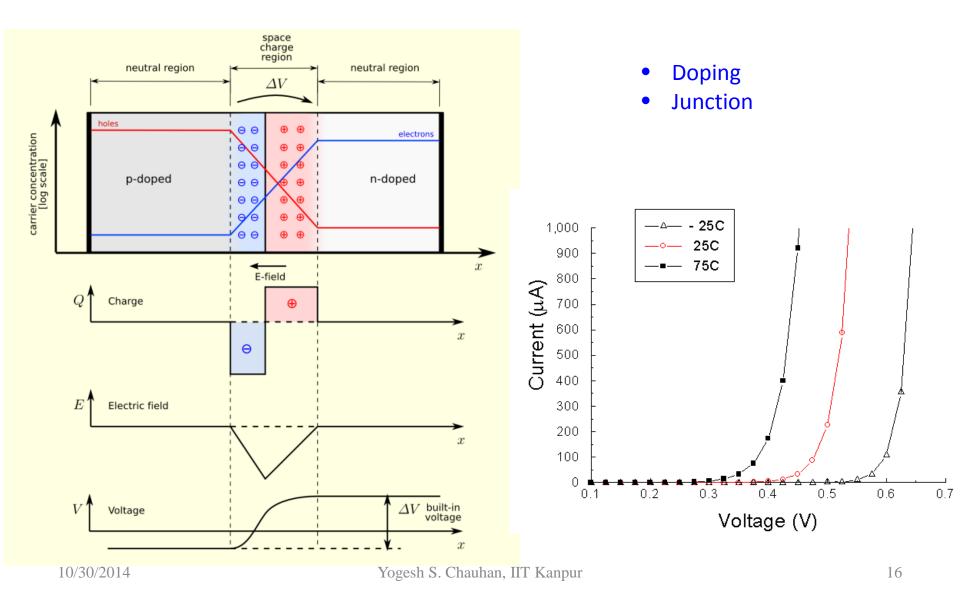

## Semiconductor Devices – Junction

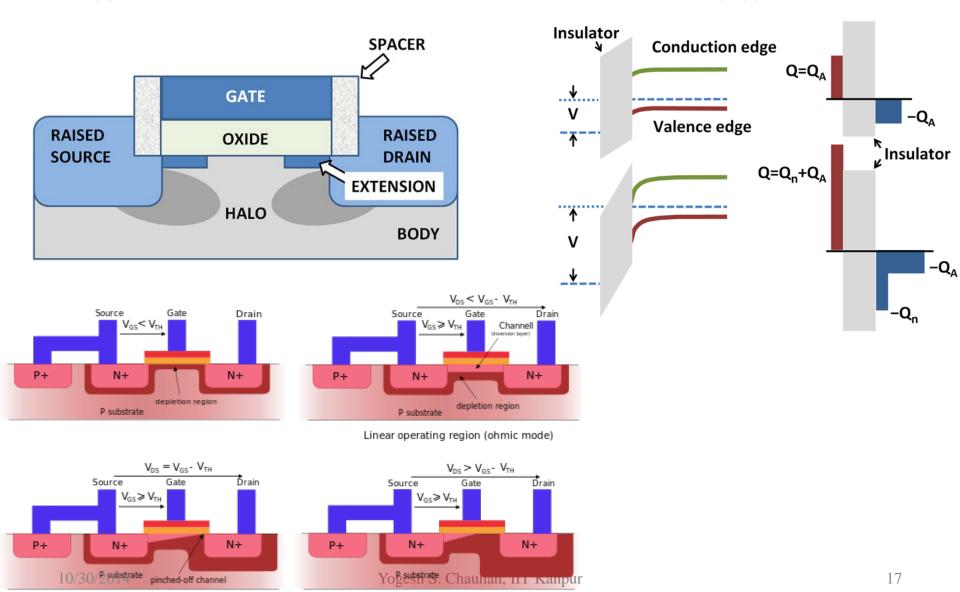

## Semiconductor Devices – MOSFET

Saturation mode

Saturation mode at point of pinch-off

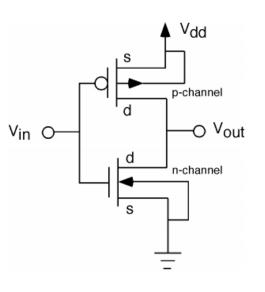

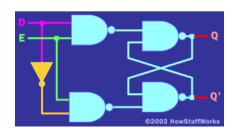

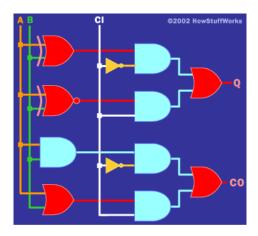

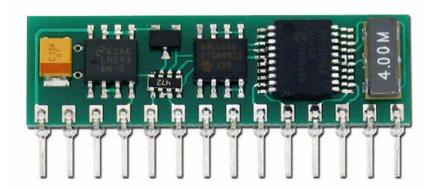

## Semiconductor devices to circuits

#### Flip-flop

NOT gate

Full Adder

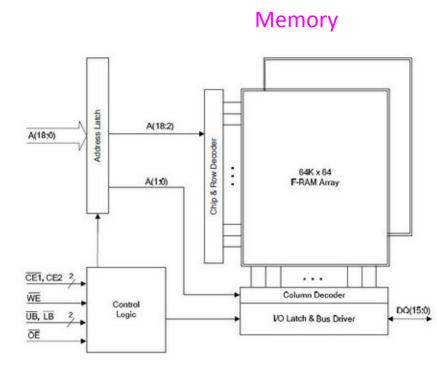

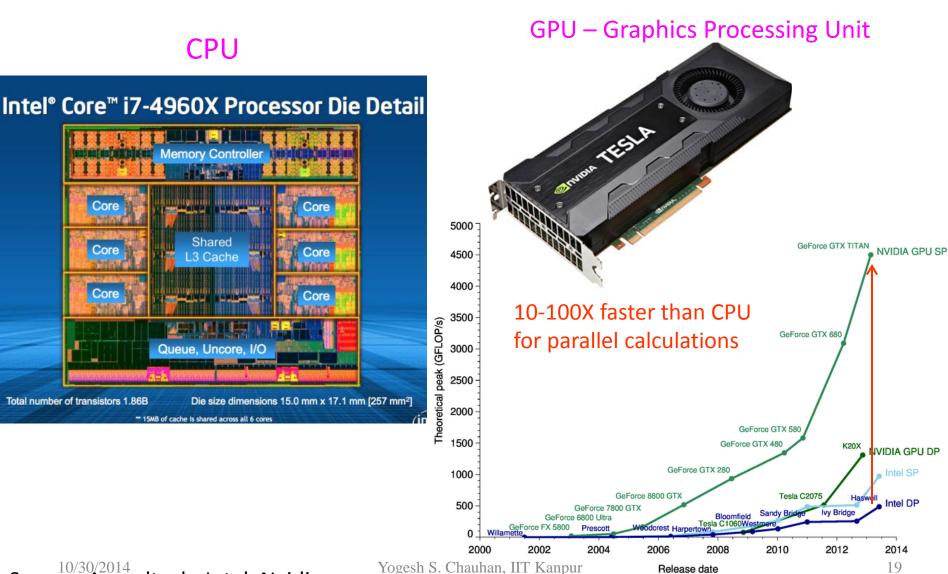

## Semiconductor circuits to Products

Source: Anandtech, Intel, Nvidia

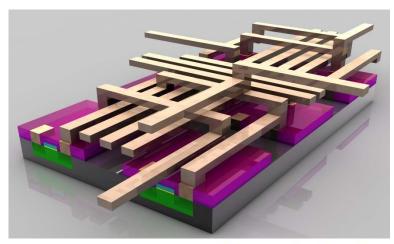

## Today's ICs

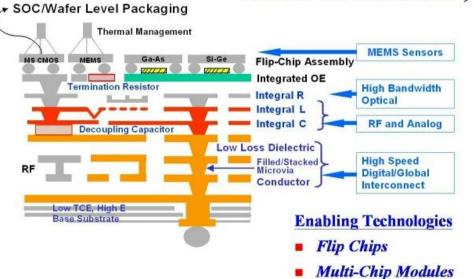

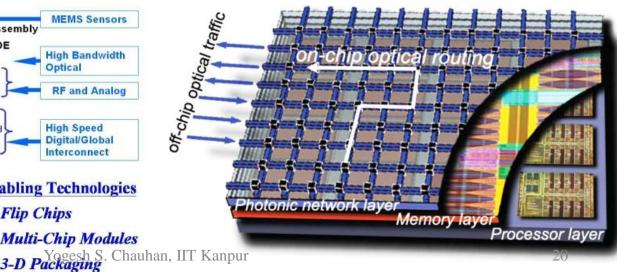

#### Multiple metal layers

3D ICs

#### System in Package (SIP)

Substrate **Heat Sink**

10/30/2014

## How do you make these?

**Silicon Crystals**

Silicon "Wafers"

**Bunny Suits!**

\$5B Fabrication Facility

10B Transistors per cm<sup>2</sup>

**Finish**

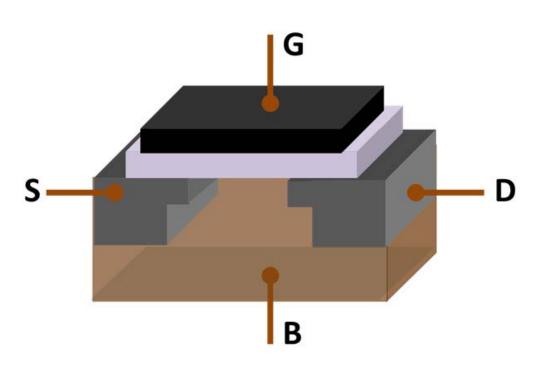

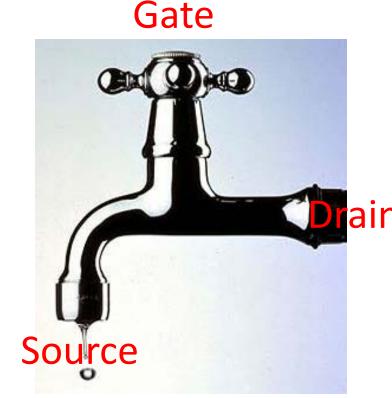

## Building block – (tiny) MOSFET!

• MOSFET is a transistor used for amplifying or switching electronic signals.

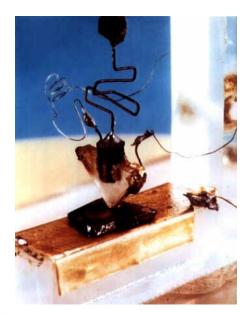

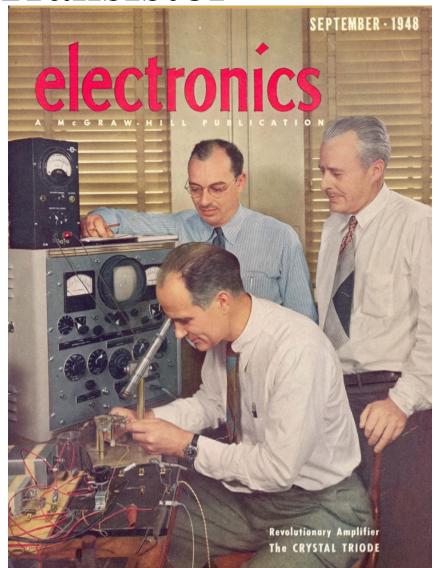

## Invention of Transistor

- First Transistor (1947-1948) at AT&T's Bell Labs

- Point Contact Transistor

- First transistor was bipolar contact transistor

- Material Germanium

## Invention of Transistor

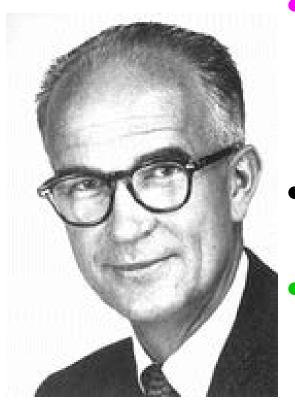

William Shockley

- Worked on theory of Diode, Transistor, Thyristor etc.

- Invented First transistor at Bell Labs

- Received Nobel Prize in 1956

- Formed Shockley semiconductor in Mountain View, California in 1956

- Employees of Shockley semiconductor (Robert Noyce, Gordon Moore, ....)

- These employees opened 65 companies in next 20 years including Intel, AMD, Fairchild,...

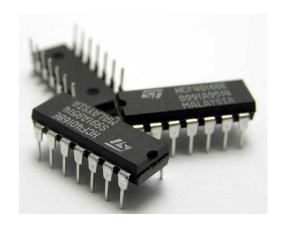

## Integrated Circuit (IC)

- IC Electronic circuit manufactured on the surface of a thin substrate of semiconductor material.

- Additional materials are deposited and patterned to form interconnections between semiconductor devices.

• ICs are used in virtually all electronic equipment today and have revolutionized the world of electronics.

## Invention of Integrated Circuits

- Jack Kilby (at *Texas Instruments*) demonstrated first working IC in 1958.

- Jack Kilby was awarded the Nobel Prize in Physics 2000.

- Kilby's work was named an IEEE Milestone in 2009.

First IC

First handheld Calculator

- Robert Noyce (at *Fairchild Semiconductor*) also invented IC separately six months later than Kilby.

- It was made of silicon, whereas Kilby's chip was made of germanium.

- Fairchild Semiconductor was also home of the first silicon gate IC technology with self-aligned gates, which stands as the basis of all modern CMOS computer chips.

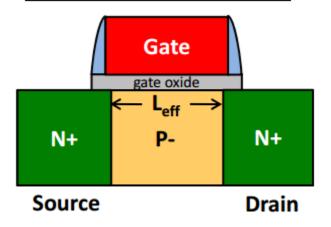

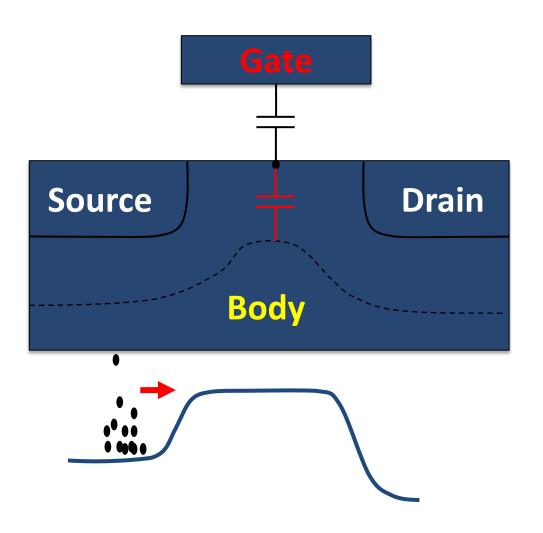

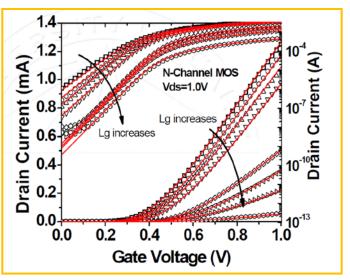

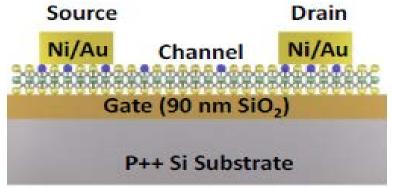

## **Bulk MOSFET**

#### **Schematic Cross Section**

#### **Desired**

- High I<sub>ON</sub>

- Low I<sub>OFF</sub>

#### Barrier height is controlled by gate voltage

10/30/2014

Yogesh S. Chauhan, IIT Kanpur

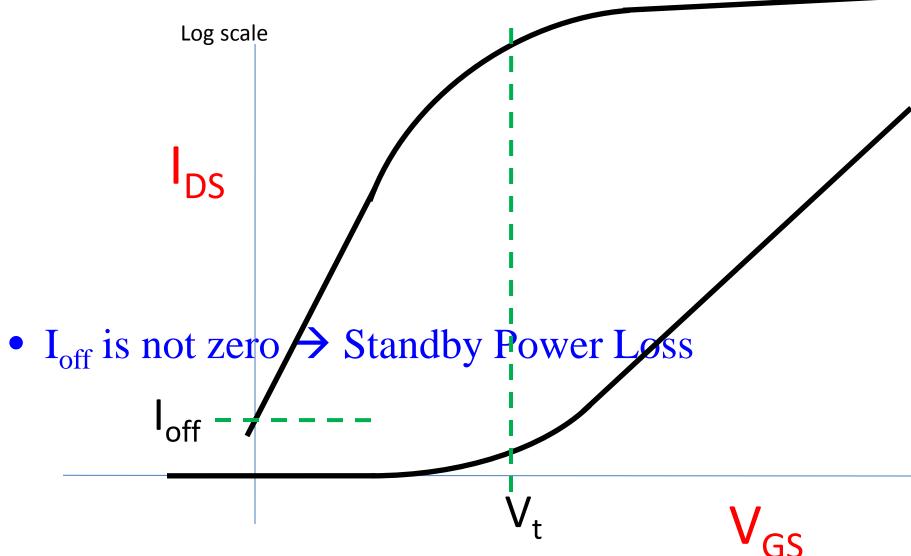

## **Bulk MOSFET**

• Drain current in MOSFET (ON operation)

$$I_{ON} = \mu \frac{W}{L} C_{ox} (V_{DD} - V_{TH})^2$$

• Drain current in MOSFET (OFF operation)

$$I_{OFF} \propto 10^{\left(\frac{V_{GS} - V_{TH}}{S}\right)}$$

Desired

- $C_{ox} = \varepsilon_{ox}/t_{ox} = oxide cap.$ S – Subthreshold slope

- High  $I_{ON}$  ( $\downarrow L$ ,  $\uparrow Cox$ ,  $\uparrow V_{DD}$ - $V_{TH}$ )

- Low  $I_{OFF} (\uparrow V_{TH}, \uparrow S)$

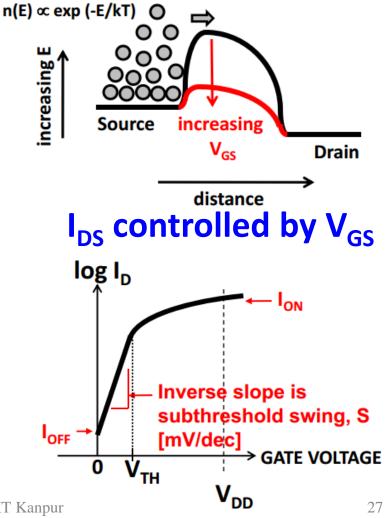

#### Moore's Law:

The defining features of the integrated circuit technology (size, speed, cost) follow an <u>exponential</u> growth pattern over time

**Moral**: Computing power **1** while cost **↓** exponentially!

## Technology Scaling drives down the cost

- Scaling: At each new node, all geometrical features are reduced in size to 70% of the previous node.

- **Reward:** Reduction of *circuit size by half*.

- Twice number of circuits on each wafer

- Cost per circuit is reduced significantly.

$$I_{ON} = \mu \frac{W}{L} C_{ox} (V_{DD} - V_{TH})^2$$

### Moore's Law It's not technology! → It's economy.

In 1978, a commercial flight between New York and Paris cost around \$900 and took seven hours. If the principles of Moore's Law had been applied to the airline industry the way they have to the semiconductor industry since 1978, that flight would now cost about a penny and take less than one second.

- Ways to Huge Profits

- High performance and Low Cost

- Achieved by making everything SMALLER

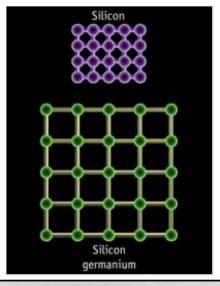

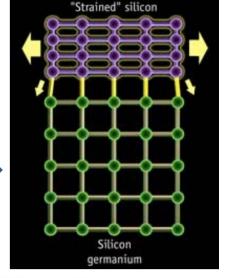

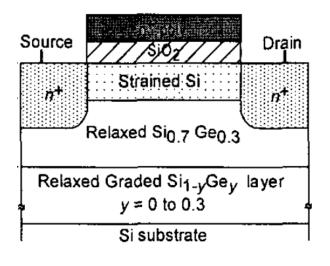

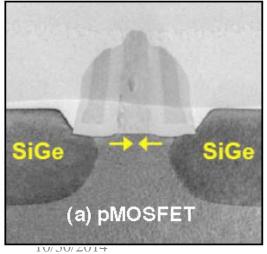

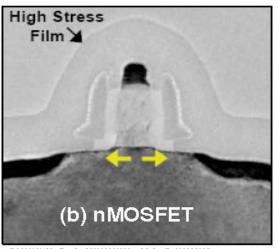

## Strained Silicon $I_{ON} = \mu \frac{W}{L} C_{ox} (V_{DD} - V_{TH})^2$

#### Silicon is placed on substrate having large atomic spacing

10gesh 5. Chauhan, H 1 Kanpur

#### Methods of straining

- -Burried SiGe –Biaxial

- -Uniaxial Stress S/D SiGe

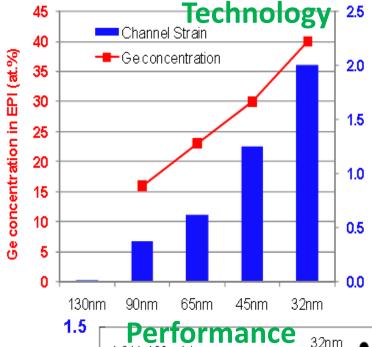

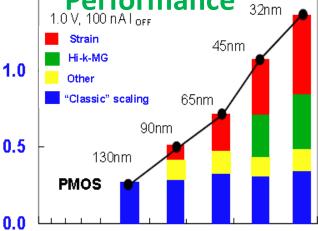

## Technology Trend

2003 <u>90 nm</u> 2005 65 nm 2007 45 nm 2009 32 nm 2011

<u>22 nm</u>

Invented SiGe Strained Silicon

2<sup>nd</sup> Gen. SiGe Strained Silicon

Source: www.intel.com

Invented Gate-Last High-k Metal Gate

2<sup>nd</sup> Gen. Gate-Last High-k Metal Gate

First to Implement Tri-Gate

Tri-Gate

Strained Silicon

#### **Product**

Penryn

Intel\* Core

Microarchitecture

TICK

As nm

Process Technology

Nehalem

NEW Intel\*

Microarchitecture

TICK

TOCK

#### High-k Metal Gate

Drive Current (mA/um) 0.5

1000

10/30/2014

Yogesh S. Chauhan, IIT Kan

100

Channel Strain (GPa)

Gate Pitch (nm)

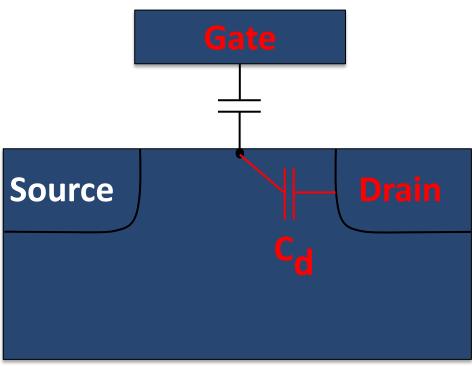

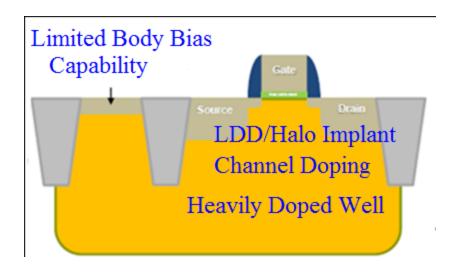

## Thin Depletion Layer - Problem

- $Q_G = Q_i + Q_b$

- Charge sharing

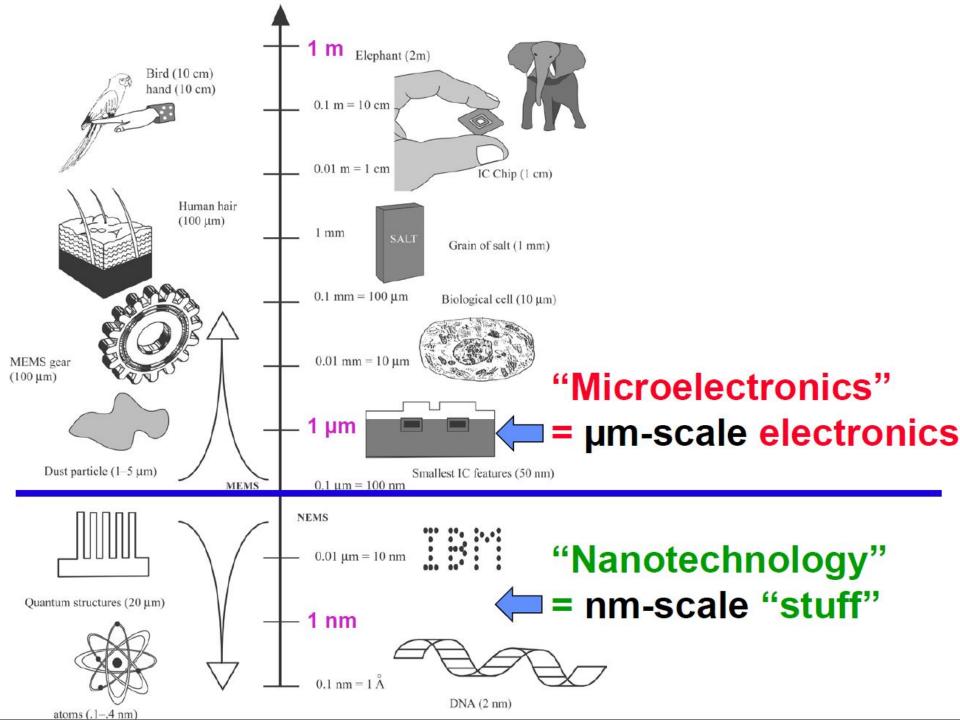

## Current in MOSFET

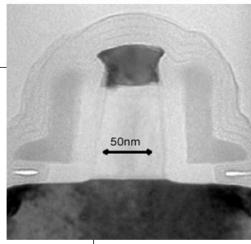

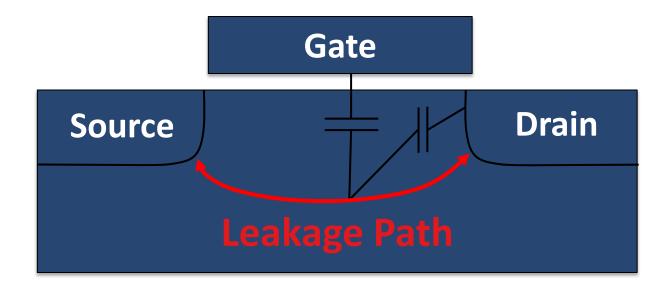

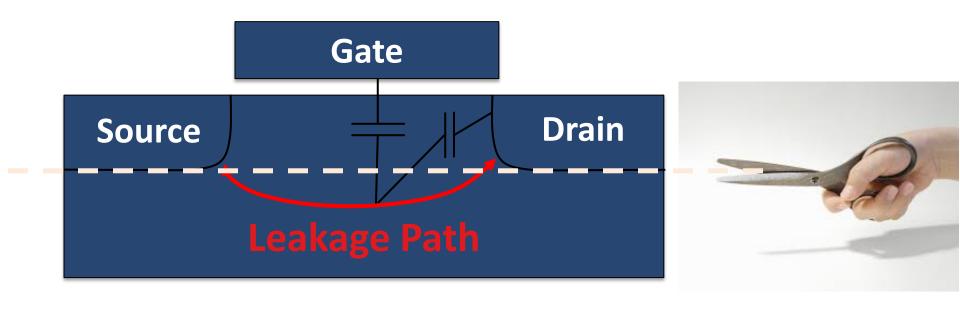

## Short Channel – Big Problem

#### MOSFET becomes "resistor" at small L.

Chenming Hu, "Modern Semiconductor Devices for ICs" 2010, Pearson

## Making Oxide Thin is Not Enough

Gate cannot control the leakage current paths that are far from the gate.

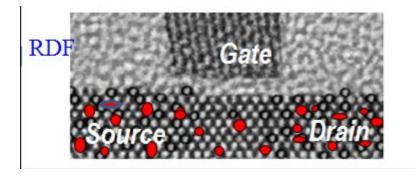

#### Good Old MOSFET has reached its Limits

- Ioff is bad

- Size and dopant variations

High Vdd, Power, Design Cost

#### What can we do?

#### May 4, 2011

#### The New York Times Front Page

• Intel will use 3D FinFET at 22nm

• Most radical change in decades

There is a competing SOI technology

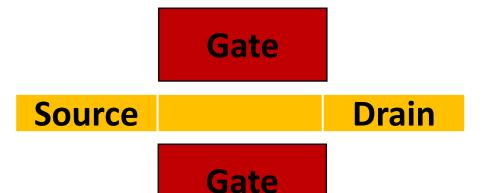

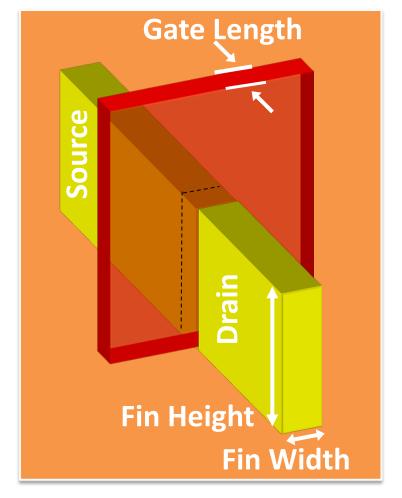

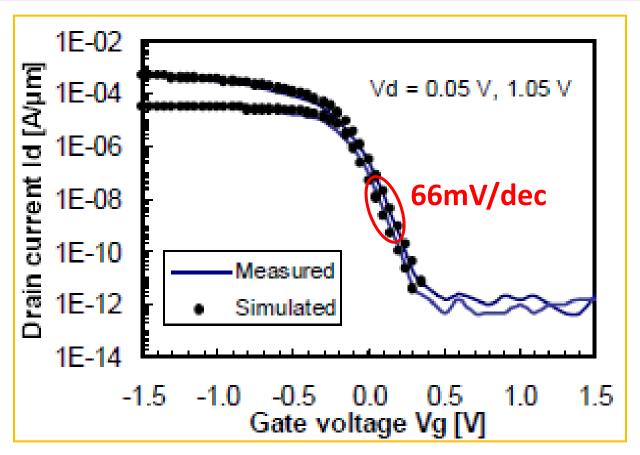

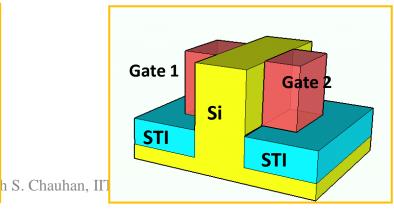

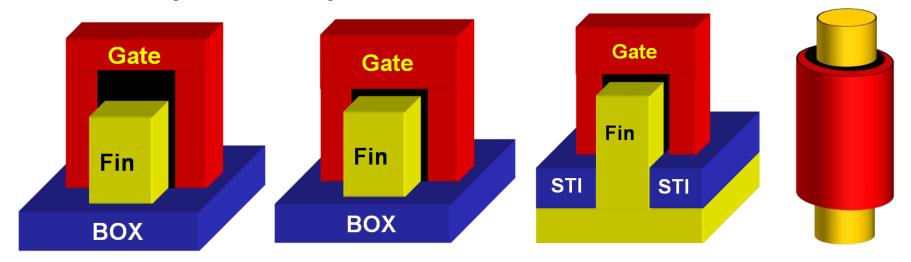

## One Way to Eliminate Si Far from Gate

Thin body controlled By multiple gates.

FinFET body is a thin Fin.

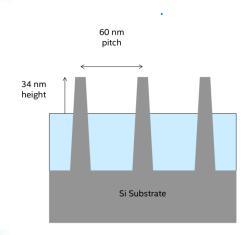

#### 40nm FinFET – 1999

#### 30nm Fin allows 2.7nm SiO2 & undoped body

ridding random donant fluctuation

# Introduced New Scaling Rule Leakage is well suppressed if

Fin thickness < Lg

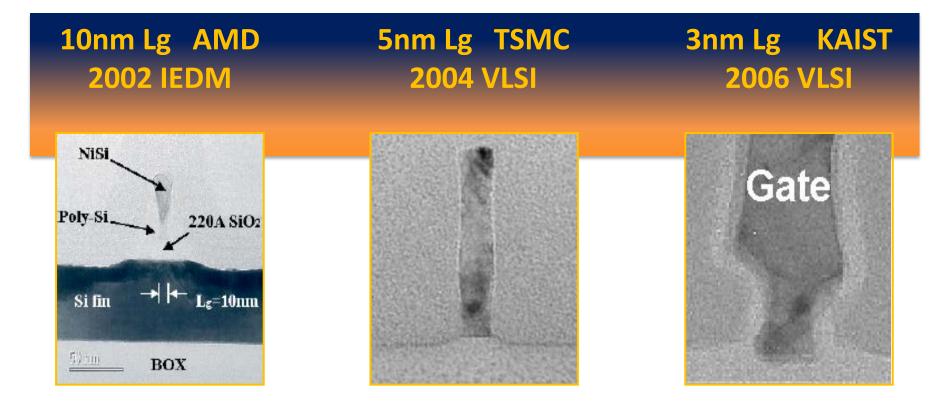

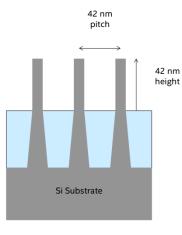

#### State-of-the-Art 14nm FinFET

#### Transistor Fin Improvement

22 nm 1<sup>st</sup> Generation Tri-gate Transistor

14 nm 2<sup>nd</sup> Generation Tri-gate Transistor

22 nm Process

14 nm Process

Taller and Thinner Fins for increased drive current and performance

Higher Transistor Performance (switching speed)

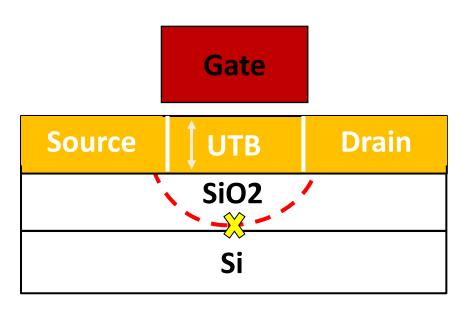

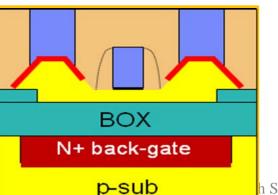

## 2<sup>nd</sup> Way to Eliminate Si far from Gate

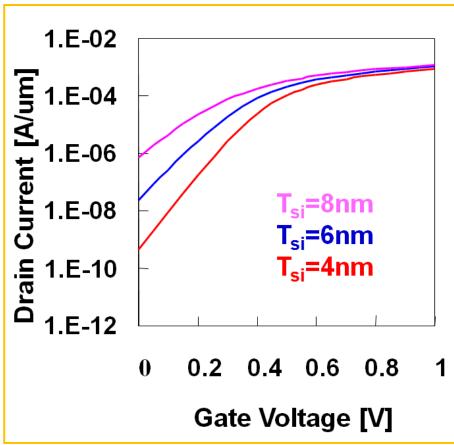

#### **Ultra-thin-body SOI (UTB-SOI)**

Y-K. Choi, IEEE EDL, p. 254, 2000

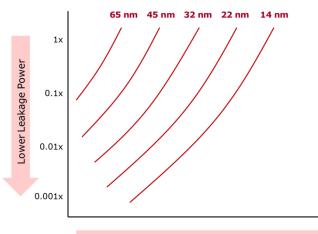

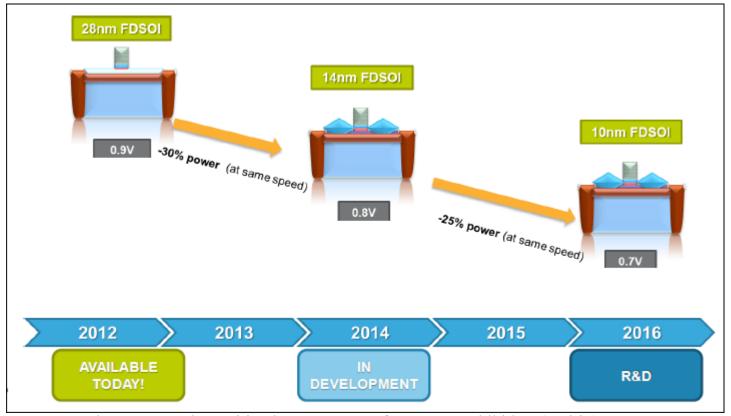

## FDSOI Roadmap

From a global cooperation ST-IBM-LETI have enabled an FD-SOI 3-node roadmap.

#### Main Differences

**FinFET**

Body thickness < Lg

Investment by fab

Has larger Ion

UTB-SOI

Thickness <1/3Lg

Investment by SOI suppliers

Has good back-gate bias option

**UTB-SOI**

FinFET

### Compact Modeling or SPICE Modeling

- Good model should be

- Accurate: Trustworthy simulations.

- Simple: Parameter extraction is easy.

- Balance between accuracy and simplicity depends on end application

- Excellent Convergence

- Simulation Time ~μsec

- Accuracy requirements

- − ~ 1% RMS error after fitting

- Example: BSIM6, BSIM-CMG

#### BSIM-CMG and BSIM-IMG

- Berkeley Short-channel IGFET Model

- First industry standard SPICE model for IC simulation

- Used by hundreds of companies for IC design since 1997

- BSIM FinFET model became industry standard in March 2012

It's Free

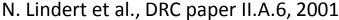

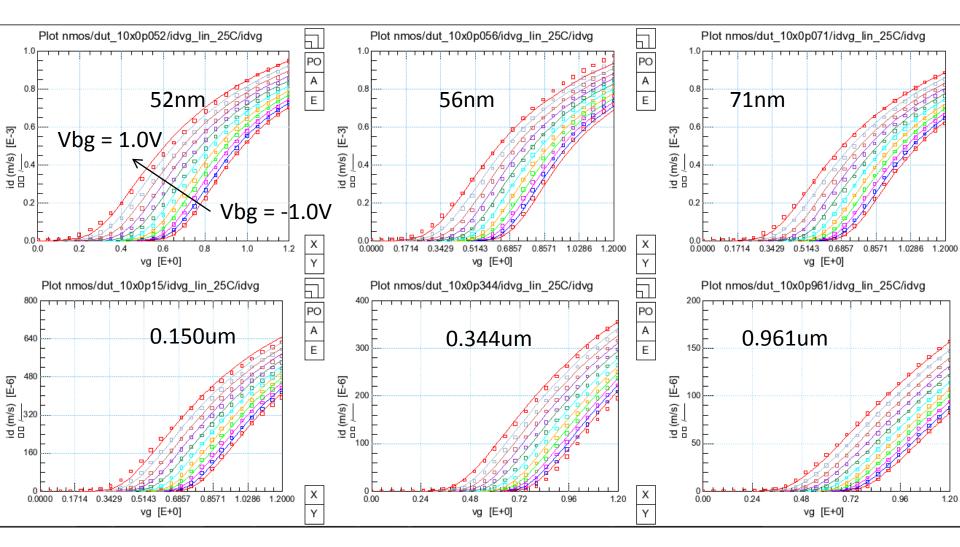

## BSIM-IMG: Length scaling@low Vds

## Common-Multi-Gate Modeling

- Common Multi-gate (BSIM-CMG):

- All gates tied together

- Surface-potential-based core I-V and C-V model

- Supports double-gate, triple-gate, quadruple-gate, cylindrical-gate; Bulk and SOI substrates

#### **BSIM-CMG**

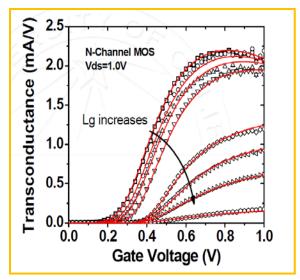

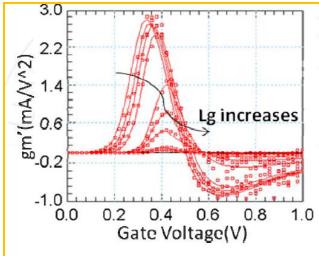

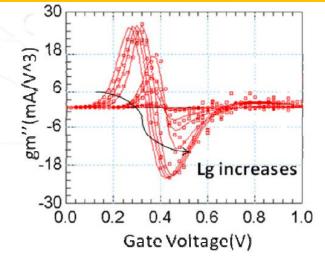

### Global fitting with 30nm–10µm FinFETs

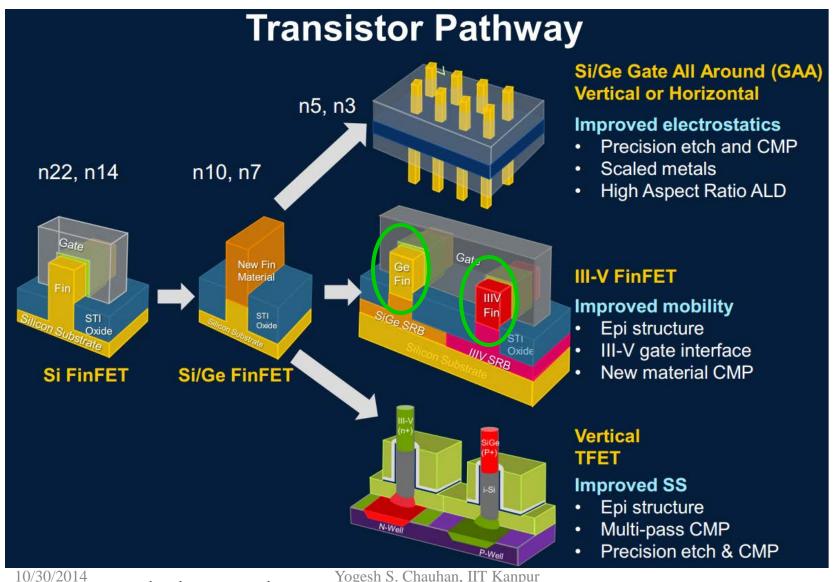

#### What Next?

Source: Applied Materials

Yogesh S. Chauhan, IIT Kanpur

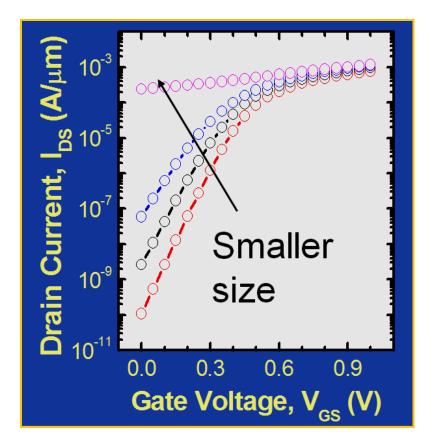

## Modeling of III-V FinFET

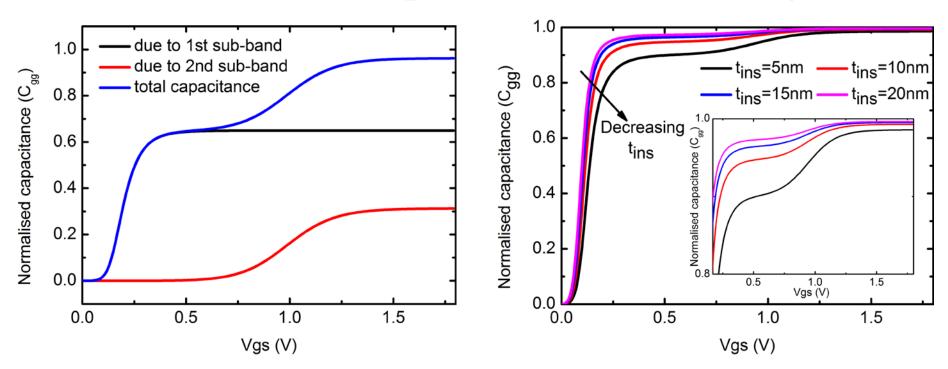

#### **Quantum Capacitance Modeling**

Avirup Dasgupta et. al., "Analysis and Modeling of Quantum Capacitance in III-V Transistors", submitted in ICEE Bangalore, 2014.

## Modeling of III-V FinFET

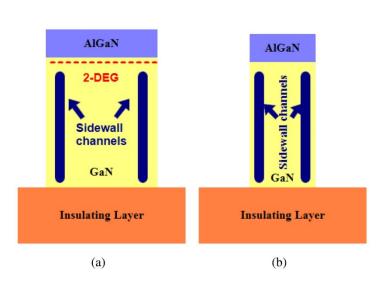

Fig. 1. Schematic showing sidewall channels and 2-DEG channel in AlGaN/GaN based FinFET devices; (a) Wide fin-width device, (b) Narrow fin-width device [12].

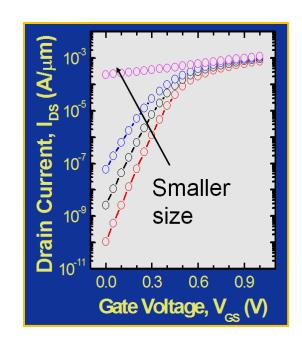

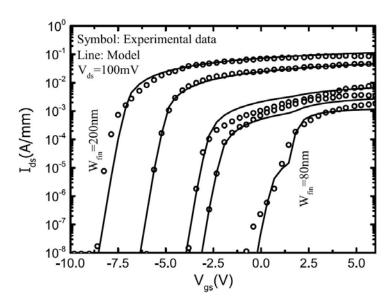

Fig. 3. Subthreshold behaviour of model with experimental data [12], for  $W_{fin}$ =80nm, 120nm, 140nm, 180nm and 200nm and  $Lg=1.0\mu m$ . Drain current is normalized with total gate width  $(W_{fin}+2H_{fin})$ , where  $H_{fin}=120nm$ .

• Chandan Yadav et. al., "Modeling of GaN-Based Normally-Off FinFET", IEEE ELECTRON DEVICE LETTERS, June 2014.

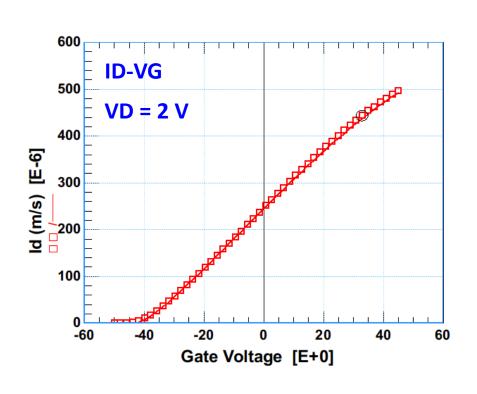

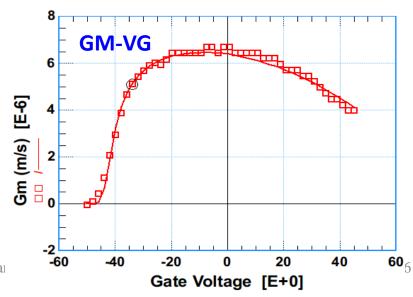

# Forward Looking Modeling of 2D Semiconductor FET

Yogesh S. Chauhar

## Joint Development & Collaboration

Working closely with universities/companies on model development and support

## Upcoming Book on FinFET Model

# FinFET Modeling for IC Simulation and Design: Using the BSIM-CMG Standard

## FinFET Modeling for IC Simulation & Design

**Using the BSIM-CMG Standard**

Yogesh Singh Chauhan

Darsen Lu

Sriramkumar Venugopalan

Sourabh Khandelwal

Juan Pablo Duarte

Navid Paydavosi

Ali Niknejad

Chenming Hu

#### **Chapters**

- 1. FinFET- from Device Concept to Standard Compact Model

- 2. Analog/RF behavior of FinFET

- 3. Core Model for FinFETs

- 4. Channel Current and Real Device Effects

- 5. Leakage Currents

- 6. Charge, Capacitance and Non-Quasi-Static Effect

- 7. Parasitic Resistances and Capacitances

- 8. Noise

- 9. Junction Diode Current and Capacitance

- 10. Benchmark tests for Compact Models

- 11. BSIM-CMG Model Parameter Extraction

- 12. Temperature Effects

## Summary

- Future is beyond imagination.

- Challenges

- Technology Hardware and Software

- Need Innovation

- Opportunities

- Entrepreneurship

- Research

- Jobs (private/public)

- Knowledge economy

## Are you ready?

**Present**

**Future**