# Fundamentals and Recent Progress in Negative Capacitance Transistors

Yogesh S. Chauhan

**Associate Professor**

Nanolab, Department of Electrical Engineering IIT Kanpur, India

Email: <a href="mailto:chauhan@iitk.ac.in">chauhan@iitk.ac.in</a>

Homepage – <a href="http://home.iitk.ac.in/~chauhan/">http://home.iitk.ac.in/~chauhan/</a>

#### Nanolab@IITK

#### Current members – 30

- Postdoc 3

- Ph.D. − 19

- Seven PhD graduated

#### **Funding:**

DST, SERB, CSIR, ISRO, DRDO, SRC, IBM, UCB, CMC, Maxlinear, ...

|            | 2019 | 2018 | 2017 | 2016 | 2015 |

|------------|------|------|------|------|------|

| Books      | 1    |      |      |      | 1    |

| Journal    | 13   | 20   | 19   | 18   | 9    |

| Conference | 11   | 19   | 11   | 30   | 30   |

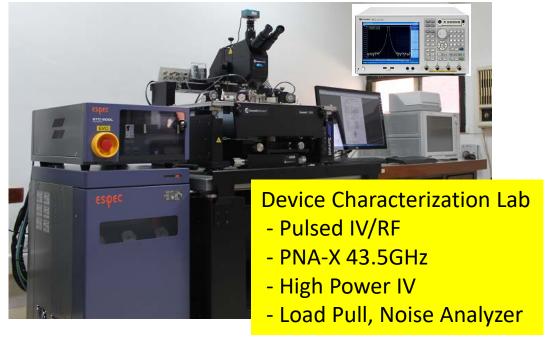

## Nanolab@IITK: From Theory to Applications

#### **Theory**

Materials

Atomistic Sim.

Semiconductors

Transport

#### **Applications**

Fabrication

Characterization

SPICE Models

Circuit Design

## Joint Development & Collaboration

CITM GMERIE SYNOPSYS® cādence®

## What is a Compact Model?

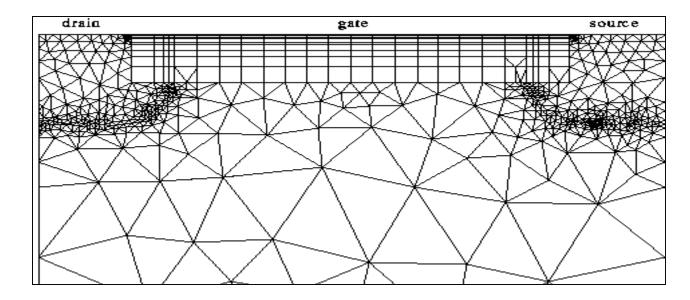

### Compact MOSFET Model

Compact Model

TCAD Model

#### Compact Modeling or SPICE Modeling

- Good model should be

- **Accurate:** Trustworthy simulations.

- Simple: Parameter extraction is easy.

- Balance between accuracy and simplicity depends on end application

- Excellent Convergence

- Simulation Time ~μsec

- Accuracy requirements

- − ~ 1% RMS error after fitting

- Example: BSIM-BULK, BSIM-CMG, BSIM-IMG

#### Industry Standard Compact Models

Standardization Body – Compact Model Coalition

CMC Members – EDA Vendors, Foundries, IDMs,

Fabless, Research Institutions/Consortia

http://www.si2.org/cmc/

## Challenges in Compact Modeling

**Materials Physics** (Si, Ge, III-V) (Quantum Mechanics, Transport) **SPICE Model** Maths/ Electronics Computer Sc. (Circuit considerations – (Compiler, Function speed, Digital/Analog/RF/noise) implementation, algorithms, smoothing, integration, PDE)

### Some Snapshots from recent work

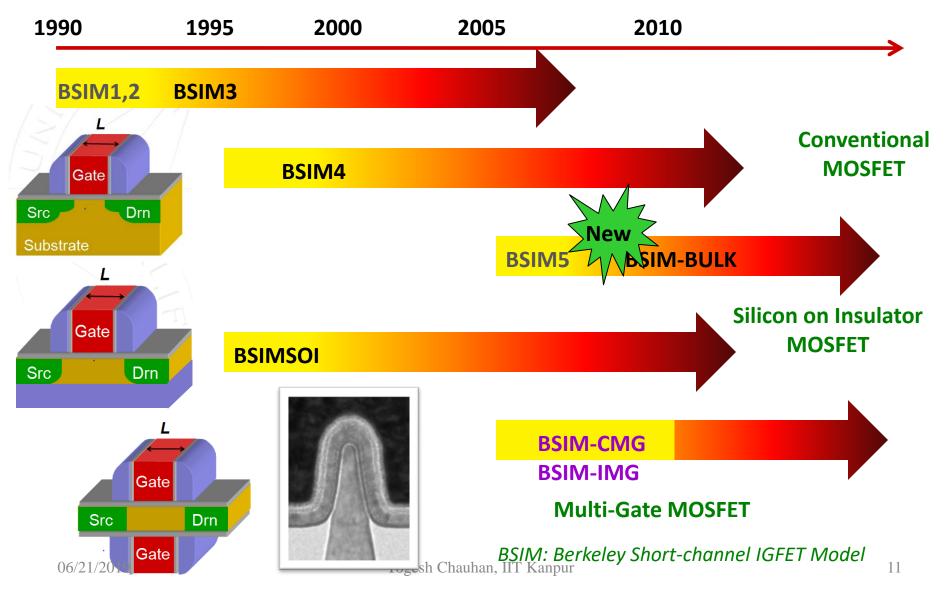

#### BSIM Family of Compact Device Models

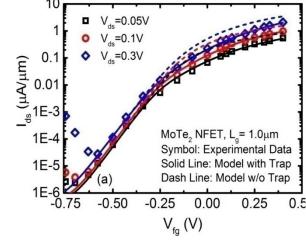

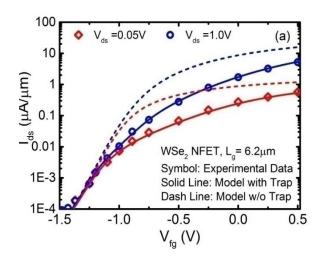

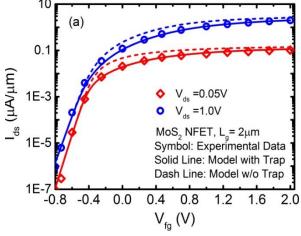

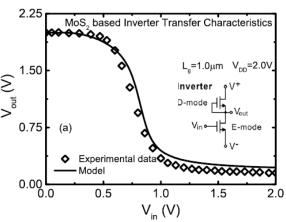

## Modeling of TMD transistor

- 2D density of state

- Fermi–Dirac statistics

- Trapping effects

C. Yadav et. al. "Compact Modeling of Transition Metal Dichalcogenide based Thin body Transistors and Circuit Validation", IEEE TED, March 2017.

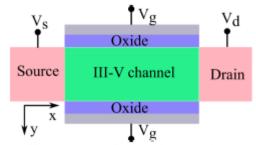

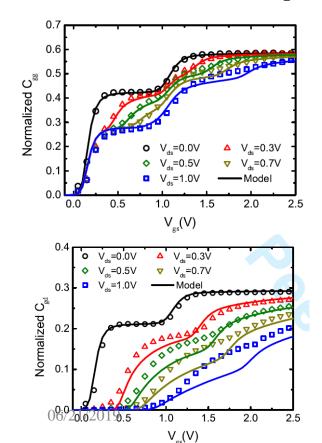

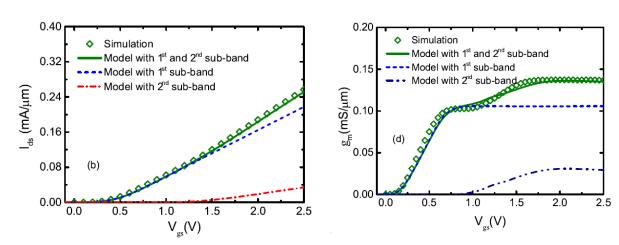

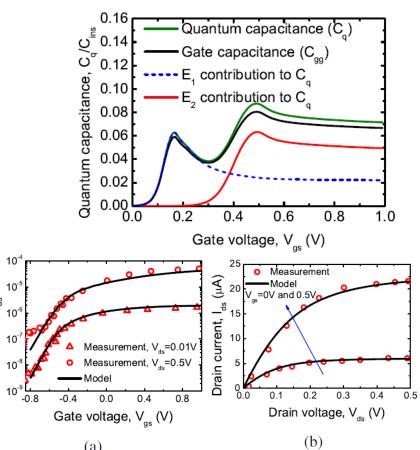

#### Modeling of III-V Channel DG-FETs

- Conduction band nonparabolicity

- 2-D density of states

- Quantum capacitance in low DOS materials

- Contribution of multiple subbands

Fig. 1. Schematic of III-V channel double-gate field effect transistor (DGFET) used in the study where V<sub>g</sub>, V<sub>d</sub> and V<sub>s</sub> denotes the applied voltage at gate, drain and source terminals, respectively.

C. Yadav et. al., Compact Modeling of Charge, Capacitance, and Drain Current in III-V Channel Double Gate FETs, IEEE TNANO, 2017.

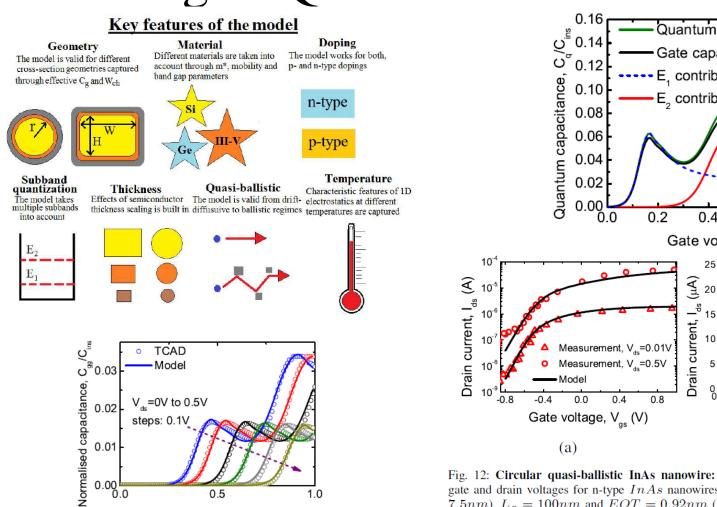

#### Modeling of Quasi-ballistic Nanowire FETs

Fig. 12: Circular quasi-ballistic InAs nanowire: Drain current as a function of the gate and drain voltages for n-type InAs nanowires, with a circular cross-section (r =7.5nm),  $L_q = 100nm$  and EOT = 0.92nm (Device 5)[44], are shown in (a) and (b) respectively. Device works in the quasi-ballistic regime. Relevant parameter values are specified in Table II. Short channel effect related parameters have been used as in

A. Dasgupta et al., "An Improved Model for Quasi-Ballistic Transport in MOSFETs", IEEE TED, Jul. 2017.

Gate voltage, V<sub>gs</sub> (V)

06/21/2019

Yogesh Chauhan, IIT Kanpur

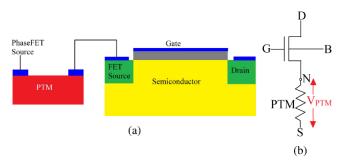

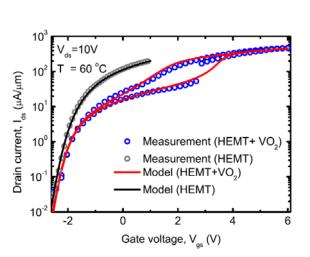

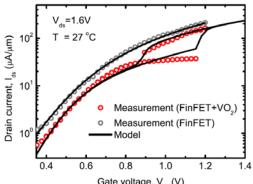

## IMT PhaseFET Including Hysteresis and Multidomain Switching

Fig. 1. (a) Graphical representation of a PhaseFET with an insulator—metal PTM at the source. (b) Schematic of a PhaseFET used for the simulations in this paper [4], [8], [9].

Fig. 2. Experimental data (symbols) and the model results (solid black) showing the variation of the resistance with temperature for a  $\rm VO_2$  resistor of  $\rm 20^{2}\mu m$  length and  $\rm 100^{2}\mu m$  width in log and linear (inset) scales [17]. The behavior smoothly changes from semiconductorlike to metallic with increasing temperature. Prediction from a single-domain-based numerical simulation (dotted blue), which shows sharp switching and no hysteresis, as suggested by the Landau theory [19], [20]. Our multidomain model is able to match the measurement, including the hysteresis, with a good accuracy.

A. Dasgupta, A. Verma, and Y. S. Chauhan, "Analysis and Compact" Modeling of Insulator-Metal-Transition Material based PhaseFET Including Hysteresis and Multi-domain Switching", IEEE TED, Jan. 2019.

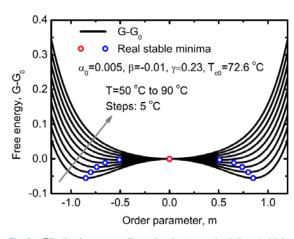

Fig. 3. Effective free energy illustrating the two real solutions to (1) in the form of the two stable minima (blue symbols) at low temperatures. With increasing temperature, the system exhibits only one stable minima (red symbol), giving rise to a switching behavior as shown in Fig. 2.

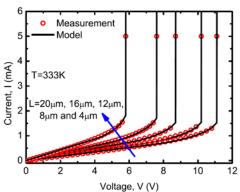

Fig. 6. Experimental data along with model prediction for I–IV characteristics of 100- $\mu$ m wide  $VO_2$  resistors of different lengths, such as L=20, 16, 12, 8, and 4  $\mu$ m, at T=60 °C [17]. The self-heating model captures the variation of device temperature with applied voltage and current flow, enabling accurate modeling of the device behavior. Parameter values are listed in Table I

15

## FinFET Modeling for IC Simulation and Design: Using the BSIM-CMG Standard

## FinFET Modeling for IC Simulation & Design

**Using the BSIM-CMG Standard**

Yogesh Singh Chauhan

Darsen Lu

Sriramkumar Venugopalan

Sourabh Khandelwal

Juan Pablo Duarte

Navid Paydavosi

Ali Niknejad

Chenming Hu

#### **Chapters**

- 1. FinFET- from Device Concept to Standard Compact Model

- 2. Analog/RF behavior of FinFET

- 3. Core Model for FinFETs

- 4. Channel Current and Real Device Effects

- 5. Leakage Currents

- 6. Charge, Capacitance and Non-Quasi-Static Effect

- 7. Parasitic Resistances and Capacitances

- 8. Noise

- 9. Junction Diode Current and Capacitance

- 10. Benchmark tests for Compact Models

- 11. BSIM-CMG Model Parameter Extraction

- 12. Temperature Effects

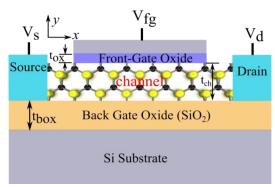

## Industry Standard FDSOI Compact Model BSIM-IMG for IC Design

#### **Chapters**

- 1. Fully Depleted Silicon on Oxide Transistor and Compact Model

- 2. Core Model for Independent Multigate MOSFETs

- 3. Channel Current Model With Real Device Effects in BSIM-IMG

- 4. Leakage Current and Thermal Effects

- 5. Model for Terminal Charges and Capacitances in BSIM-IMG

- 6. Parameter Extraction With BSIM-IMG Compact Model

- 7. Testing BSIM-IMG Model Quality

- 8. High-Frequency and Noise Models in BSIM-IMG

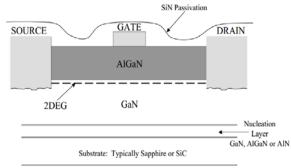

#### News (March 2018)

- Our <u>ASM-GaN-HEMT Model</u> is world's first industry standard SPICE Model for GaN HEMTs

- Download http://iitk.ac.in/asm/

Si2 Approves IC Design Simulation Standards for Gallium Nitride Devices

March 14, 2018 / 0 Comments / in Compact Model, Frontpage /

Si2 Approves Two IC Design Simulation Standards for Fast-Growing Gallium Nitride Market

Compact Model Coalition Models Expected to Reduce Costs, Speed Time-to-Market

http://www.si2.org/cmc/

http://www.si2.org/2018/03/14/gallium-nitride-models/ 06/21/2019 Yogesh Chauhan, IIT Kanpur

#### Outline

- Motivation

- Understanding Negative Capacitance

- Experimental realization of Negative Capacitance

- NCFETs: Modeling and Analysis

- MFIS vs MFMIS configurations

- Long Channel

- Short Channel

- Performance of NCFET based Circuits

- Conclusion

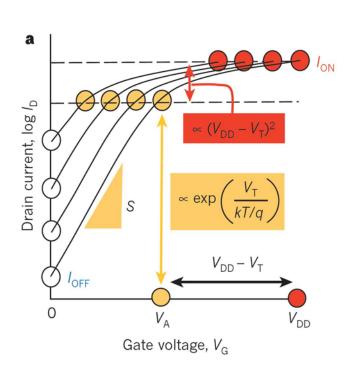

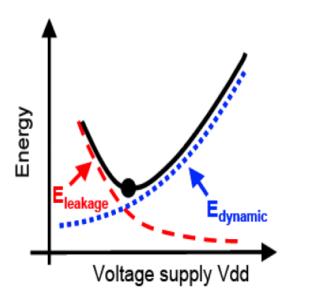

#### Power challenge

Scaling both the  $V_{\rm DD}$  and  $V_{\rm T}$  maintains same performance ( $I_{\rm ON}$ ) by keeping the overdrive ( $V_{\rm DD}$  -  $V_{\rm T}$ ) constant.

A.M. Ionescu, H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches", *Nature* 479, 329 (2011)

$$I_{ON} = \mu \frac{W}{L} C_{ox} (V_{DD} - V_{TH})^2$$

$$I_{OFF} \propto 10^{\left(\frac{-V_{TH}}{SS}\right)}$$

$$P = C_L V_{DD}^2 \alpha f + I_{leakage} V_{DD} + P_{SC}$$

A. M. Ionescu, Kathy Boucart, "Tunnel FET or Ferroelectric FET to achieve a sub-60mV/decade switch", *IEDM 2009*.

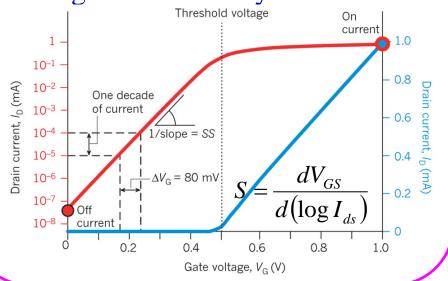

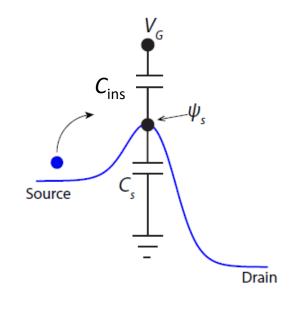

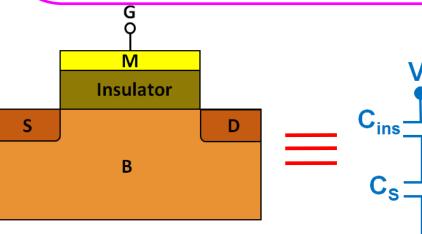

### Subthreshold Swing

$$S = \frac{\partial V_G}{\partial \log_{10} I_D} = \frac{\partial V_G}{\partial \psi_S} \frac{\partial \psi_S}{\partial \log_{10} I_D}$$

$$= \left(1 + \frac{C_S}{C_{ins}}\right) \cdot 60 \text{mV/decade}$$

As  $1 + \frac{C_S}{C_{ins}} \ge 1$ ,  $S \ge 60mV/decade$

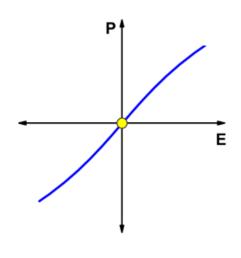

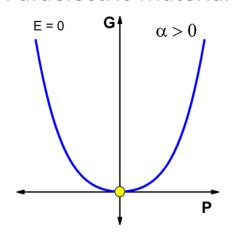

#### Capacitance Definition

- In general, insulator can be a non-linear dielectric whose capacitance density (per unit volume) can be defined as

- 1:  $C_{ins} = \left(\frac{\partial^2 G}{\partial P^2}\right)^{-1}$  = inverse curvature of free energy density 2:  $C_{ins} = \frac{\partial P}{\partial E}$  = slope of the polarization vs electric field curve

P = Polarization in dielectric, G = Free energy density, E = Externally applied electric field

- Two types of non-linear dielectrics:

- Paraelectric: No polarization when electric field is removed.

- Ferroelectric: Two possible states of polarization when electric field is removed.

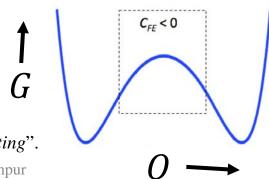

## Negative Capacitance Transistor

What if insulator has a Negative Capacitance!

$$C_{ins} < 0$$

and  $\frac{C_S}{C_{ins}} < 0$ , then  $\left(1 + \frac{C_S}{C_{ins}}\right) < 1 \rightarrow S < 60 \text{mV/decade}$

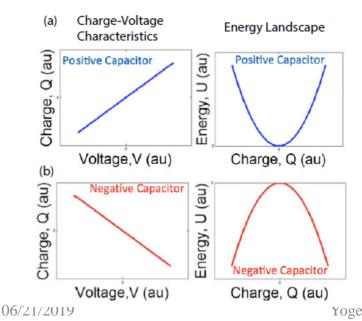

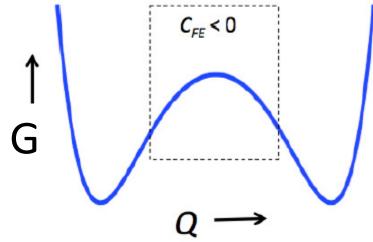

For a capacitor

- Energy

$$G = \frac{Q^2}{2C}$$

- Capacitance  $C = \frac{1}{\sqrt{\frac{d^2G}{dO^2}}} = \frac{1}{Curvature}$

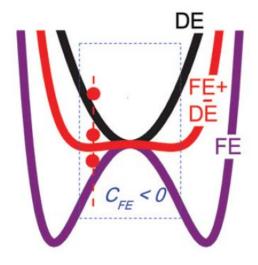

Energy landscape of ferroelectric

Yogesh Chauhan, IIT Kanpur s. 2008. materials.

$Q = \epsilon E + P \cong P$

Ref. - S. Salahuddin et. al., Nano Letters, 2008.

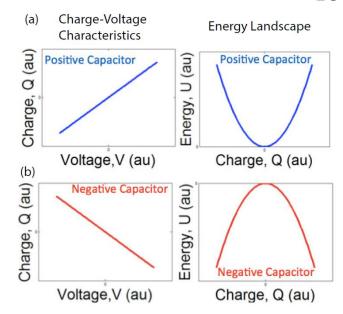

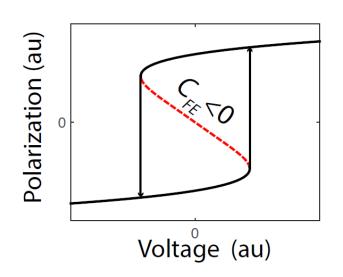

#### Capacitance Definition

#### **Charge-Voltage Relation**

$$C = \frac{dQ}{dV}$$

If  $C < 0 \rightarrow As V \downarrow$ , Q \(\Delta\)

#### **More Definitions**

Capacitance of a general dielectric:

$$C = \left(\frac{\partial^2 G}{\partial Q^2}\right)^{-1}$$

Inverse curvature of free energy density

G = Free energy density

Linear capacitor: Parabolic,  $G=rac{Q^2}{2C}$

#### Non-linear capacitor: e.g. Ferroelectric

Ref. - A.I. Khan, "Negative Capacitance for Ultra-low Power Computing". PhD(thesiso) University of California at Berkeley 2015. Chauhan, IIT Kanpur

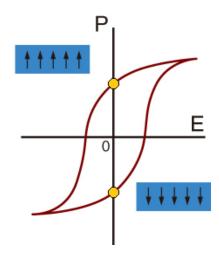

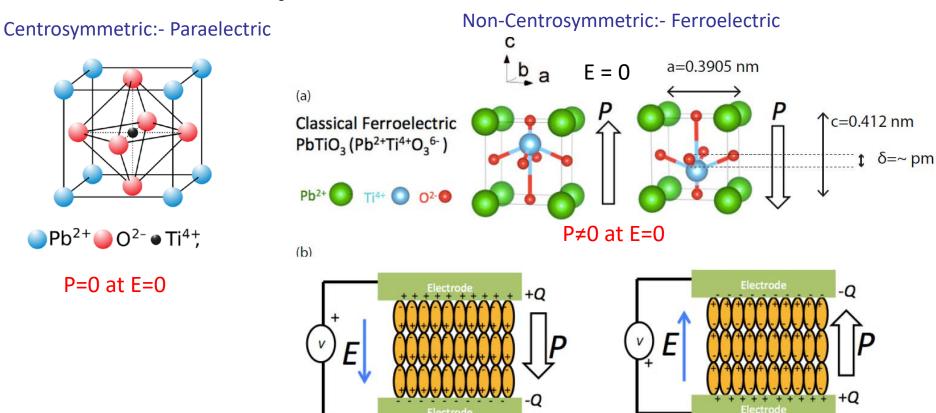

#### Para- and Ferro-electric Materials

•Paraelectric: No polarization when electric field is removed.

•Ferroelectric: Two possible states of polarization when electric field is removed —Spontaneous/Remnant Polarization.

**Paraelectric**

Ferroelectric

#### Ferroelectricity

#### Requirements:

- Spontaneous electric polarization: Non-Centrosymmetricity (for crystalline materials)

- Reversible polarization state by the application of electric field

e.g. Lead titanate PbTiO<sub>3</sub>, HZO

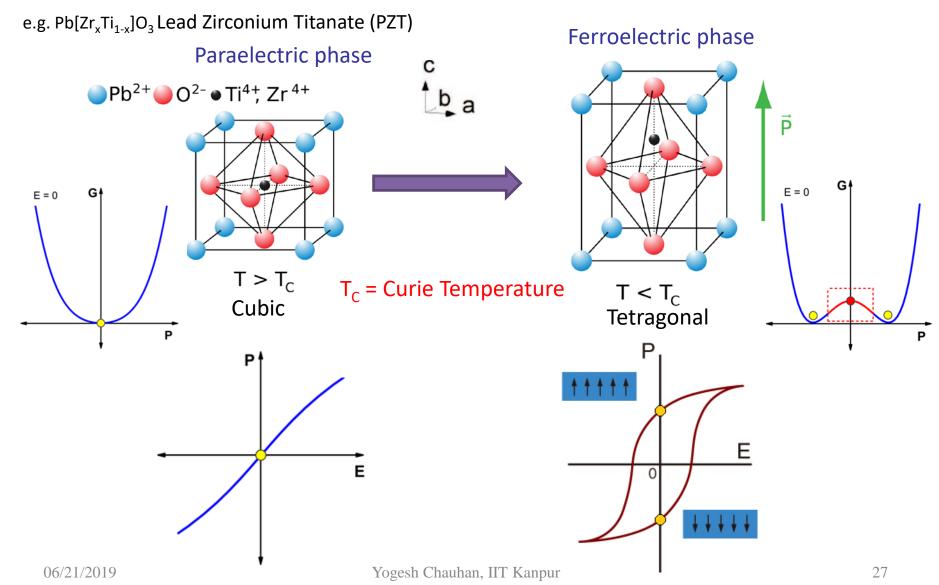

#### Paraelectric to Ferroelectric Phase Transition

[1] K. M. Rabe, C. H. Ahn, and J.-M. Triscone, Eds., *Physics of Ferroelectrics: A Modern Perspective*, vol. 105. Berlin, Germany: Springer, 2007.

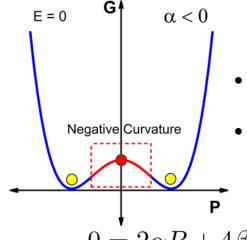

#### Landau-Khalatnikov Theory of Non-Linear Dielectrics

• Free energy of a non-linear dielectric is given as

$$G = \alpha P^2 + \beta P^4 + \gamma P^6 - EP$$

- In general,  $\alpha$  and  $\beta$  can be +ve or –ve but  $\gamma$  is always +ve for stability reasons.

- Dynamics of G is given by  $\delta \frac{dP}{dt} = -\frac{\partial G}{\partial P}$

$\delta$  = Polarization damping factor

• In the steady state,  $\frac{dP}{dt} = 0 \rightarrow E = 2\alpha P + 4\beta P^3 + 6\gamma P^5$

For  $\alpha > 0$  and at E = 0, there exit only one real root P = 0

A Paraelectric Material

For  $\alpha < 0$  and at E = 0, there exit three real roots

$$P=0,\pm P_r$$

where  $P_r=\sqrt{\frac{\sqrt{\beta^2-3\alpha\gamma}-\beta}{3\gamma}}$

A Ferroelectric Material has a non-zero P at zero E.

#### Assumptions

Free energy of a non-linear dielectric

$$G = \alpha P^2 + \beta P^4 + \gamma P^6 - EP$$

- Polarization and Electric field are uniaxial.

(perpendicular to electrodes)

- Polarization and Electric field magnitudes are uniform throughout the ferroelectric.

- Piezo-electricity is ignored.

#### L-K explanation of Phase Transition

For E = 0,

$$G = \alpha P^2 + \beta P^4 + \gamma P^6$$

and  $\alpha = \alpha_0 (T - T_0), \alpha_0 > 0$

#### Paraelectric Material

$$0 = 2\alpha P + 4\beta P^3 + 6\gamma P^5$$

- $\alpha > 0$  i.e. for T > T<sub>0</sub>; at E = 0, there exists only one real root, P = 0

- i.e. No polarization when electric field is removed

$$[P = 0 \text{ at } E = 0]$$

#### Ferroelectric Material

- Note, P = 0 has a maximum.

- Not possible in an isolated ferroelectric.

$$0 = 2\alpha P + 4\beta P^3 + 6\gamma P^5$$

•  $\alpha < 0$  i.e. for T < T<sub>0</sub>; at E = 0, there exist three real roots

$$P=0,\pm P_r$$

where

$$P_r = \sqrt{\frac{\sqrt{\beta^2 - 3\alpha\gamma} - \beta}{3\gamma}}$$

Two possible states of polarization when electric field is removed.

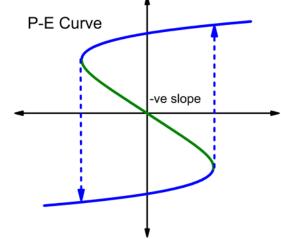

## Positive and Negative Capacitances

Only one solution

at E = 0

**Paraelectric**

A Positive Capacitor

Three possible solutions at E = 0

P = 0 is not possible in a isolated Ferroelectric due to maxima of energy or a negative capacitance

Negative Slope

$$C_{ins} = \left(\frac{\partial^2 G}{\partial P^2}\right)^{-1} = \frac{\partial P}{\partial E} < 0$$

**Ferroelectric**

A Conditionally Negative Capacitor Yogesh Chauhan, IIT Kanpur

#### Application of Electric Field

$$G = \alpha P^2 + \beta P^4 + \gamma P^6 - EP$$

$$E = 2\alpha P + 4\beta P^3 + 6\gamma P^5$$

**Paraelectric** [A Positive Capacitor]

**Isolated Ferroelectric**

[A Conditionally Negative Capacitor]

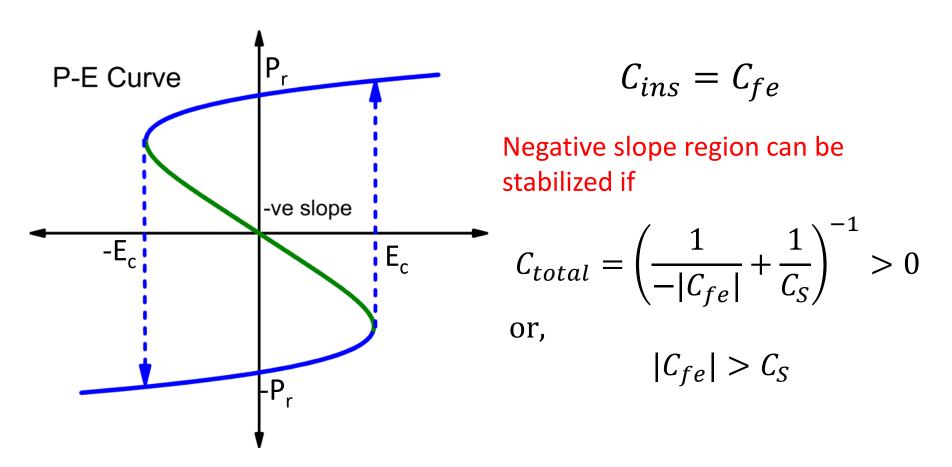

#### How to stabilize a Negative Capacitance?

Add a positive dielectric capacitance in series such that total free energy of system has a minima in the negative capacitance regime of ferroelectric.

Total energy of the FE + DE system

$$G = G_f + G_d$$

$$Q = \epsilon_0 E_f + P_f = \epsilon_0 E_d + P_d$$

For a stable system

$$\frac{\partial^2 G}{\partial Q^2} > 0$$

(minimum)

Assuming V is small

$$Q \approx P_f \approx P_d$$

$$\Longrightarrow \frac{\partial^2 G}{\partial Q^2} = \frac{\partial^2 G_f}{\partial Q^2} + \frac{\partial^2 G_d}{\partial Q^2}$$

$$\implies \frac{1}{C_{tot}} = \frac{1}{C_f} + \frac{1}{C_d} > 0$$

$$C_{tot} = \frac{C_d \cdot |C_f|}{|C_f| - C_d} > 0$$

Yogesh Chauhan, HT Kanpur  $C_d$

For a stable system

$$|C_f| > C_d$$

$$C_{tot} > C_d$$

#### Negative Capacitance in Ferroelectric

S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," Nano Letters, vol. 8, no. 2, pp. 405–410, 2008.

#### How to stabilize a Negative Capacitance?

• Add a positive dielectric capacitance in series such that total free energy of system has a minima in the negative capacitance regime of ferroelectric.

A. I. Khan et al., APL, vol. 99, no. 11, p. 113501, 2011

$$\bullet \quad \frac{1}{C_{tot}} = \frac{1}{C_{FE}} + \frac{1}{C_{DE}} > 0$$

•

$$C_{DE} < |C_{FE}|$$

and  $C_{FE} < 0$

•

$$C_{tot} = \frac{C_{DE} \cdot |C_{FE}|}{|C_{FE}| - C_{DE}} > 0$$

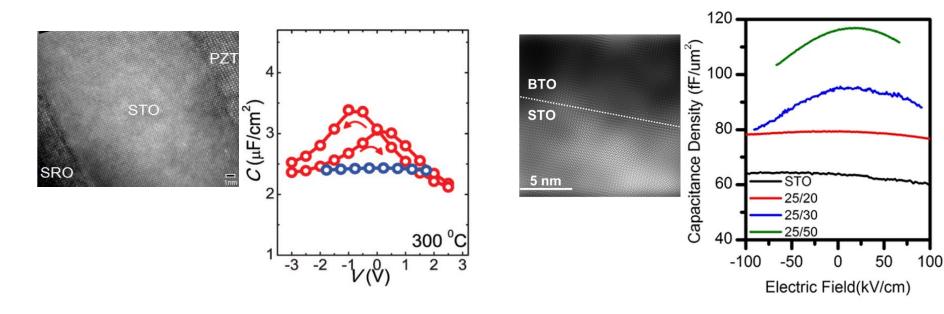

### Ferroelectric-Dielectric Systems

A. I. Khan et al., APL, vol. 99, no. 11, p. 113501, 2011.

D. J. Appleby et al., Nano Letters, vol. 14, no.7, pp. 3864–3868, 2014.

Total Capacitance of Ferroelectric-dielectric hetro-structure becomes greater than the dielectric capacitance.

$$C_{tot} = \frac{C_{DE}. |C_{FE}|}{|C_{FE}| - C_{DE}} > 0$$

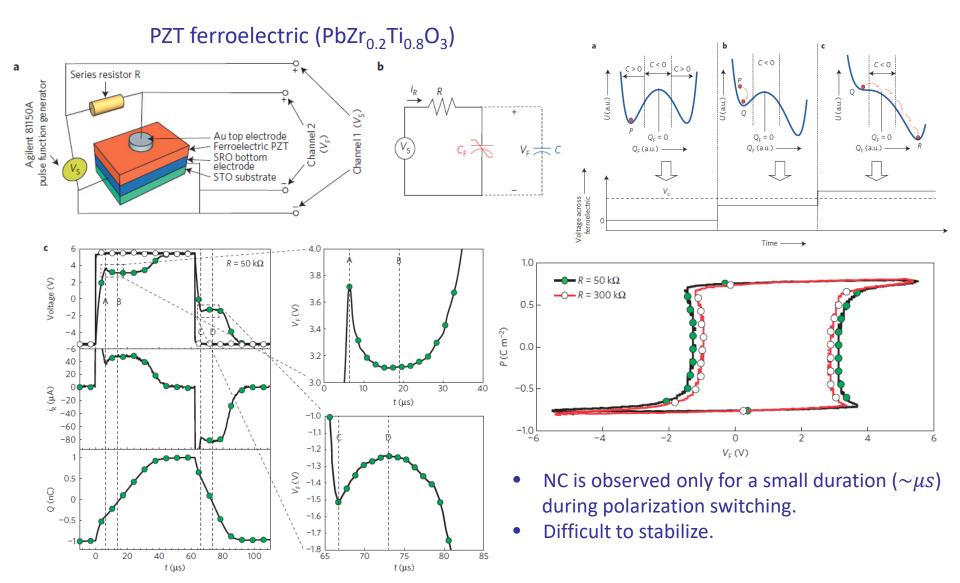

# Ferroelectric-Resistor System

A<sub>6</sub>L Khan et al., "Negative capacitance in a ferroelectric capacitor," Nature Mater., vol. 14, no. 2, pp. 182–186, 2015.

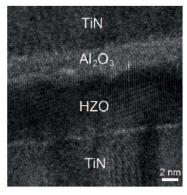

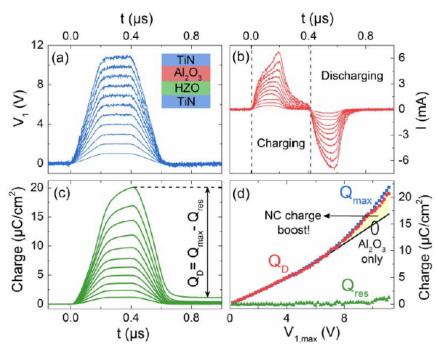

## First ever demonstration of S-curve

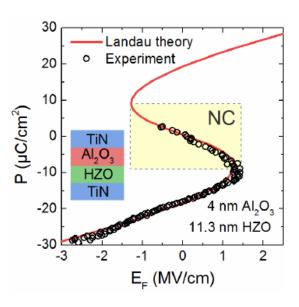

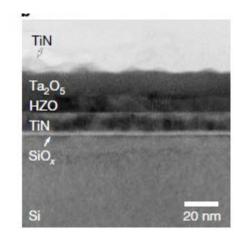

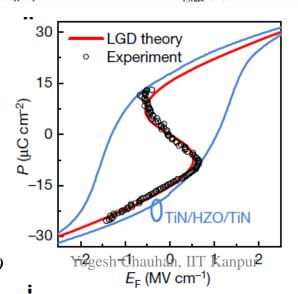

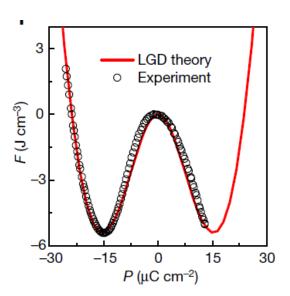

Hoffmann et al. *IEDM*, Dec 2018

Hoffmann et al. Nature Lett., Jan 2019

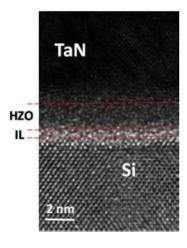

Measuring S-Curve a Experimental set-up 15 V(t)Pulse gen. Charge (nC) 8.0 €<sup>10</sup> Ta<sub>2</sub>O<sub>5</sub> HZO TIN Si 0.0 0.5 1.0  $V_{\text{max}}$  (V) Time (µs) LGD theory Experiment P (µC cm<sup>-2</sup>) / (mA) b TiN -10 -2 -1 0.0 0.5 1.0  $E_{\rm F}$  (MV cm<sup>-1</sup>) Time (µs) Ta<sub>2</sub>O<sub>5</sub> **HZO** 3 2.4 LGD theory Experiment TiN F (J cm<sup>-3</sup>) Charge (nC) 8.0 SiO.

Ref. – Thomas Mikolajick et al., "Unveiling the double-well energy landscape in a ferroelectric layer", Nature, Jan. 2019.

0.5

0.0

0.0

20 nm

0 P (μC cm<sup>-2</sup>)

30

-15

-30

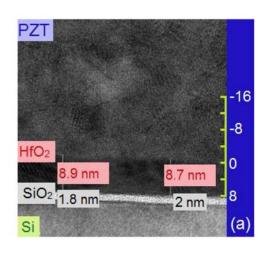

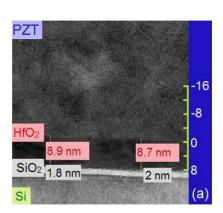

# Negative Capacitance FETs

PbZr<sub>0.52</sub>Ti<sub>0.48</sub>O3 FE with HfO<sub>2</sub> buffer interlayer

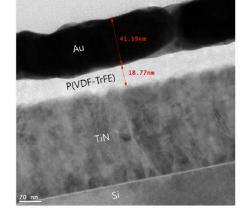

P(VDF<sub>0.75</sub>-TrFE<sub>0.25</sub>) Organic Polymer FE

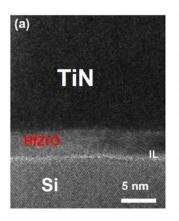

HfZrO FE CMOS compatible FE

S. Dasgupta et al., IEEE JESCDC, 2015.

J. Jo et al., Nano Letters, 2015

K.-S. Li et al., in IEEE IEDM, 2015.

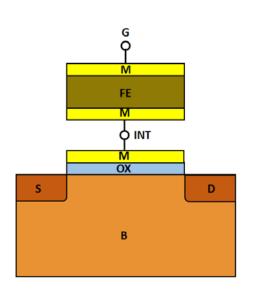

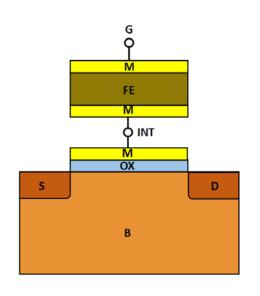

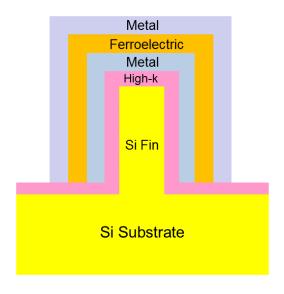

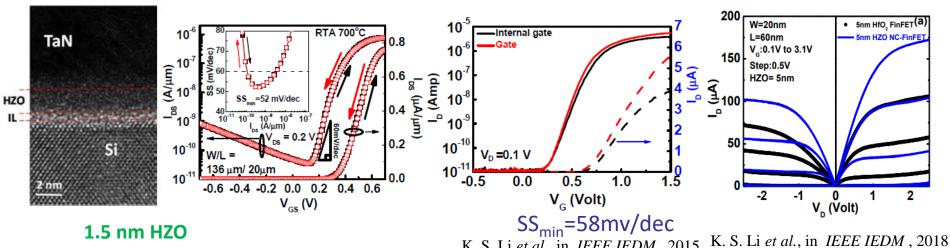

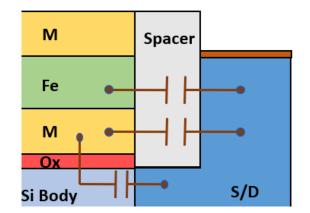

# NCFET Structures

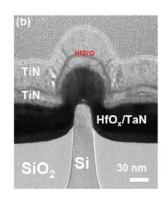

#### **MFMIS Structure**

Metal

Ferroelectric

Metal

Insulator

Semiconductor

NC-FinFET (FE:  $Hf_{0.42}Zr_{0.58}O_2$ ) Lg = 30 nm [Li et al. IEDM '15]

46 mV/decade [Rusu et al. IEDM '10] 06/21/2019

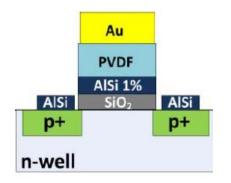

#### **MFIS Structure**

Metal

Ferroelectric

Insulator

Semiconductor

13 mV/decade Lg = 10 μm [Dasgupta et al., IEEE JESCDC, '15]

$\begin{array}{c} 52 \text{ mV/decade} \\ \textbf{t}_{\text{fe}} = \textbf{1.5 nm} \\ \text{[Lee et al., IEDM '16]} \end{array}$

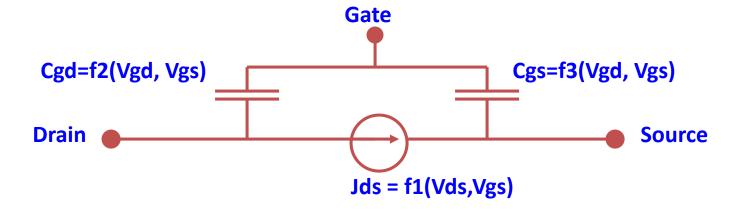

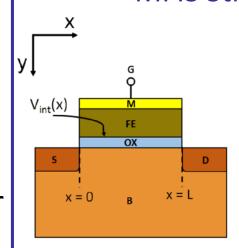

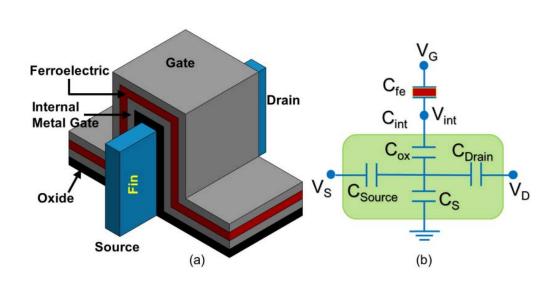

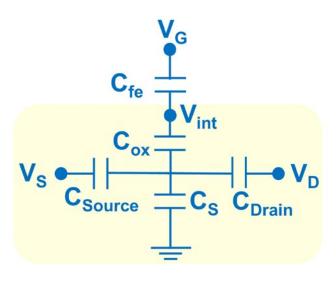

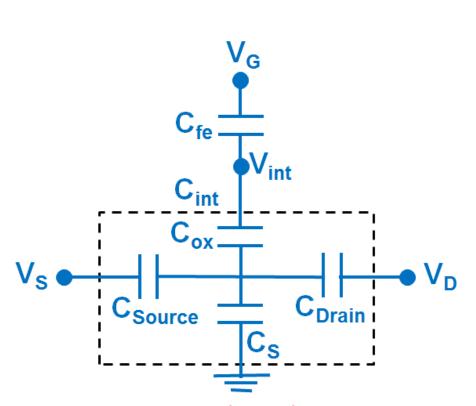

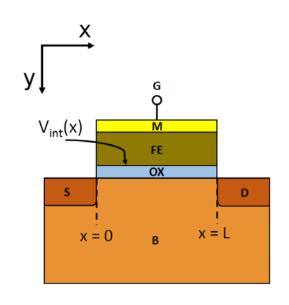

# MFMIS NCFET Modeling

#### **MFMIS Structures**

- Metal internal gate  $\rightarrow$  equipotential surface with a spatially constant  $V_{\text{int}}$ .

- Ferroelectric and baseline MOSFET can be considered as two separate circuit entities connected by a wire

Simplified modeling

### Device Structure

Metal-ferroelectric-Metal-Insulator-Semiconductor (MFMIS)

- Metal internal gate provides an equipotential surface with a spatially constant  $V_{int}$ .

- Simplifies modeling as ferroelectric and baseline MOSFET can be considered as two separate circuit entities connected by a wire.

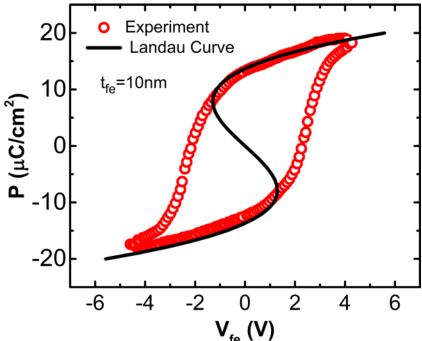

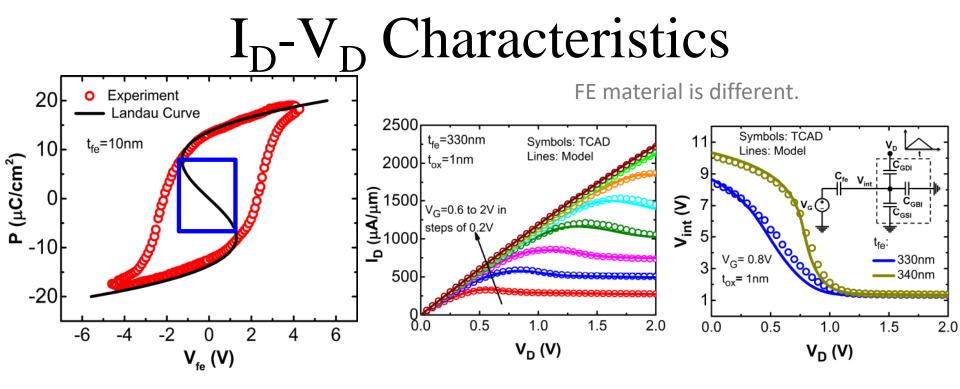

## Experimental Calibration of L-K Model

Calibration of L-K with P-V<sub>fe</sub> curve for Y-HfO2 with 3.6 mol% content of  $YO_{1.5}[3]$

$$\alpha = -1.23 \times 10^9 \text{ m/F}$$

$$\beta = 3.28 \times 10^{10} \text{ m/F}$$

$$\gamma = 0 \text{ (2}^{\text{nd}} \text{ order phase transition)}$$

Gibb's Energy,

$$G = \alpha P^2 + \beta P^4 + \gamma P^6 - EP$$

Dynamics of G is given by

$$\delta \frac{dP}{dt} = -\frac{\partial G}{\partial P}$$

In the steady state,  $\frac{dP}{dt} = 0$

$$E = \frac{V_{fe}}{t_{fe}} = 2\alpha P + 4\beta P^{3} + 6\gamma P^{5}$$

$$P = Q - \varepsilon E \approx Q \text{ (Gate Charge)}$$

[1] Devonshire et al., The London, Edinburgh, and Dublin Philosophical Magazine and Journal of Science, vol. 40, no. 309, pp. 1040-1063, 1949.

[2] Landau, L. D. & Khalatnikov, I. M. On the anomalous absorption of sound near a second order phase transition point. Dokl. Akad. Nauk 96, 469472 (1954).

[3] J. M"uller et al., JAP, vol. 110, no. 11, pp. 114113, 2011.

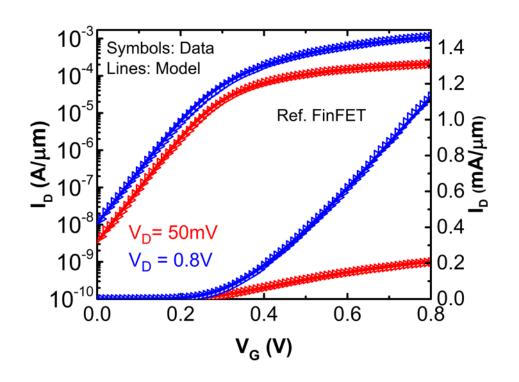

## Calibration of Baseline FinFET

Calibration of baseline FinFET with 22 nm node FinFET.

BSIM-CMG model is used to model baseline FinFET.

Gate length (L) = 30nm, Fin height (Hfin) = 34nm Fin thickness (Tfin) = 8nm

C. Auth et al., in VLSIT, 2012, pp. 131-132.

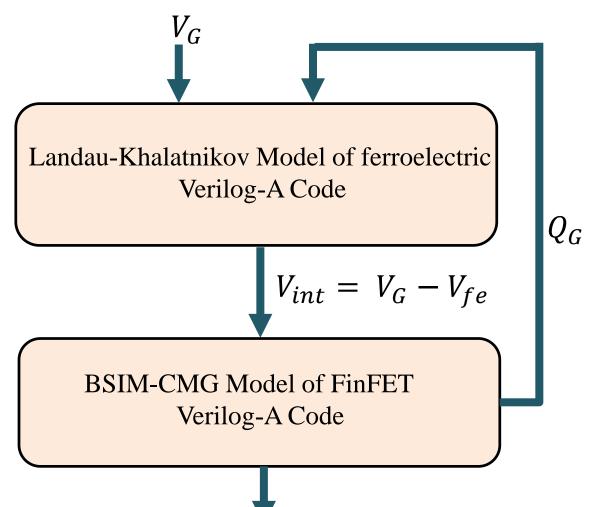

# Complete Modeling Flowchart

$$E = \frac{V_{fe}}{t_{fe}} = 2\alpha P + 4\beta P^{3} + 6\gamma P^{5}$$

$$P = Q - \varepsilon E \approx Q \text{ (Gate Charge)}$$

06/21/2019

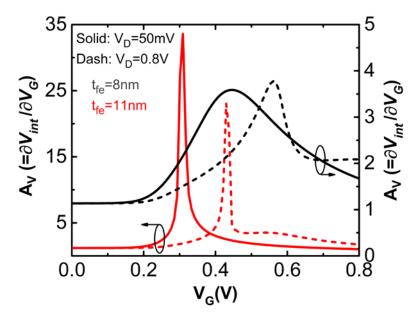

## Capacitances and Voltage Amplification

Capacitance matching between  $|C_{fe}|$  and  $C_{int}$  increases the gain.

$$E = \frac{V_{fe}}{t_{fe}} = 2\alpha P + 4\beta P^{3} + 6\gamma P^{5}$$

$$V_{fe} = t_{fe}(2\alpha P + 4\beta P^{3} + 6\gamma P^{5})$$

$$C_{fe} = \frac{\partial Q}{\partial V_{fe}} = \frac{1}{t_{fe}(2\alpha + 12\beta Q^{2} + 30\gamma Q^{4})}$$

$$\frac{1}{C_{int}} = \frac{1}{C_{ox}} + \frac{1}{C_{S} + C_{Drain} + C_{Source}}$$

Internal Voltage Gain,

$$A_V = \frac{\partial V_{int}}{\partial V_G} = \frac{|C_{fe}|}{|C_{fe}| - C_{int}}$$

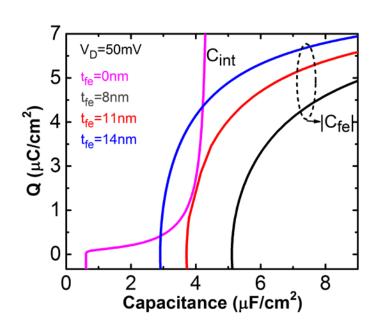

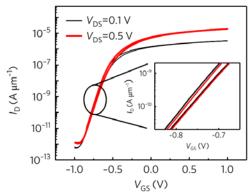

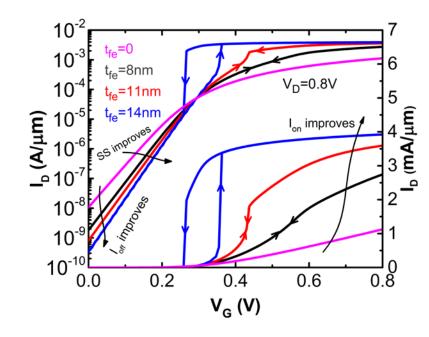

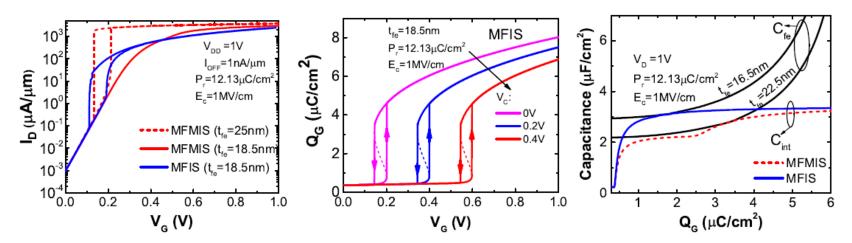

# Capacitance Matching

- Capacitance matching increases with  $t_{fe}$  which increases the gain.

- Hysteresis appears for  $|C_{fe}|$  < Cint which is region of instability.

- Increase in V<sub>D</sub> reduces the capacitance matching

- Reduces gain.

- Reduces width of hysteresis window.

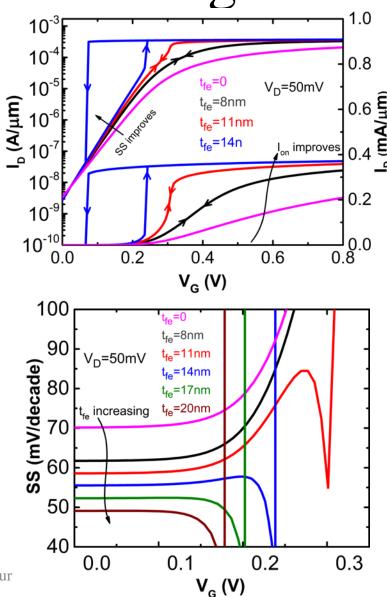

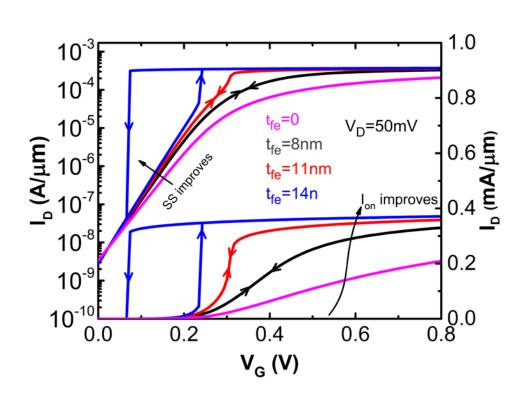

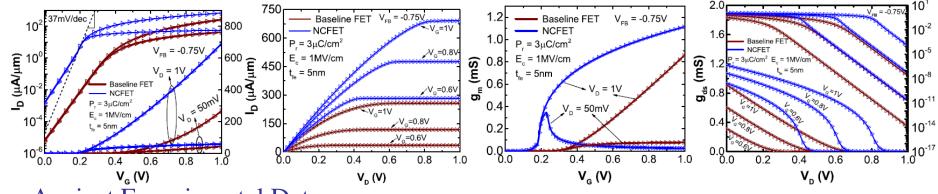

# I<sub>D</sub>-V<sub>G</sub> Characteristics – SS region

- As t<sub>fe</sub> increases

- Capacitance matching is better

- C<sub>S</sub> and C<sub>ins</sub> are better matched

$$S = \left(1 - \frac{c_S}{|c_{ins}|}\right).60 \text{mV/dec}$$

• As  $t_{fe} \uparrow \rightarrow SS \downarrow$

# I<sub>D</sub>-V<sub>G</sub> Characteristics – ON region

- As t<sub>fe</sub> increases

- Capacitance matching is better

$$A_{V} = \frac{\partial V_{int}}{\partial V_{G}} = \frac{|C_{fe}|}{|C_{fe}| - C_{int}}$$

As gain increases, I<sub>ON</sub> increases.

Note the significant improvement in  $I_{ON}$  compared to SS.

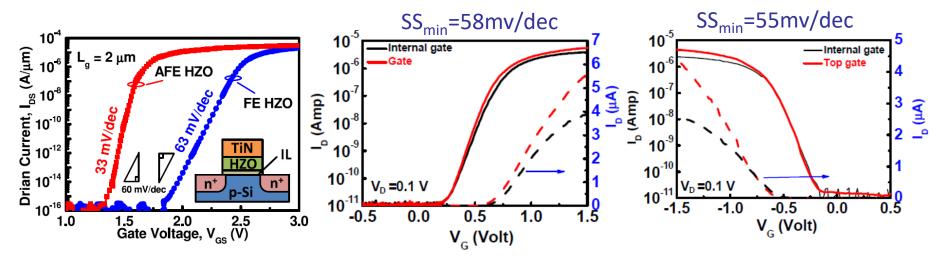

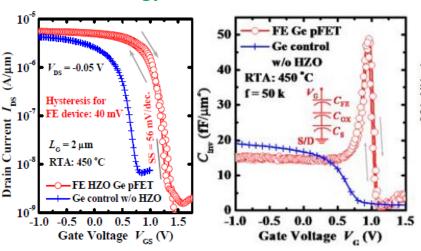

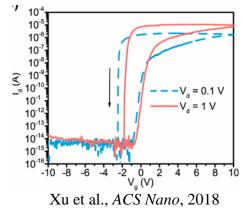

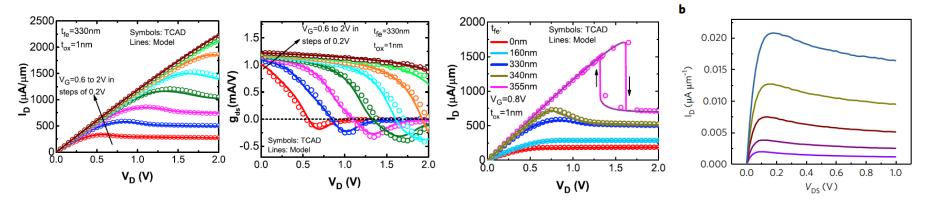

# I<sub>D</sub>-V<sub>G</sub> Experimental Demonstration

M. H. Lee et al., in IEEE JEDS, July 2015.

K. S. Li et al., in IEEE IEDM, 2015

J. Zhou et al., in IEEE IEDM, 2016.

D. Kwon et al., in IEEE EDL, 2018

Jing Li et al., in IEEE EDL, 2018

- NCFET is biased in negative capacitance region.

- $Q_G$  or P is positive  $\rightarrow V_{fe}$  is negative.

- $V_{DS} \uparrow \rightarrow Q_G \text{ or } P \downarrow \rightarrow |V_{fe}| \downarrow \rightarrow V_{int} = V_G + |V_{fe}| \downarrow \rightarrow A_V \downarrow \rightarrow Current reduces$

G. Pahwa, ..., Y. S. Chauhan, "Analysis and Compact Modeling of Negative Capacitance Transistor with High ON-Current and Negative Output Differential Resistance", IEEE TED, Dec. 2016.

52

# **Experimental Demonstration**

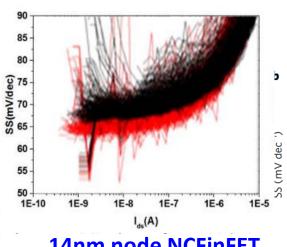

Compatible with sub-10nm technology node

12.1.1-12.1.4., 2016

J. Zhou et al., IEDM, 2016, pp. 12.2.1-12.2.4. 06/21/2019

M. H. Lee et al, IEDM, pp.

K. S. Li et al., in IEEE IEDM, 2015

14nm node NCFinFET by Global Foundries

Krivokapic et al., IEDM, 2017, pp. 15.1.1-

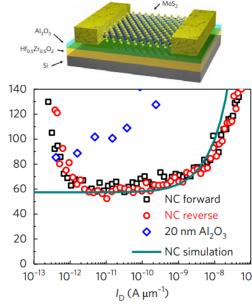

M. Si et al., Nature Nanotechnol.,

vol. 13, pp. 24–28, 2018.

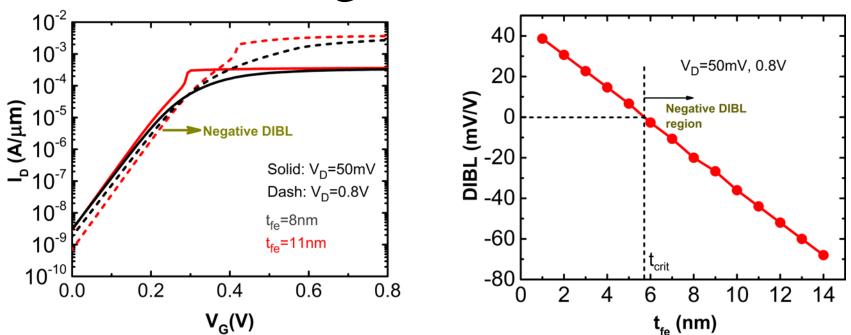

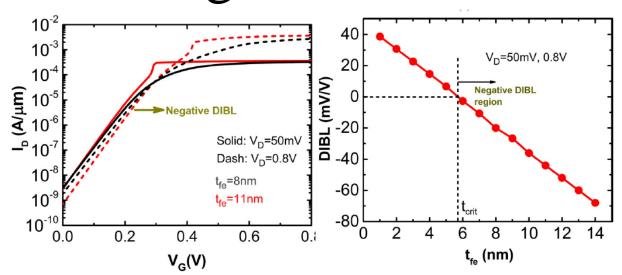

# Negative DIBL

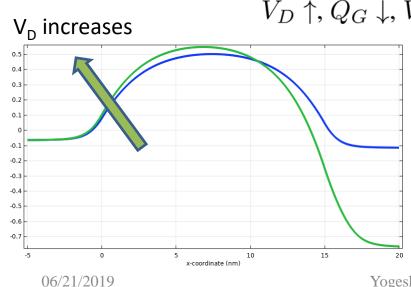

- $V_D$  reduces  $Q_G$  which, in turn reduces  $V_{int} = V_G V_{fe}$  in the negative capacitance region.

- Negative DIBL increases with  $t_{fe}$  due to increased  $V_{fe}$  drop.

- V<sub>th</sub> increases with V<sub>D</sub> instead of decreasing.

- Higher I<sub>ON</sub> still lower I<sub>OFF</sub>!

# Negative DIBL/DIBR Effect

G. Pahwa et al., IEEE Eur. Solid-State Device Res. Conf. (ESSDERC), Sep. 2016, pp. 41-46.

$V_D \uparrow, Q_G \downarrow, V_{fe} \uparrow, V_{int} \downarrow, V_{th} \uparrow$

M. Si et al., *Nature Nanotechnol.*, vol. 13, pp. 24–28, 2018.

- V<sub>th</sub> increases with V<sub>D</sub> instead of decreasing. Higher I<sub>ON</sub> still lower I<sub>OFF</sub>!

- Negative DIBL increases with  $t_{fe}$  due to increased  $V_{fe}$  drop.

Yogesh Chauhan, IIT Kanpur

# I<sub>D</sub>-V<sub>G</sub> Characteristics – High V<sub>DS</sub>

- Hysteresis appears for  $|C_{fe}| < C_{int}$  which is the region of instability.

- As t<sub>fe</sub> increases

- SS reduces, I<sub>ON</sub> increases.

- I<sub>OFF</sub> reduces for high V<sub>D</sub>.

- Width of hysteresis at larger thicknesses can be controlled with V<sub>D</sub>.

# Negative Output Differential Resistance

G. Pahwa et al.," IEEE TED, Dec. 2016

Mengwei Si et al., Nature Nanotechnology, 2018

J. Zhou et al., IEEE, JEDS, 2018

J. Zhou et al., IEDM 2016

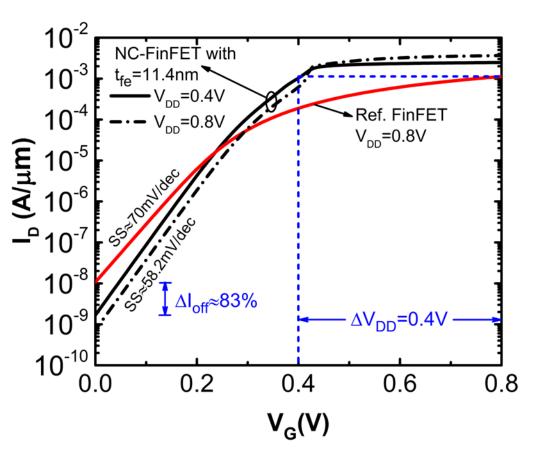

# Optimum NC-FinFET

- Same I<sub>ON</sub> as 22 nm node FinFET.

- Steeper SS of 58.2 mV/decade.

- V<sub>DD</sub> reduction by 0.4 V.

- I<sub>OFF</sub> reduction by 83 %.

G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "<u>Designing Energy Efficient and Hysteresis Free Negative Capacitance FinFET with Negative DIBL and 3.5X ION using Compact Modeling Approach</u>", IEEE European Solid-State Device Research Conference (ESSDERC), Lausanne, Switzerland, Sept. 2016. (Invited)

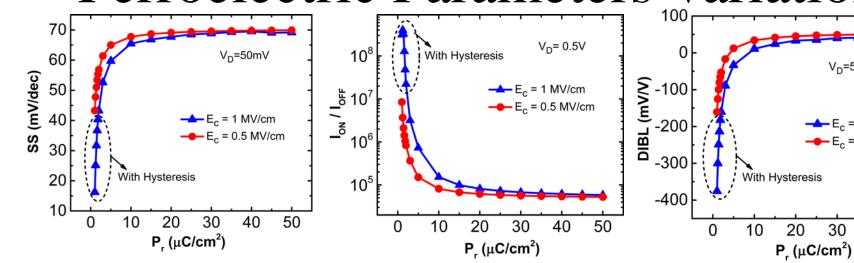

# Ferroelectric Parameters Variation

If

$$\gamma = 0$$

,

$$\alpha = -\frac{3\sqrt{3}E_c}{P_r} \quad \beta = \frac{3\sqrt{3}E_c}{P_r^3}$$

$P_r$  = Remnant Polarization

$$E_c$$

= Coercive Field

$$C_{fe} = \frac{1}{t_{fe}(2\alpha + 12\beta Q^2)}$$

#### Low P<sub>r</sub> and high E<sub>c</sub>

- reduce |C<sub>fe</sub>| which leads to improved capacitance matching and hence, a high gain.

- Low SS

- increase I<sub>ON</sub> but reduce I<sub>OFF</sub> due to a more negative DIBL  $\Rightarrow$  high  $I_{ON}/I_{OFF}$ .

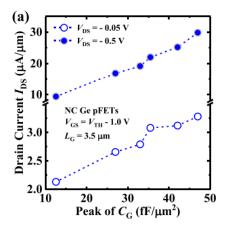

V<sub>D</sub>=50mV, 0.5V

$-E_c = 1 \text{ MV/cm}$

30

$-E_c = 0.5 \text{ MV/cm}$

40

50

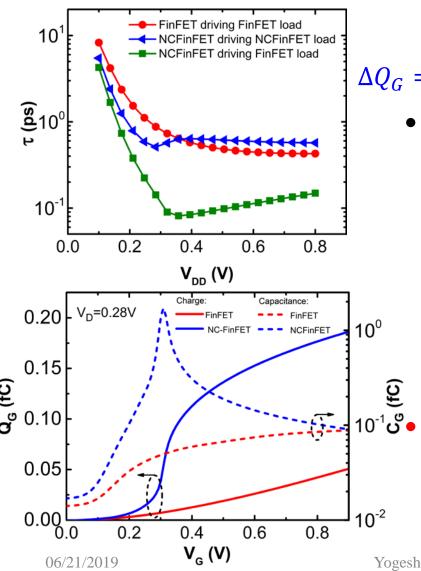

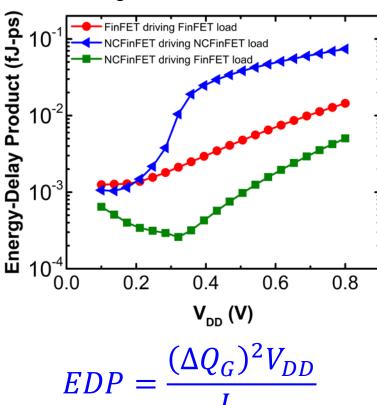

# Intrinsic Delay

Delay,

$$au=rac{\Delta Q_G}{I_{ON}}$$

$$\Delta Q_G=Q_G(V_G=V_D=V_{DD})-Q_G(V_G=0,V_D=V_{DD})$$

- NC-FinFET driving NC-FinFET

- For high  $V_{DD}$ , high  $I_{ON}$  advantage is limited by large amount of  $\Delta Q_G$  to be driven.

- Outperforms FinFET at low V<sub>DD</sub>.

- Minimum at  $V_{DD} \approx 0.28$  V corresponds to a sharp transition in  $Q_G$ .

NC-FinFET driving FinFET load provides full advantage of NC-FinFET.

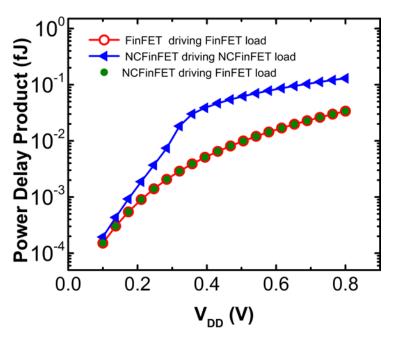

# Power and Energy Delay Products

$$PDP = \Delta Q_G. V_{DD}$$

- NC-FinFET driving NC-FinFET shows advantage only for low V<sub>DD</sub>.

- NC-FinFET driving FinFET load is the optimum choice.

# Modeling of MFIS NCFET

#### Contrast with MFIMS structure:

- P and  $V_{\text{int}}$  vary spatially in longitudinal direction

- Better stability w.r.t. Leaky ferroelectric and domain formation

### Issues with Existing Models<sup>[1,2]</sup>:

Implicit equations – tedious iterative numerical solutions

[1] H.-P. Chen, V. C. Lee, A. Ohoka, J. Xiang, and Y. Taur, "Modeling and design of ferroelectric MOSFETs," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2401–2405, Aug. 2011.

[2] D. Jiménez, E. Miranda, and A. Godoy, "Analytic model for the surface potential and drain current in negative capacitance field-effect transistors," *IEEE Trans. Electron Devices*, vol. 57, no. 10, pp. 2405–2409, Oct. 2010.

Yogesh Chauhan, IIT Kanpur

62

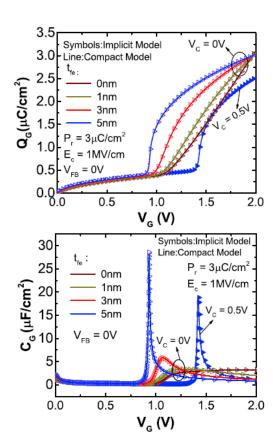

# Explicit Modeling of Charge

$$V_{\rm fe} = E t_{\rm fe} = a Q_G + b Q_G^3$$

#### Voltage Balance:

$$V_{G} - V_{FB} = V_{fe} + \frac{Q_{G}}{C_{ox}} + \psi_{S} = a_{eff} Q_{G} + bQ_{G}^{3} + \psi_{S} - Q_{G} - \psi_{S} \text{ relation}^{[1]}$$

$$Q_{G} - \psi_{S} \text{ relation}^{[1]}$$

$$Q_{G} = \text{sign}(\psi_{S}) \gamma C_{ox} \left[ \psi_{S} + V_{t}(e^{-\psi_{S}/V_{t}} - 1) + e^{-(2\phi_{F} + V_{C})/V_{t}} (V_{t}e^{\psi_{S}/V_{t}} - \psi_{S} - V_{t}) \right]^{1/2}$$

- $\rightarrow$  Implicit equation in  $Q_G$

- → Goal: Explicit Model with good initial guesses for each region of NCFET operation

Both the Q<sub>G</sub> and its derivatives match well with implicit model

G. Pahwa, T. Dutta, A. Agarwal and Y. S. Chauhan, "Compact Model for Ferroelectric Negative Capacitance Transistor With MFIS Structure," in *IEEE Transactions on Electron Devices*, March 2017.

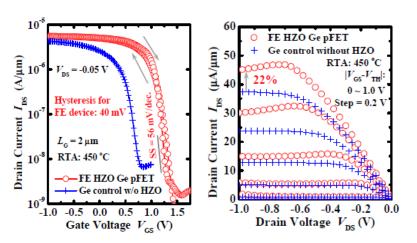

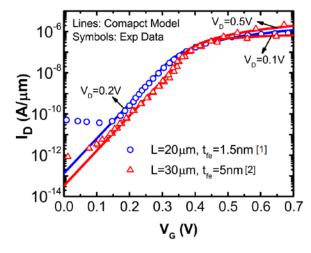

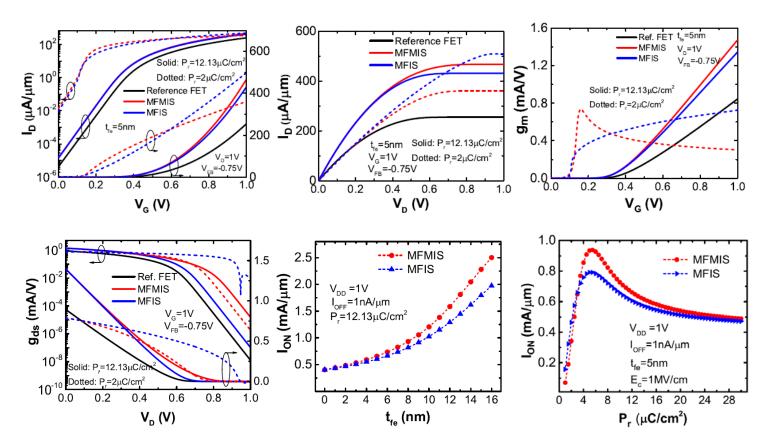

## Drain Current Model Validation

#### **Against Full Implicit Calculations**

Against Experimental Data

G. Pahwa, T. Dutta, A. Agarwal and Y. S. Chauhan, "Compact Model for Ferroelectric Negative Capacitance Transistor With MFIS Structure," *IEEE Transactions on Electron Devices*, March 2017.

[1] M. H. Lee et al., in IEDM Tech. Dig., Dec. 2016, pp. 12.1.1–12.1.4. [2] M. H. Lee et al., in IEDM Tech. Dig., Dec. 2015, pp. 22.5.1–22.5.4.

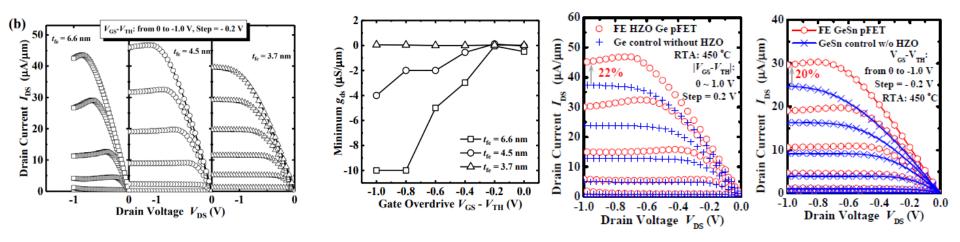

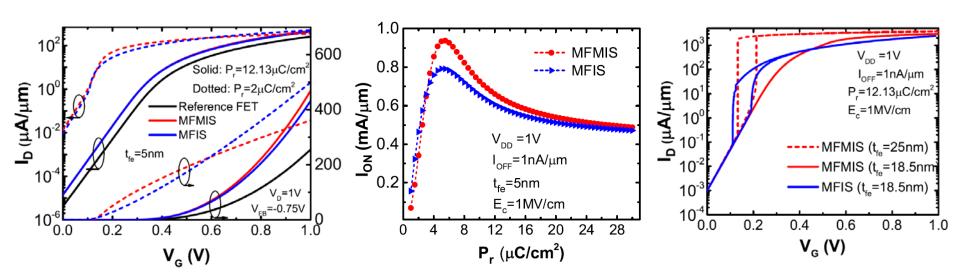

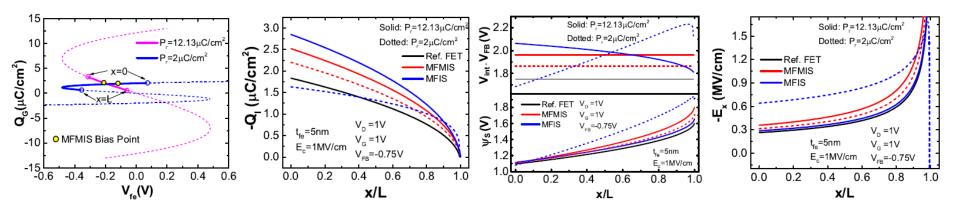

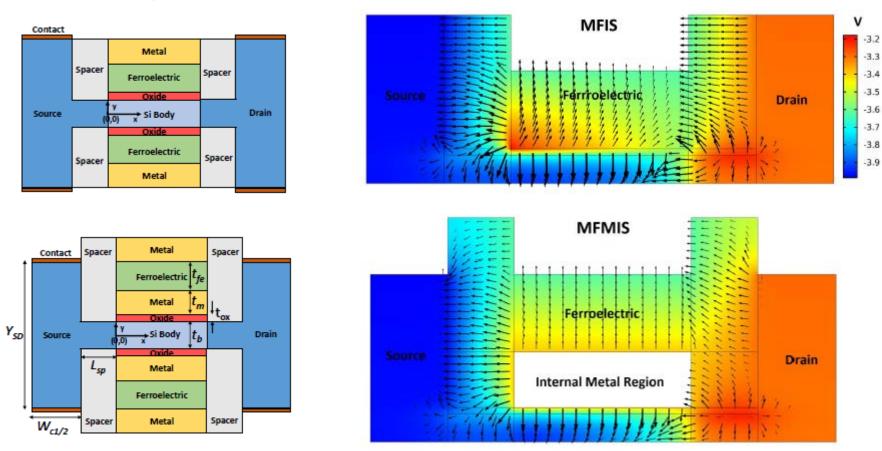

## MFIS Vs MFMIS

- MFIS excels MFMIS for low P<sub>r</sub> ferroelectrics only.

- A smooth hysteresis behavior in MFIS compared to MFMIS.

- MFIS is more prone to hysteresis → exhibits hysteresis at lower thicknesses compared to MFMIS.

G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "Physical Insights on Negative Capacitance Transistors in Non-Hysteresis and Hysteresis Regimes: MFMIS vs MFIS Structures", accepted in *IEEE Transactions on Electron Devices*, 2018.

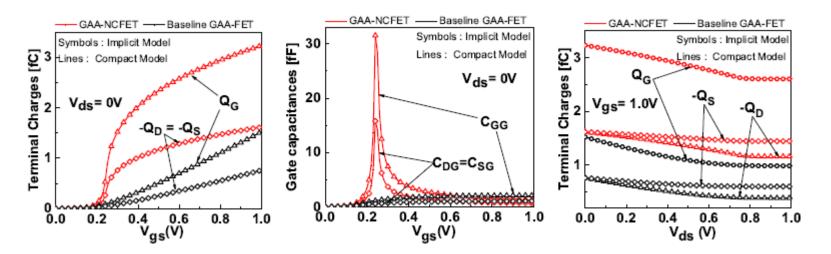

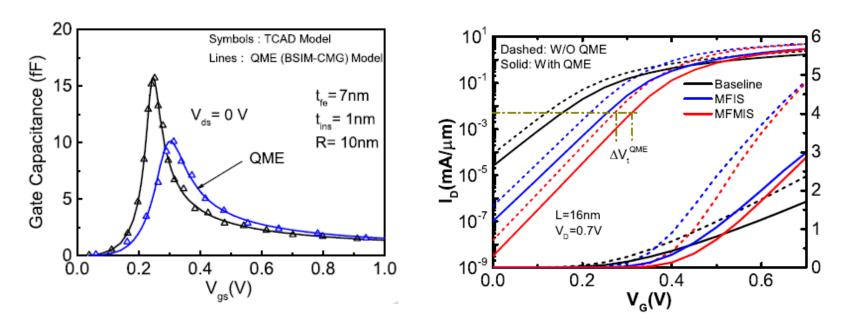

# Compact Modeling of MFIS GAA-NCFET

$$V_{\rm fe} = a_0 Q + b_0 Q^3$$

Radial Dependence in Ferroelectric Parameter:

$$a_0 = 2aR \ln[1 + t_{\rm fe}/(R + t_{\rm ins})]$$

$$b_0 = 2bR^3[1/(R + t_{\rm ins})^2 - 1/(R + t_{\rm ins} + t_{\rm fe})^2]$$

$$Q = \varepsilon_{\rm si} \left( \frac{d\psi}{d\rho} \right) \bigg|_{\rho = R} = \left( \frac{2\varepsilon_{\rm si}}{R} \right) \left( \frac{2kT}{q} \right) \left( \frac{\beta^2}{1 - \beta^2} \right)$$

Voltage Balance:

$$V_g - \Delta \phi - \psi_s = (a_0 + 1/C_{\text{ins}})Q + b_0 Q^3$$

$$\ln(\beta) - \ln(1 - \beta^2) + m\left(\frac{\beta^2}{1 - \beta^2}\right) + n\left(\frac{\beta^2}{1 - \beta^2}\right)^3 - G = 0$$

$V_g$

Gate Ferroelectric

Insulator

Channel

Insulator Ferroelectric Gate

$\rightarrow$  Goal: Explicit Model for  $\beta$  with good initial guess valid in all region of NCFET operation which will be used for further calculation of drain current and terminal charges.

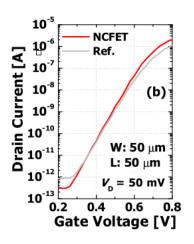

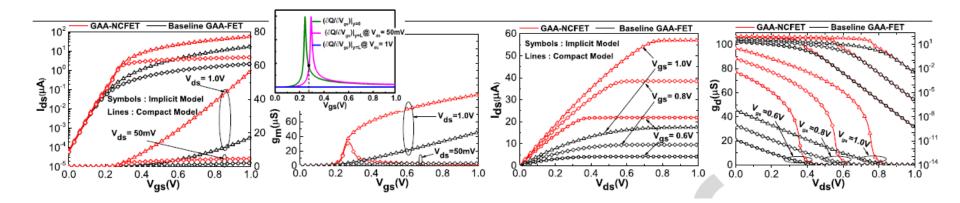

## Drain Current Model Validation

#### **Against Full Implicit Calculations**

- In contrast to bulk-NCFETs

- Multi-gate NCFETs with an undoped body exhibit same I<sub>OFF</sub> and V<sub>th</sub> due to absence of bulk charges.

- GAA-NCFET characteristics show different bias dependence due to the absence of bulk charge.

A. D. Gaidhane, G. Pahwa, A. Verma, and Y. S. Chauhan, "Compact Modeling of Drain Current, Charges and Capacitances in Long Channel Gate-All-Around Negative Capacitance MFIS Transistor", accepted in IEEE Transactions on Electron Devices, 2018.

# Terminal Charges in GAA-NCFET

- Peak in the gate capacitance is observed where the best capacitance matching occurs between the internal FET and the ferroelectric layer.

- For high  $V_{DS}$ , the  $Q_G$  for GAA-NCFET is saturates to  $(4/5)^{th}$  of the maximum value (at Vds = 0) in contrast to conventional devices for which it saturates to  $(2/3)^{rd}$  of the maximum value.

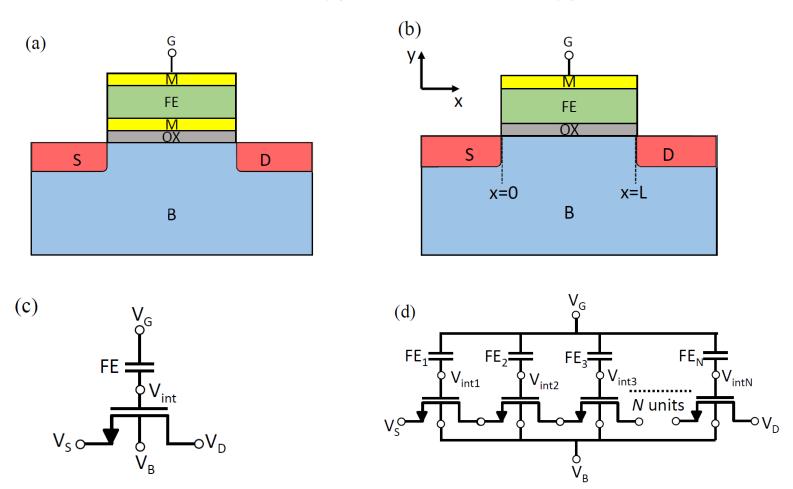

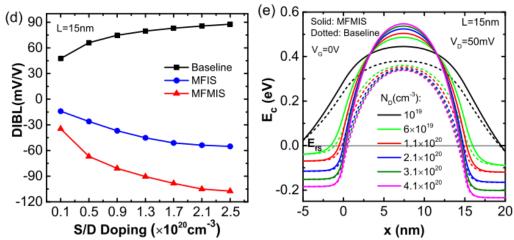

## MFMIS Vs MFIS

G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "*Physical Insights on Negative Capacitance Transistors in Non-Hysteresis and Hysteresis Regimes: MFMIS vs MFIS Structures*", IEEE Transactions on Electron Devices, Vol. 65, Issue 3, Mar. 2018.

# Comparing I<sub>D</sub>-V<sub>G</sub> and I<sub>D</sub>-V<sub>D</sub> Characteristics (long channel)

• MFIS excels MFMIS for low P<sub>r</sub> ferroelectrics only, in long channel NCFETs.

# Understanding different trends with P<sub>r</sub>

- Total current in ON regime ≈ drift current = inversion charge \* horizontal electric field

- For high P<sub>r</sub>, charge is higher for MFIS, but electric field in channel is low due to a decreasing V<sub>int</sub> profile from source to drain, which results in lower current than MFMIS.

- For low P<sub>r</sub>, charge is lower for MFIS, but electric field in channel is high due to a increasing V<sub>int</sub> profile from source to drain, which results in higher current than MFMIS.

G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "*Physical Insights on Negative Capacitance Transistors in Non-Hysteresis and Hysteresis Regimes: MFMIS vs MFIS Structures*", IEEE Transactions on Electron Devices, Vol. 65, Issue 3, Mar. 2018.

# Hysteresis Behavior

- Continuous switching of dipoles from source to drain results in a smooth hysteresis behavior in MFIS compared to MFMIS where dipoles behave in unison.

- Source end dipole switches, first, owing to its least hysteresis threshold.

- Non-zero drain bias disturbs capacitance matching in MFMIS resulting in a delayed onset of hysteresis.

- MFIS is more prone to hysteresis → exhibits hysteresis at lower thicknesses compared to MFMIS.

G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "*Physical Insights on Negative Capacitance Transistors in Non-Hysteresis and Hysteresis Regimes: MFMIS vs MFIS Structures*", IEEE Transactions on Electron Devices, Vol. 65, Issue 3, Mar. 2018.

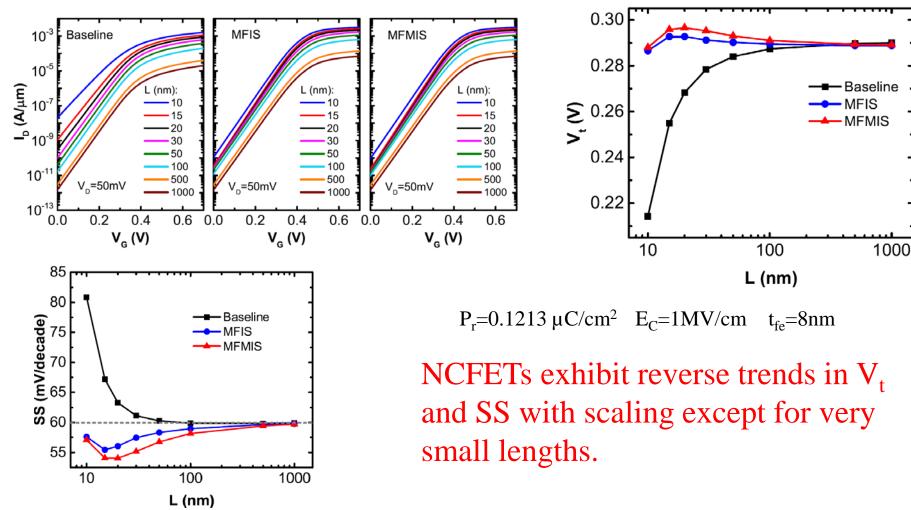

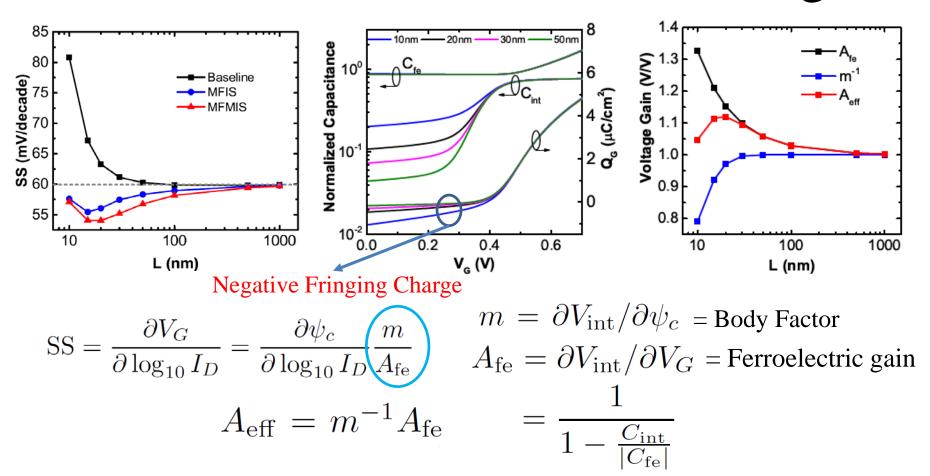

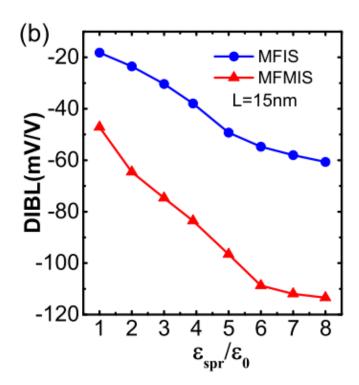

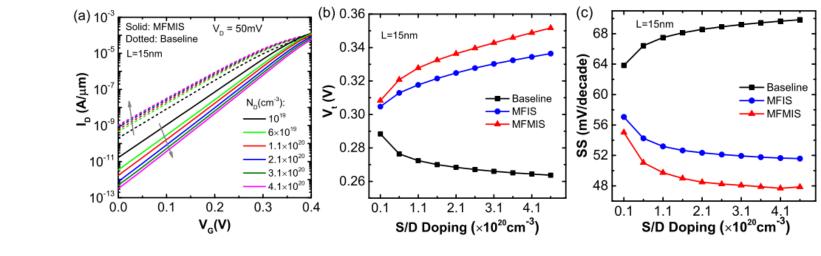

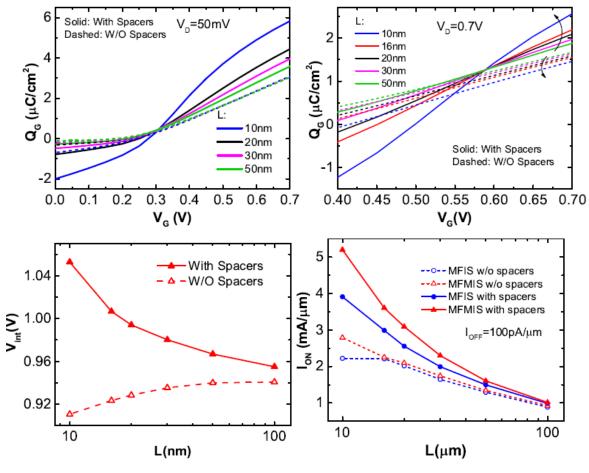

## MFMIS vs MFIS: Short Channel Effects

## OFF Regime (low V<sub>D</sub>)

#### 2D Numerical Simulation Results in COMSOL

G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Numerical Investigation of Short Channel Effects in Negative Capacitance Transistors: MFMIS Versus MFIS Structures", IEEE Transactions on Electron Devices.

Yogesh Chauhan, IIT Kanpur

74

## Reverse V<sub>t</sub> Shift with Scaling

- Coupling of inner fringing electric field to the ferroelectric increases with scaling, which increases the voltage drop across ferroelectric and hence, the conduction barrier height.

- In MFIS, fringing effect remains localized to channel edges only → Halo Like barriers.

- In MFMIS, internal metal extends this effect to the entire channel  $\rightarrow$  larger  $V_t$  than MFIS.

G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Numerical Investigation of Short Channel Effects in Negative Capacitance Transistors: MFMIS Versus MFIS Structures", IEEE Transactions on Electron Devices.

## Reverse SS trends with Scaling

$L\downarrow,\frac{c_{int}}{|c_{fe}|}\uparrow,A_{fe}\uparrow,m\downarrow,A_{eff}\uparrow,SS\downarrow$  (except for very small lengths where

G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Numerical Investigation of Short Channel Effects in Negative m dominates). Capacitance Transistors: MFMIS Versus MFIS Structures", IEEE Transactions on Electron Devices.

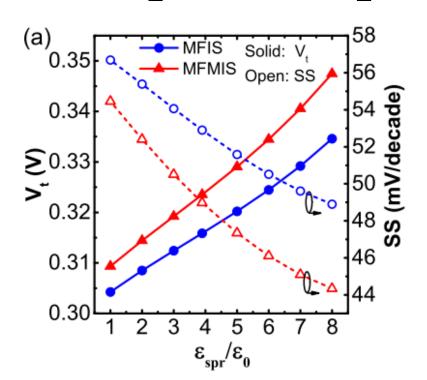

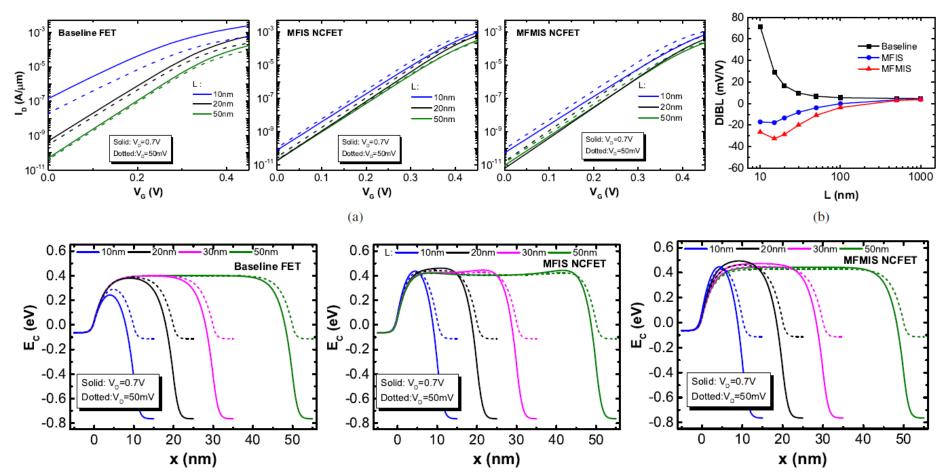

## Impact of Spacer Permittivity

Increasing the spacer permittivity enhances the outer fringing electric field, which leads to a rise in Vt and reduction in SS and DIBL.

G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Numerical Investigation of Short-Channel Effects in Negative Capacitance MFIS and MFMIS Transistors: Subthreshold Behavior", in IEEE Transactions on Electron Devices, vol. 65, no. 11, pp. 5130–5136, Nov. 2018.

### OFF Regime (high V<sub>DS</sub>): Negative DIBL

- Negative DIBL effect increases with Scaling.

- More pronounced in MFMIS than MFIS.

G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Numerical Investigation of Short Channel Effects in Negative Capacitance Transistors: MFMIS Versus MFIS Structures", IEEE Transactions on Electron Devices.

## Impact of S/D doping

- NCFETs exhibit trends opposite to baseline FET with respect to the increase in N<sub>D</sub>.

- Strength of fringing field originated from ionized S/D dopant ions increases with N<sub>D</sub>.

79

G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Numerical Investigation of Short-Channel Effects in Negative Capacitance MFIS and MFMIS Transistors: Subthreshold Behavior", in IEEE Transactions on Electron Devices, vol. 65, no. 11, pp. 5130–5136, Nov. 2018.

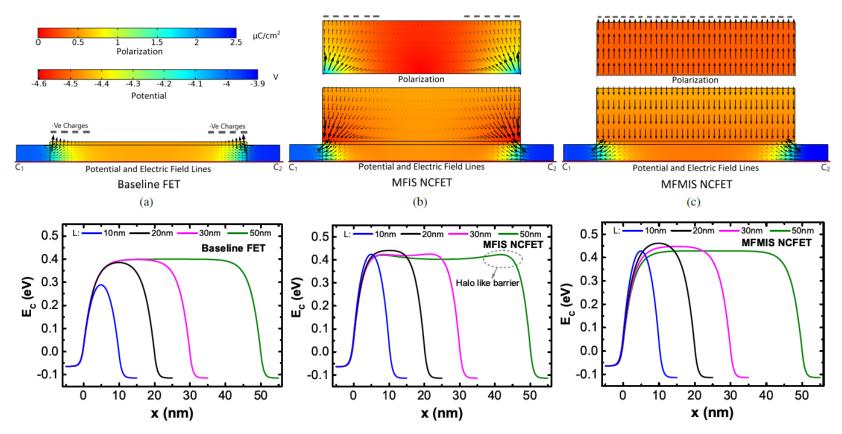

### ON Regime: Potential and field distribution

- The internal floating metal gate maintains a uniform electrical field distribution throughout the ferroelectric and a uniform potential (Vint) at ferroelectric-oxide interface.

- In the MFIS, however, electric field distribution and Vint at the interface are non-uniform.

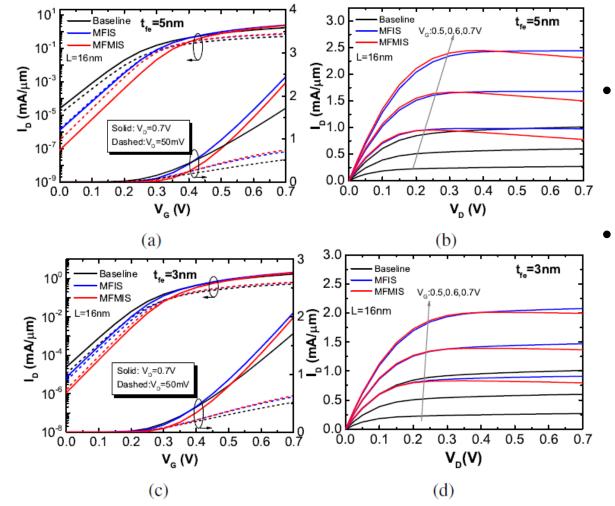

## ON Regime: Electrical Characteristics

- Drain side charge pinches-off earlier in MFIS than MFMIS due to strong localized drain to channel coupling  $\rightarrow$  lower  $V_{DSat}$  of MFIS results in lower  $I_{DS}$ .

- However, internal metal in MFMIS helps  $V_{DS}$  impact to easily reach source side  $\rightarrow Q_{IS} \downarrow$ → Larger NDR effect in MFMIS than MFIS.

- In long channel, MFMIS excels MFIS, however, for short channels vice-versa is true due to substantial NDR effect in former for iso-V<sub>FB</sub> case only. G. Pahwa et al., IEEE Transactions on Electron Devices, 2019.

## ON Regime: Impact of Spacers

G. Pahwa et al., IEEE Transactions on Electron Devices, 2019.

Without Spacers: Inner Fringing Only With Spacers: Inner + Outer Fringing

$$A_V = \frac{\partial V_{int}}{\partial V_G} = \frac{|C_{fe}|}{|C_{fe}| - C_{int}}$$

- C<sub>int</sub> increases with scaling in NCFETs with spacers due to outer fringing capacitances→increases gain.

- For W/O spacers, V<sub>int</sub> decreases due to absence of outer fringing, uncompensated drain side inner fringing, and increased drain to channel coupling.

Yogesh Chauhan, IIT Kanpur

### Impact of Quantum Mechanical Effects

• The QME results in an increase in the effective oxide thickness of the internal FET which eventually diminishes the benefits achievable from NC effect for the particular value of ferroelectric thickness.

A. D. Gaidhane, G. Pahwa, A. Verma, and Y. S. Chauhan, "Compact Modeling of Drain Current, Charges and Capacitances in Long Channel Gate-All-Around Negative Capacitance MFIS Transistor", accepted in IEEE Transactions on Electron Devices, 2018.

G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Numerical Investigation of Short-Channel Effects in Negative Capacitance MFIS and MFMIS Translations of Processing Processing Processing Processing Control of Processing Processi

## Impact of Ferroelectric Thickness

- NC influence decreases with t<sub>fe</sub> which also starts to homogenise the internal gate potential.

- Thus, relative difference between MFIS and MFMIS diminishes as t<sub>fe</sub> is decreased.

G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Numerical Investigation of Short-Channel Effects in Negative Capacitance MFIS and MFMIS Transactions on Electron Devices, 2019.

## Does polarization damping really limit operating frequency of NC-FinFET based circuits?

#### Recent Demonstration by Global Foundries on 14nm NC-FinFET

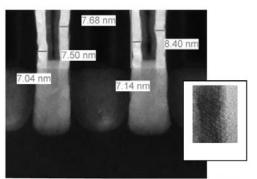

Fig. 3: TEM picture of minimum gate length RMG with 8nm FE. The inset shows the crystallinity of the FE film.

[1] Krivokapic, Z. et al.,

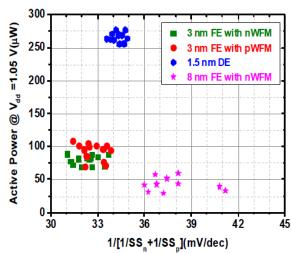

Fig. 13: Active power of FO3 inverter RO vs. effective SS for  $V_{dd}$ =1.05V.

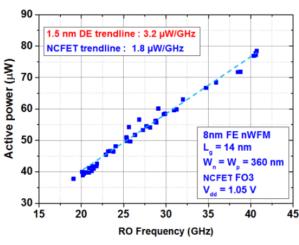

Fig. 14: Active power of NCFET FO3 inverter RO with W<sub>n</sub>=W<sub>p</sub>=360nm, L=14nm.

- Ring Oscillators with NC-FinFET can operate at frequencies similar to FinFET but at a lower active power<sup>[1]</sup>.

- Another theoretical study predicted intrinsic delay due to polarization damping in NCFET to be very small (270 fs)<sup>[2]</sup>.

[2] Chatterjee, K., Rosner, A. J. & Salahuddin, IEEE Electron Device Letters 38, 1328–1330 (2017).

**IEDM 2017**

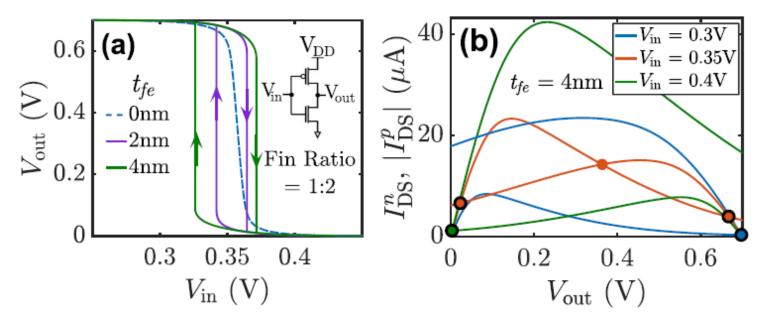

### NC-FinFET based inverters

Although the transistor characteristics show no Hysteresis, the VTCs of NC-FinFET inverters can still exhibit it due to the NDR region in the output characteristics.

T. Dutta, G. Pahwa, A. R. Trivedi, S. Sinha, A. Agarwal, and Y. S. Chauhan, "Performance Evaluation of 7 nm Node Negative Capacitance FinFET based SRAM", IEEE Electron Device Letters, Aug. 2017.

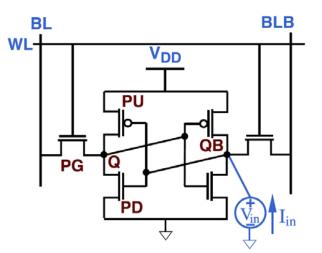

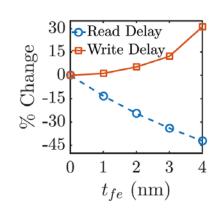

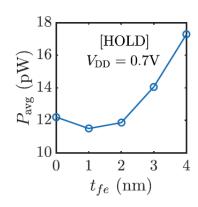

### NC-FinFET based SRAM

06/21/2019

87

- Read time: reduced due to the increased drive current

- Write time: slower due to the gate capacitance enhancement

- P<sub>avg</sub>: NC-SRAM performs better with lower standby leakage only at small t<sub>fe</sub>, taking advantage of the lower subthreshold currents

T. Dutta, G. Pahwa, A. R. Trivedi, S. Sinha, A. Agarwal, and Y. S. Chauhan, "Performance Evaluation of 7 nm Node Negative Capacitance FinFET based SRAM", IEEE Electron Device Letters, Aug. 2017.

Yogesh Chauhan, IIT Kanpur

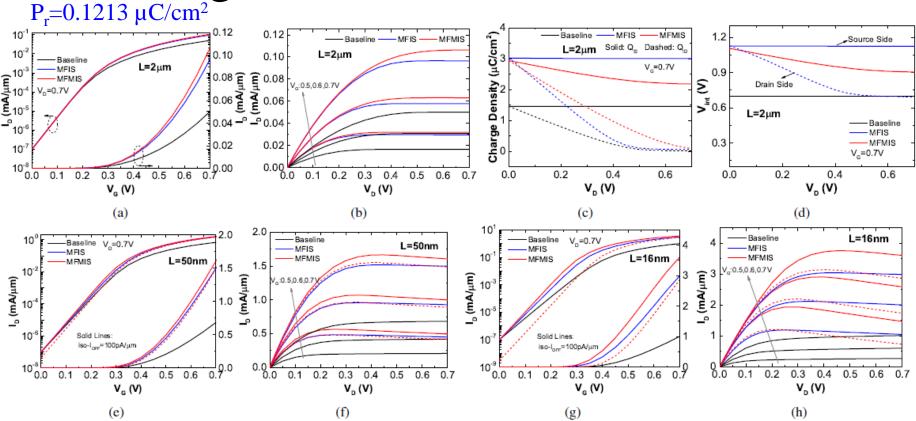

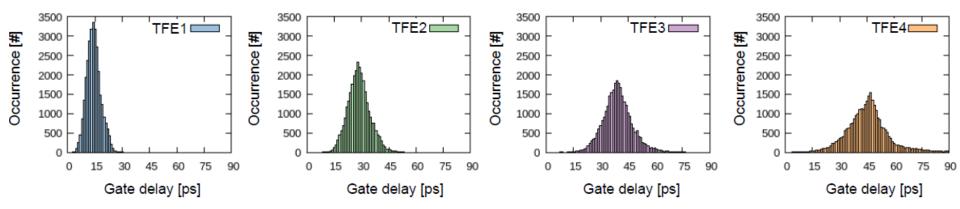

# Effects of NCFET on standard cells: 7nm FinFET standard cell library

Increasing t<sub>fe</sub> – larger A<sub>v</sub> in transistors (i.e., steeper slope and higher ON current) → Delay of cells become smaller.

# Effects of NCFET on standard cells: 7nm FinFET standard cell library

Using a ferroelectric with 1nm, 2nm, 3nm and 4nm thickness provides a speedup of around 15%, 30%, 40% and 45% respectively, in the delay of gates at the operating voltage of 0.7V.

• Quantifying the relative delay decrease/improvement of cells within the 7nm FinFET standard cell library due to NCFET at  $V_{DD} = 0.7V$ .

# Effects of NCFET on standard cells: 7nm FinFET standard cell library

- Increase in t<sub>fe</sub> leads to an increase in the total cells' capacitance which further increases internal power of the cells.

- Same baseline performance (i.e., frequency) can be achieved at a lower voltage, which leads to quadratic saving in dynamic power and exponential saving in stand-by power, thus, compensating the side effect of NCFET with respect to power.

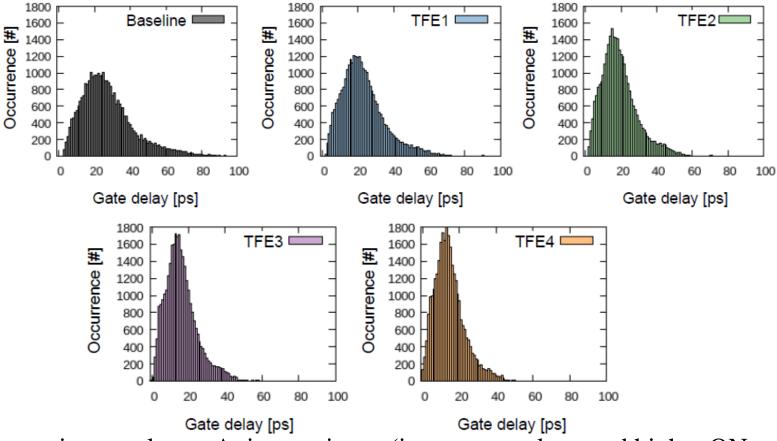

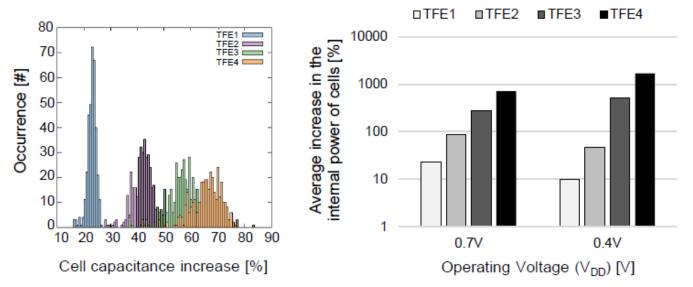

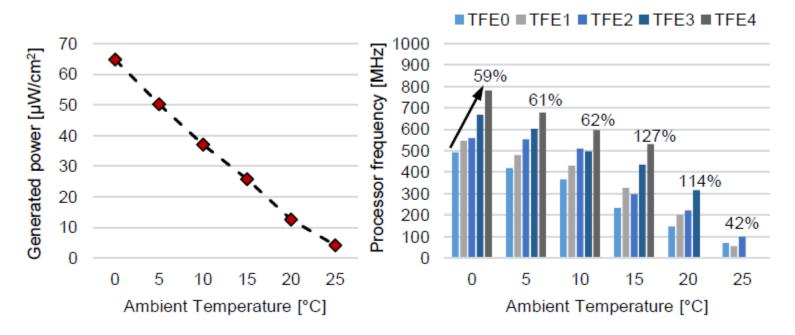

# Effects of NCFET on future processor design

TFE1: 1nm ferroelectric, TFE2: 2nm ferroelectric, TFE3: 3nm ferroelectric, TFE4: 4nm ferroelectric

- (a) What is the frequency increase due to NCFET under the same voltage constraint?

- (b) What is the frequency increase under the same (i.e., baseline) power density constraint?

- (c) What is the minimum operating voltage along with the achieved power reduction under the same (i.e., baseline) performance (i.e., frequency) constraint?

- H. Amrouch, G. Pahwa, A. D. Gaidhane, J. Henkel, and Y. S. Chauhan, "Negative Capacitance Transistor to Address the Fundamental Limitations in Technology Scaling: Processor Performance", IEEE Access, 2018.

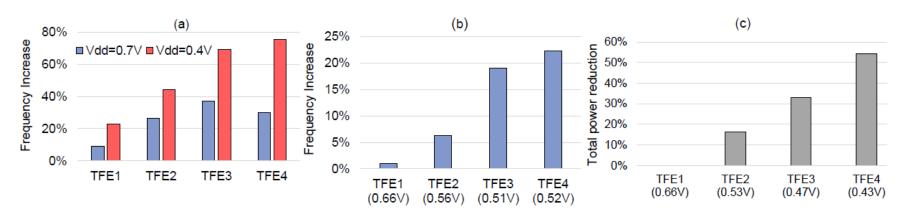

#### NC-FinFET based Processor Performance

• NCFET with ferroelectric thickness more than 1nm leads to a noticeable temperature reduction, due to the decrease in the on-chip power density.

#### NC-FinFET based Processor Performance

#### **Energy harvesting and IOT**

• Under very small power budgets harvested from body heat, NCFET technology enables the processor to operate at around 42-127% higher frequency compared to the conventional FinFET technology.

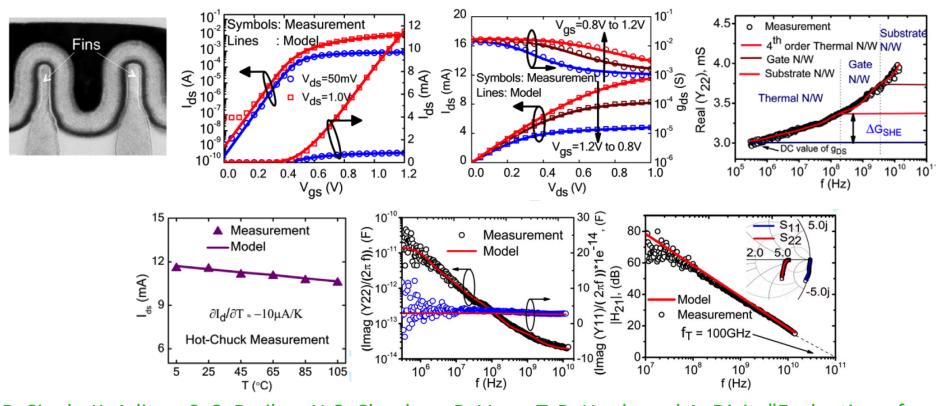

### NC-FinFET RF Performance

- Baseline Technology: 10 nm node RF FinFET

- RF Parameters extraction using BSIM-CMG model

- BSIM CMG coupled with L-K for NC-FinFET analysis

R. Singh, K. Aditya, S. S. Parihar, Y. S. Chauhan, R. Vega, T. B. Hook, and A. Dixit, "Evaluation of 10nm Bulk FinFET RF Performance - Conventional vs. NC-FinFET", IEEE Electron Device Letters, Aug. 2018.

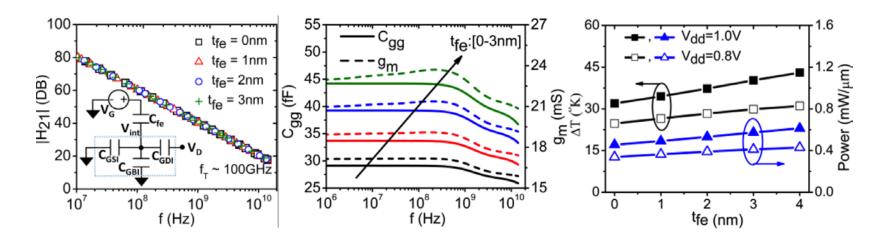

### NC-FinFET RF Performance

- Current gain ( $\propto {g_m}/{c_{gg}}$ ) is almost independent of  $t_{fe}$  as both the  $g_m$  and  $c_{gg}$  increase with  $t_{fe}$  almost at a constant rate.

- Cut-off frequency  $(f_T)$  remains identical for both the Baseline and NC-FinFET.

- Temperature rise and Power consumption due to self-heating increase with  $t_{fe}$  as  $I_d$  increases. Reduce  $V_{dd}$  to achieve energy efficient performance.

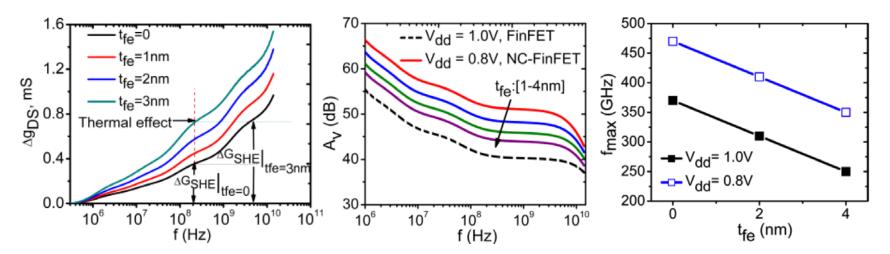

### NC-FinFET RF Performance

•  $g_{ds}$  and self heating  $(\Delta G_{SHE} \propto g_{ds}(f) - g_{ds}(dc))$  both increase with  $t_{fe}$  due to increased capacitance matching between  $C_{fe}$  and  $C_{int}$ .

$$g_{ds} = \frac{\partial I_{ds}}{\partial V_{ds}} = \frac{\partial I_{ds}}{\partial V_{int}} * \frac{\partial V_{int}}{\partial V_{ds}} = g_m^{int} * A_V^D$$

where  $A_V^D = \frac{-C_{GDI}}{|C_{fe}| - C_{int}}$

- Voltage gain  $(A_V = g_m/g_{ds} = C_{fe}/C_{GDI})$  decreases with  $t_{fe}$  due to decrease in  $C_{fe}$ .

- Maximum oscillation frequency  $(f_{max})$  also reduces with  $t_{fe}$  which can be compensated by reducing  $V_{dd}$ .

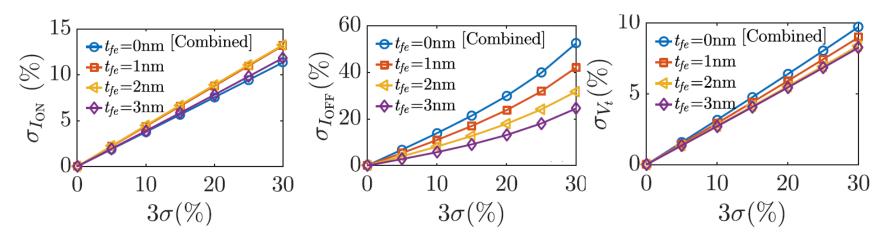

## Impact of Process Variations

- Variability in  $I_{ON}$ ,  $I_{OFF}$ , and  $V_t$  due to combined impact of variability in  $L_g$ ,  $T_{fin}$ ,  $H_{fin}$ , EOT,  $t_{fe}$ ,  $E_c$ , and  $P_r$

- $I_{ON}$ : Improvement is non-monotonic with  $t_{fe}$

- I<sub>OFF</sub>: Decreases monotonically with t<sub>fe</sub>

- V<sub>t</sub>: Decreases monotonically with t<sub>fe</sub>

T. Dutta, G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Impact of Process Variations on Negative Capacitance FinFET Devices and Circuits", IEEE Electron Device Letters, 2018.

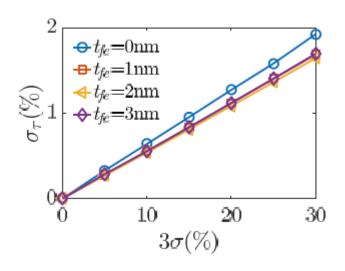

## Process Variation in Ring Oscillator

- The overall average delay variability in NC-FinFET based RO is lesser compared to the reference RO.

- The improvement is non-monotonic with nominal FE thickness scaling.

11-stage Ring-Oscillator: Variation in  $\tau$  due to combined variation

T. Dutta, G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Impact of Process Variations on Negative Capacitance FinFET Devices and Circuits", IEEE Electron Device Letters, 2018.

## Open Questions

- Is NC a static or transient phenomenon?

- Physical explanation of NC effect

- Second order effects

- Impact of grain boundaries and their sizes

- Impact of multi-domain effects

- Impact of traps

- Impact of FE thickness

- Reliability

- Impact of NDR/NDIBL on circuits

### Conclusion

- Maintaining  $I_{ON}/I_{OFF}$  is the biggest challenge in new technology nodes

- Negative capacitance FET is one of the best choice

- Need to find sweet material (HfZrO<sub>2</sub>?)

- Integration in conventional CMOS process remains a challenge (lot of progress)

- Compact (SPICE) Models are ready for circuit evaluation

## Relevant Publications from our group

- G. Pahwa, A. Agarwal and Y. S. Chauhan, "Numerical Investigation of Short-Channel Effects in Negative Capacitance MFIS and MFMIS Transistors: Above Threshold Behavior," in IEEE Transactions on Electron Devices, 2019.

- A.D. Gaidhane, G. Pahwa and Y.S. Chauhan, "Modeling of Inner Fringing Charges and Short Channel Effects in Negative Capacitance MFIS Transistor", accepted in Electron Devices Technology and Manufacturing (EDTM), 2019.

- G. Pahwa, A. Agarwal and Y. S. Chauhan, "Numerical Investigation of Short-Channel Effects in Negative Capacitance MFIS and MFMIS Transistors: Subthreshold Behavior," in IEEE Transactions on Electron Devices, Nov. 2018.

- Karishma Qureshi, G. Pahwa and Y.S. Chauhan, "Impact of Linear Intergranular Variation in Remnant Polarization on Negative Capacitance Field Effect Transistor", ICEE, 2018.

- A.D. Gaidhane, G. Pahwa and Y.S. Chauhan, "Compact Modeling of Drain Current in Double Gate Negative Capacitance MFIS Transistor", ICEE, 2018.

- H. Amrouch, G. Pahwa, A. D. Gaidhane, J. Henkel and Y. S. Chauhan, "Negative Capacitance Transistor to Address the Fundamental Limitations in Technology Scaling: Processor Performance," IEEE Access, Sep. 2018.

- A.D. Gaidhane, G. Pahwa, A. Verma, Y. S. Chauhan, "Compact Modeling of Drain Current, Charges, and Capacitances in Long-Channel Gate-All-Around Negative Capacitance MFIS Transistor," IEEE Transactions on Electron Devices, May 2018.

- G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "Physical Insights on Negative Capacitance Transistors in Non-Hysteresis and Hysteresis Regimes: MFMIS vs MFIS Structures", IEEE Transactions on Electron Devices, Mar. 2018.

- T. Dutta, G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Impact of Process Variations on Negative Capacitance FinFET Devices and Circuits", IEEE Electron Device Letters, Jan. 2018.

### Relevant Publications from Our group

- T. Dutta, G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Performance Evaluation of 7 nm Node Negative Capacitance FinFET based SRAM", IEEE Electron Device Letters, Aug. 2017.

- G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan,"Compact Model for Ferroelectric Negative Capacitance Transistor with MFIS Structure", IEEE Transactions on Electron Devices, Mar. 2017.

- G. Pahwa, T. Dutta, A. Agarwal, S. Khandelwal, S. Salahuddin, C. Hu, and Y. S. Chauhan, "Analysis and Compact Modeling of Negative Capacitance Transistor with High ON-Current and Negative Output Differential Resistance

Part I, Model description", IEEE Transactions on Electron Devices, Dec. 2016.

- G. Pahwa, T. Dutta, A. Agarwal, S. Khandelwal, S. Salahuddin, C. Hu, and Y. S. Chauhan, "Analysis and Compact Modeling of Negative Capacitance Transistor with High ON-Current and Negative Output Differential Resistance Part II, Model validation", IEEE Transactions on Electron Devices, Dec. 2016.

- G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "Energy-Delay Tradeoffs in Negative Capacitance FinFET based CMOS Circuits", IEEE ICEE, Dec. 2016. (Best Paper Award)

- G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "Designing Energy Efficient and Hysteresis Free Negative Capacitance FinFET with Negative DIBL and 3.5X ION using Compact Modeling Approach", IEEE ESSDERC, Switzerland, Sept. 2016. (Invited)

- G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Compact Modeling of Negative Capacitance Transistor with Experimental Validation", IWPSD, Dec. 2015.

## Thank You