## Physics and Modeling of Nano-Transistors

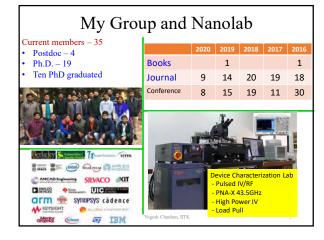

Dr. Yogesh S. Chauhan

Professor

Department of Electrical Engineering

IIT Kanpur, India

Email: <a href="mailto:chauhan@iitk.ac.in">chauhan@iitk.ac.in</a>

Homepage - http://home.iitk.ac.in/~chauhan/

## Outline

- Compact Modeling

- Bulk MOSFET and FinFET

- Negative Capacitance FET

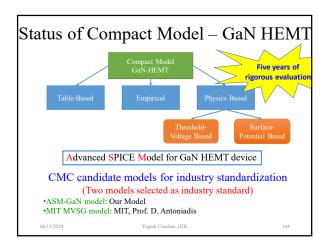

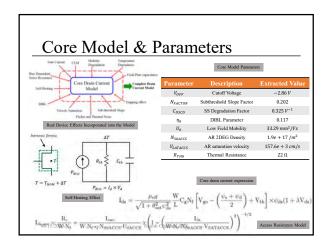

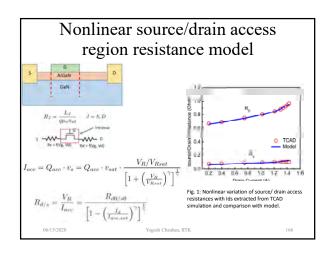

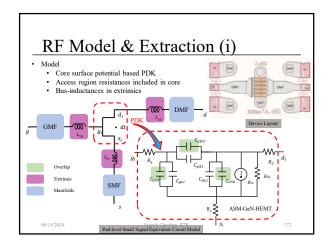

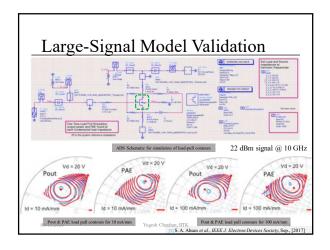

- ASM-GaN-HEMT Model

5/2020 Yogesh Chauhan,

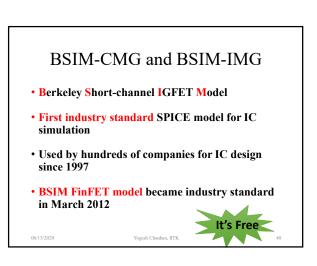

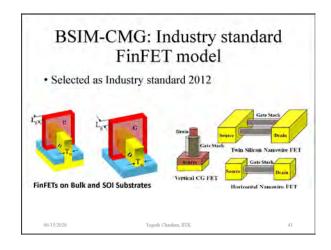

## Compact Modeling – <u>Industrial Research</u>

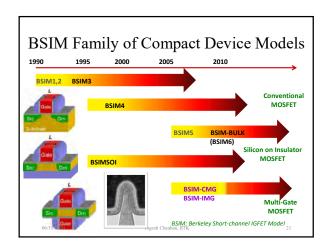

- Bulk MOSFET Modeling (DC to RF)

- · BSIM4 and BSIM6

- Partially Depleted SOI MOSFET Modeling (DC to RF)

- BSIM-SOI

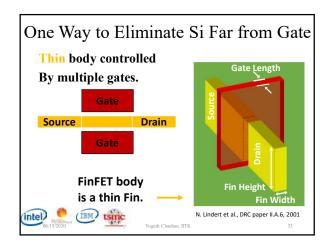

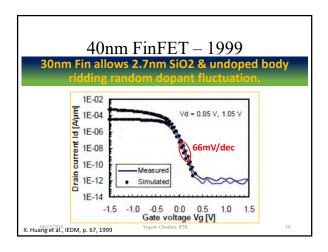

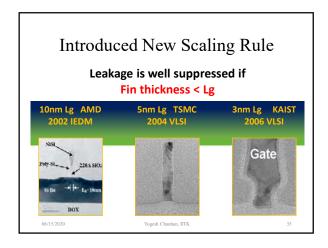

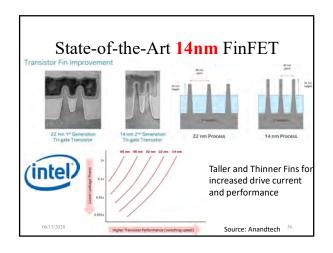

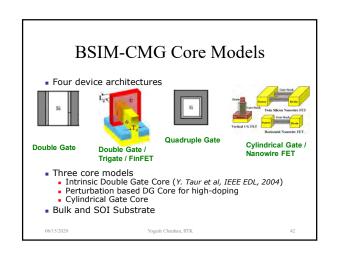

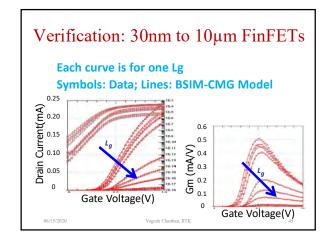

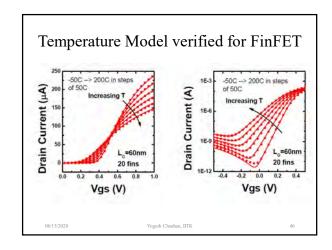

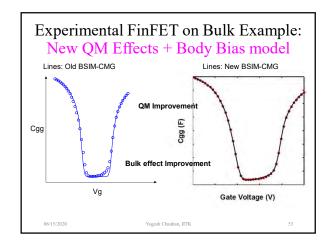

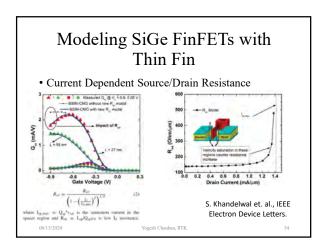

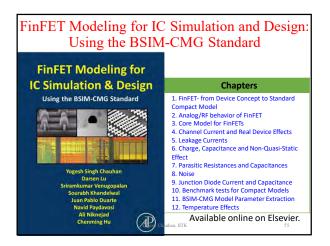

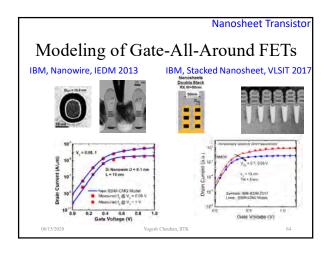

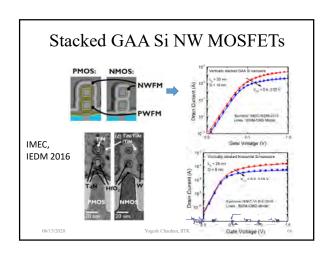

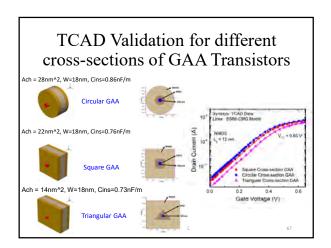

- Multigate MOSFET Modeling

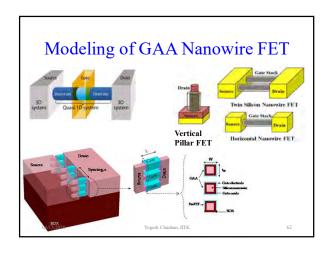

- FinFET & Nanowire Transistor BSIM-CMG

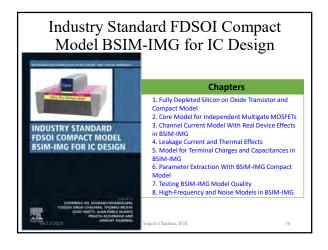

- Fully Depleted SOI (FDSOI) Transistor—BSIM-IMG

- High Voltage LDMOS Modeling using BSIM6 BSIM-HV

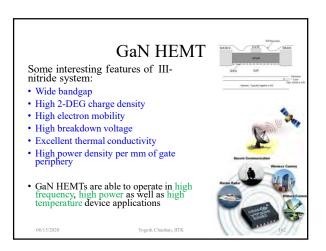

- GaN HEMT Modeling

- ASM-HEMT: industry standard

- DC, CV and RF Characterization

- All models are validated on measured data

- Working as BSIM Group member/consultant

06/15/2020

Yogesh Chauhan,

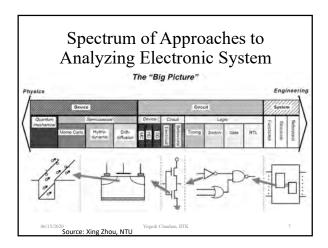

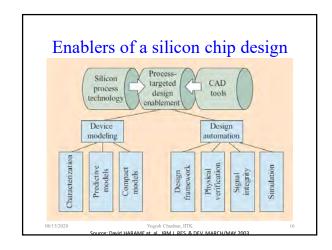

## Circuit simulation

- · Circuit simulation is an important part of any design

- Explosive growth of integrated circuit market in the 1970's resulted in the rise of importance of circuit simulation.

- · With integrated circuits, prototypes were expensive to build and difficult to troubleshoot.

- As designs became larger and more complicated, the need to use circuit simulators increased.

- · Time to market and cost.

### **SPICE Simulation**

- SPICE (Simulation Program with Integrated Circuits Emphasis) is a powerful general purpose circuit simulation program that is used to verify circuit designs and to predict the circuit behavior.

- SPICE was originally developed at the Electronics Research Laboratory of the University of California, Berkeley in early part of 1970.

- SPICE can do several types of circuit analyses.

Non-linear DC / Transient analysis, Linear AC Analysis

Noise analysis, Sensitivity analysis, Distortion analysis

06/15/2020

Yogesh Chauhan, IITK

## SPICE Development

• SPICE was developed out of a graduate class *project* at University of California, Berkeley

Laurence W. Nagel

L. W. Nagel and D. O. Pederson, "SPICE (Simulation Program with Integrated Circuit Emphasis), " Memorandum No. ERL-M382, University of California, Berkeley, Apr. 1973. " "http://www.bcs.berkeley.edu/Pub/786th8617973/228271.html"

## SPICE and Device Models nodal admittance matrix would be tion and its negative side effec Don Pederson correctly recognized that device models, not internal algorithms, were the keys to the success of a circuit simulation program. adequate as pivot choices in effectthe engineering intuition of c ing its factorization into lower and Special Issue on 40th Anniversary of SPICE SPRING 2011 FEEE SOLID-STATE CIRCUITS MAGAZINE Yogesh Chauhan, IITK

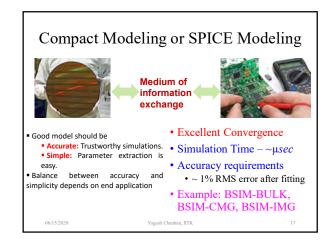

## Model Types

- Look Up Table Store measured or simulated data in a table.

- Physical model generally does not have parameters but does not fit with data accurately.

- Empirical models are mathematical models written to reflect measured characteristics

- · Angelov model for HEMT

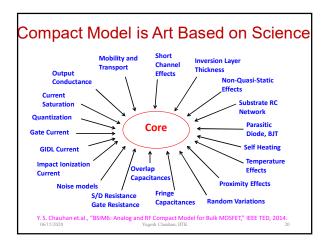

- Compact SPICE models are the physics based model but parametrized to fit measured data.

Yogesh Chauhan, IITK

## Industry Standard Compact Models • Standardization Body – Compact Model Coalition • CMC Members – EDA Vendors, Foundries, IDMs, Fabless, Research Institutions/Consortia

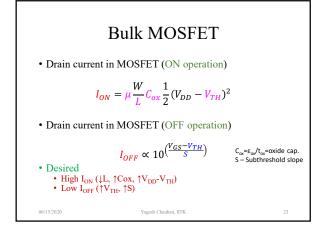

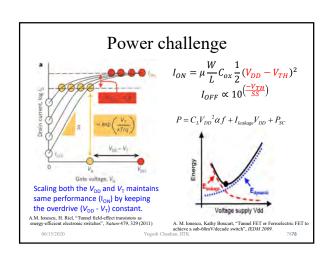

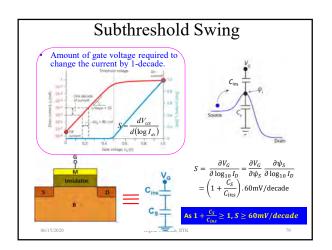

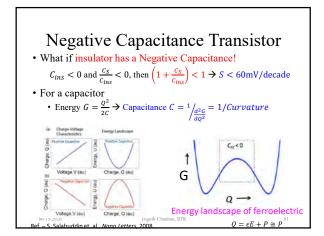

## Wasn't that smooth ride? • Where is the bottleneck? $I_{ON} = \mu \frac{W}{L} C_{ox} \frac{1}{2} (V_{DD} - V_{TH})^2$ • V<sub>TH</sub> and Subthreshold Slope can't be decreased $\log Scale$ $\log Scale$

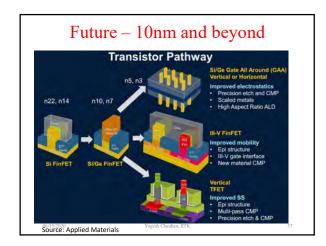

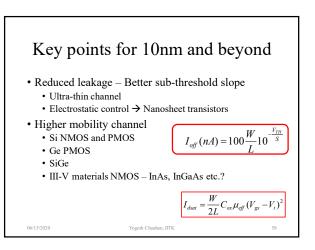

# Outline • Compact Modeling • Bulk MOSFET and FinFET • Negative Capacitance FET • ASM-GaN-HEMT Model Vogeth Chauthan, ITTK 39

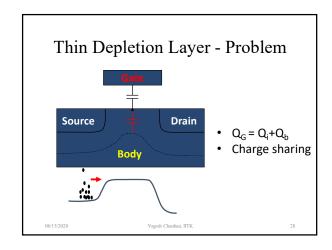

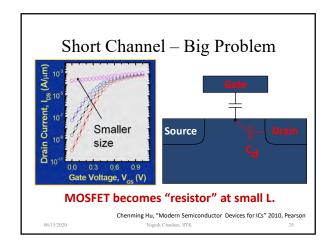

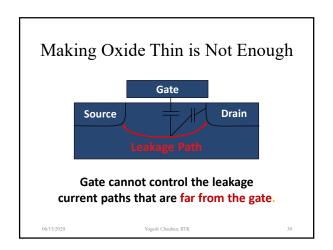

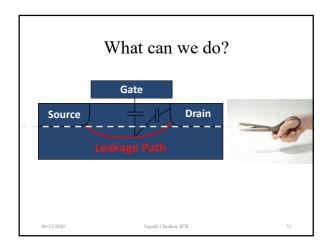

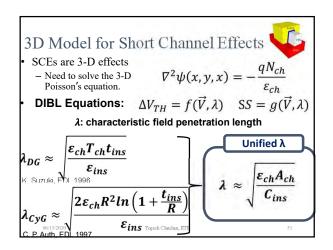

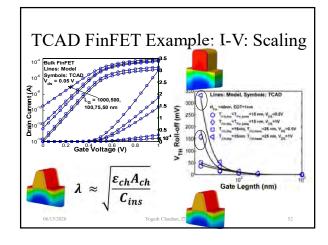

# Short Channel (2D) Effects $\frac{1}{r} \frac{\partial}{\partial r} \left( \frac{\partial \psi}{\partial r} \right) + \frac{\partial^2}{\partial y^2} \psi = \frac{qN_s}{\epsilon_{ss}}$ • Along the channel – 2D • Quasi-2D analysis $\frac{d^2 \psi_c}{dy^2} + \frac{V_g - V_B - \Psi_c}{\lambda^2} = \frac{qN_s}{\epsilon_{ss}}$ • Characteristic Length • Similar expression for Double Gate and FinFET/Trigate • Analytical expressions model • Threshold Voltage roll off • Drain induced barrier lowering (DIBL) • Sub-threshold swing degradation \*\*Vegeth Chambar, ITTK\*\* \*\*Auth and Plummer, IEEE FID. 2007.

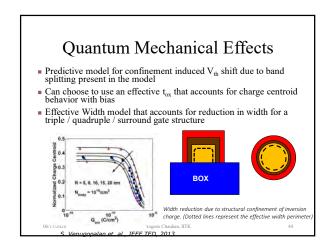

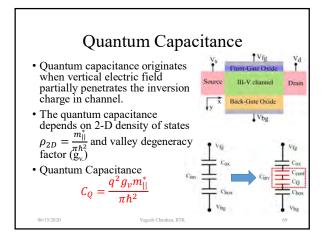

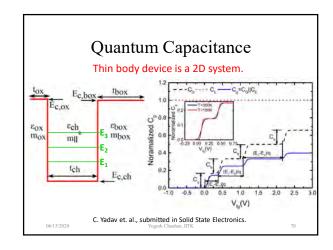

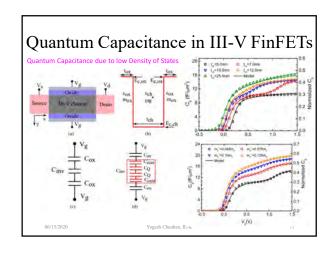

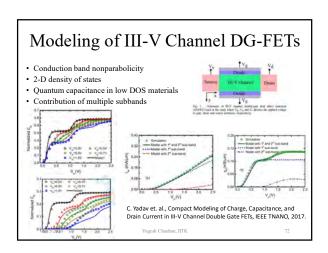

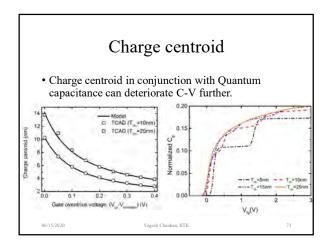

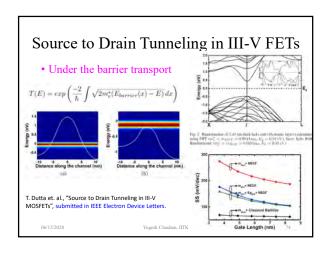

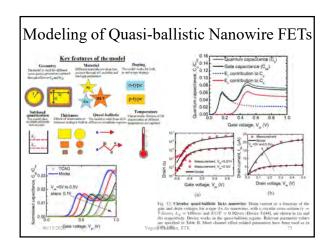

## 7nm & beyond – Would it be a smooth ride? • Effects in ultra-thin Si/Ge/III-V Transistors • Quantum Capacitance • Charge centroid • Source to Drain Tunneling • Bandgap variation with thickness • Effective mass variation with thickness

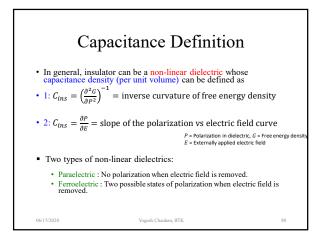

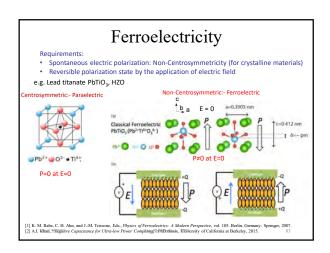

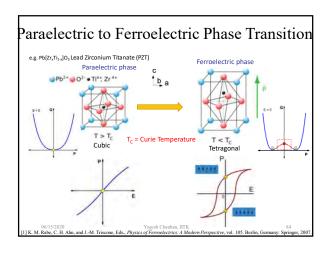

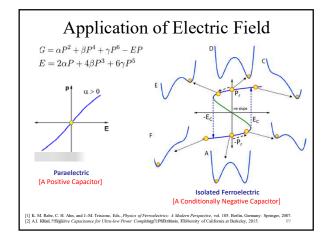

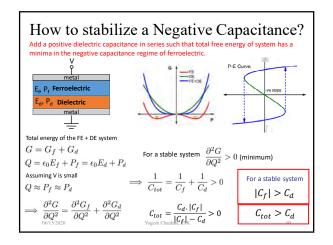

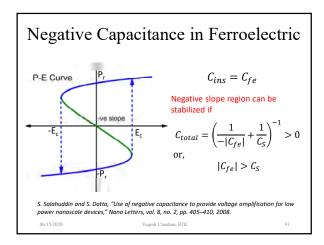

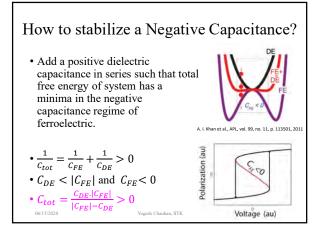

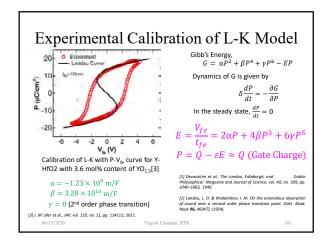

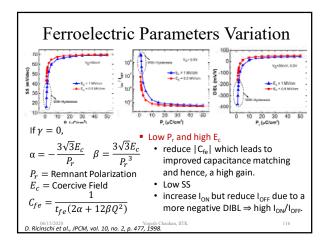

## Landau-Khalatnikov Theory of Non-Linear Dielectrics

- Free energy of a non-linear dielectric is given as  $G = \alpha P^2 + \beta P^4 + \gamma P^6 EP$

- $\alpha$  and  $\beta$  can be +ve or -ve but  $\gamma$  is always +ve for stability reasons.

- Dynamics of G is given by  $\delta \frac{dP}{dt} = -\frac{\partial G}{\partial P}$

- In the steady state,  $\frac{dP}{dt} = 0 \rightarrow E = 2\alpha P + 4\beta P^3 + 6\gamma P^5$

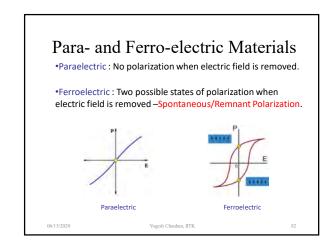

For  $\alpha > 0$  and at E = 0, there exit only one real root P=0

A Paraelectric Material

For  $\alpha < 0$  and at E = 0, there exit three real roots  $P=0,\pm P_r$  where  $P_r=\sqrt{\frac{\sqrt{\beta^2-3\alpha\gamma}-}{3\gamma}}$

A Ferroelectric Material has a non-zero P at zero E.

## Assumptions

Free energy of a non-linear dielectric  $G = \alpha P^2 + \beta P^4 + \gamma P^6 - EP$

- Polarization and Electric field are uniaxial. (perpendicular to electrodes)

- Polarization and Electric field magnitudes are uniform throughout the ferroelectric.

- Piezo-electricity is ignored.

### For E = 0, $G = \alpha P^2 + \beta P^4 + \gamma P^6$ and $\alpha = \alpha_0 (T - T_0), \alpha_0 > 0$ Ferroelectric Material a < 0 Note, P = 0 has a maximum. Not possible in an isolated ferroelectric $0=2\alpha P+4\beta P^3+6\gamma P^5$ $0 = 2\alpha P + 4\beta P^3 + 6\gamma P^5$ $\alpha < 0$ i.e. for T < T $_0$ ; at E = 0, there exist three real roots

L-K explanation of Phase Transition

- $\alpha > 0$  i.e. for T > T<sub>0</sub>; at E = 0, there exists only one real root,

- i.e. No polarization when electric field is removed

[P = 0 at E = 0]

Two possible states of polarization when electric field is removed.

idern Perspective, vol. 105. Berlin, Germany: Springs

$\sqrt{\beta^2 - 3\alpha\gamma} - \beta$

$P = 0, \pm P_r$  where

1 K M Rithé 3C/(H/(Ahn and L-M Triscone Eds. Physics of Figure

## Positive and Negative Capacitances Three possible solutions at E = 0P=0 is not possible in a isolated Ferroelectric due Only one solution to maxima of energy or a $\alpha > 0$ Paraelectric Fermelectric

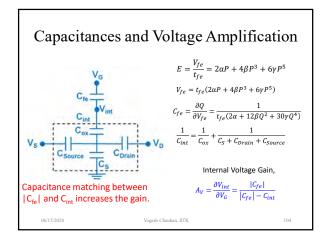

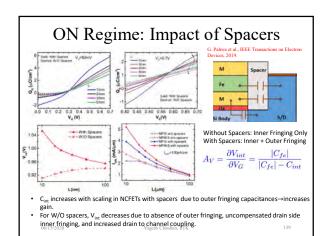

•  $g_{ds}$  and self heating  $(\Delta G_{SHE} \propto g_{ds}(f) - g_{ds}(dc))$  both increase with  $t_{fe}$  due to increased capacitance matching between  $C_{fe}$  and  $C_{int}$ .

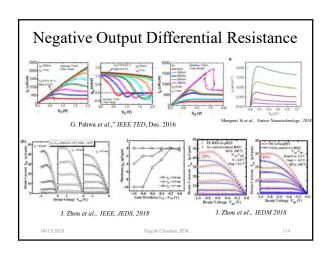

$$g_{ds} = \frac{\partial I_{ds}}{\partial v_{ds}} = \frac{\partial I_{ds}}{\partial v_{int}} * \frac{\partial v_{int}}{\partial v_{ds}} = g_m^{int} * A_V^D \quad \text{where} \quad A_V^D = \frac{-C_{GDI}}{|C_{fe}| - C_{int}}$$

- Voltage gain  $(A_V = g_m/g_{ds} = C_{fe}/C_{GDI})$  decreases with  $t_{fe}$  due to decrease in  $C_{fe}$ .

- Maximum oscillation frequency (f<sub>max</sub>) also reduces with t<sub>fe</sub> which can be compensated by reducing V<sub>dd</sub>.

5/15/2020 Yogesh Chauhan, IITK

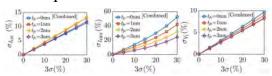

## Impact of Process Variations

- Variability in  $I_{ON}$ ,  $I_{OFF}$ , and  $V_t$  due to combined impact of variability in  $L_g$ ,  $T_{fin}$ ,  $H_{fin}$ , EOT,  $t_{fe}$ ,  $E_e$ , and  $P_r$

- I<sub>ON</sub>: Improvement is non-monotonic with t<sub>fe</sub>

- $I_{OFF}$ : Decreases monotonically with  $t_{fe}$

- Vt: Decreases monotonically with tfe

T. Dutta, G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Impact of Process Variations on Negative Capacitance FinFET Devices and Circuits", IEEE Electron Device Letters, 2018.

06/15/2020 Yogesh Chauhan, IITK 15

## Process Variation in Ring Oscillator

- The overall average delay variability in NC-FinFET based RO is lesser compared to the reference RO.

- The improvement is non-monotonic with nominal FE thickness scaling.

11-stage Ring-Oscillator: Variation in  $\tau$  due to combined variation

T. Dutta, G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Impact of Process Variations on Negative Capacitance FinFET Devices and Circuits", IEEE Electron Device Letters, 2018.

06/15/2020 Yogesh Chauhan, IITK

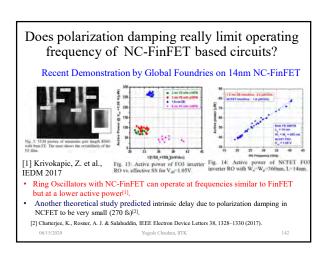

## **Open Questions**

- Is NC a static or transient phenomenon?

- Physical explanation of NC effect

- · Second order effects

- Impact of grain boundaries and their sizes

- Impact of multi-domain effects

- Impact of traps

- Impact of FE thickness

- Reliability, Variability

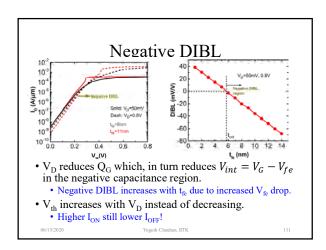

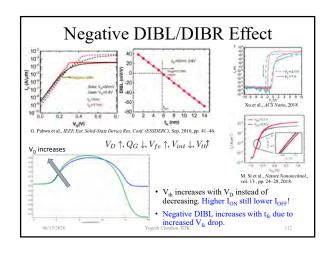

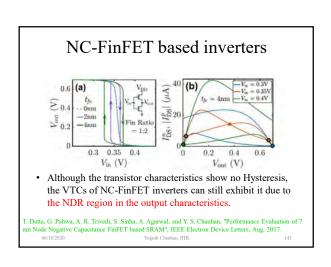

- Impact of NDR/NDIBL on circuits

06/15/2020 Yogesh Chauhan, IITK 154

### **Relevant Publications**

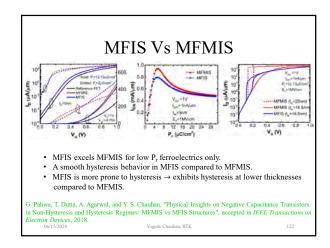

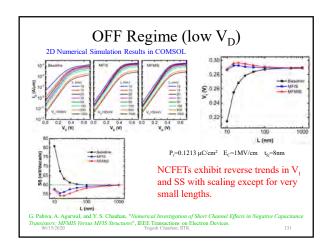

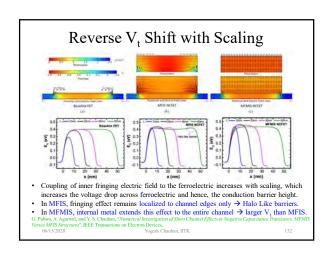

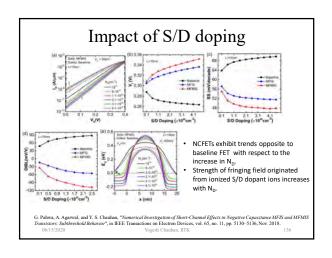

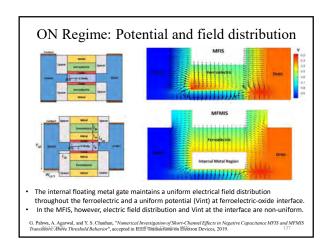

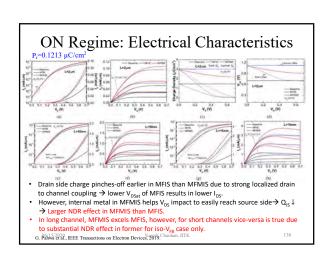

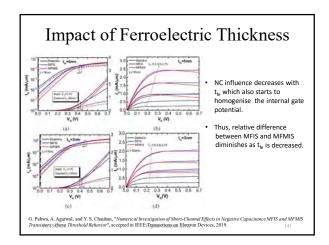

- G. Pahwa, A. Agarwal and Y. S. Chauhan, "Numerical Investigation of Short-Channel Effects in Negative Capacitance MFIS and MFMIS Transistors: Above Threshold Behavior," in IEEE Transactions on Electron Devices, 2019.

- A.D. Gaidhane, G. Pahwa and Y.S. Chauhan, "Modeling of Inner Fringing Charges and Short Channel Effects in Negative Capacitance MFIS Transistor", accepted in Electron Devices Technology and Manufacturing (EDTM), 2019.

- G. Pahwa, A. Agarwal and Y. S. Chauhan, "Numerical Investigation of Short-Channel Effects in Negative Capacitance MFIS and MFMIS Transistors: Subthreshold Behavior," in IEEE Transactions on Electron Devices, Nov. 2018.

- Karishma Qureshi, G. Pahwa and Y.S. Chauhan, "Impact of Linear Intergranular Variation in Remnant Polarization on Negative Capacitance Field Effect Transistor", ICEE, 2018.

- A.D. Gaidhane, G. Pahwa and Y.S. Chauhan, "Compact Modeling of Drain Current in Double Gate Negative Capacitance MFIS Transistor", ICEE, 2018.

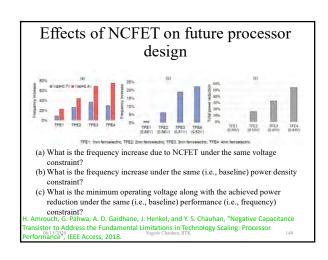

- H. Amrouch, G. Pahwa, A. D. Gaidhane, J. Henkel and Y. S. Chauhan, "Negative Capacitance Transistor to Address the Fundamental Limitations in Technology Scaling: Processor Performance," IEEE Access, Sep. 2018.

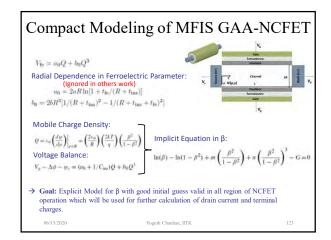

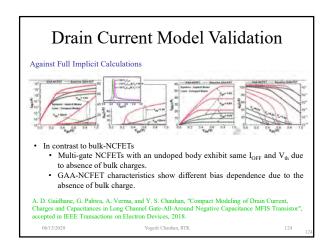

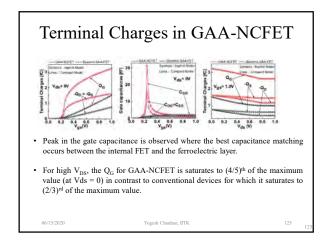

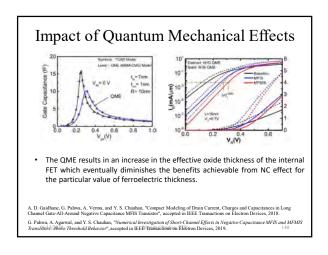

- A.D. Gaidhane, G. Pahwa, A. Verma, Y. S. Chauhan, "Compact Modeling of Drain Current, Charges, and Capacitances in Long-Channel Gate-All-Around Negative Capacitance MFIS Transistor," IEEE Transactions on Electron Devices, May 2018.

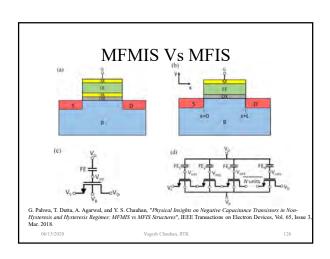

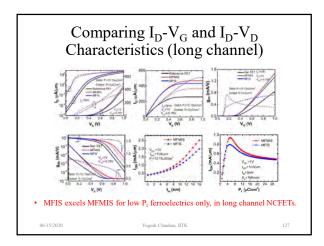

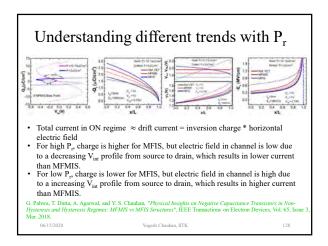

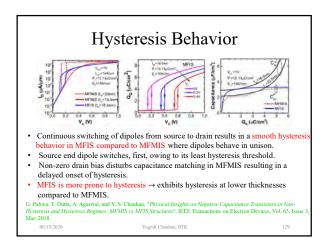

- G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "Physical Insights on Negative Capacitance Transistors in Non-Hysteresis and Hysteresis Regimes: MFMIS vs MFIS Structures", IEEE Transactions on Electron Devices, Mar. 2018.

- T. Dutta, G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Impact of Process Variations on Negative Capacitance FinFET Devices and Circuits", IEEE Electron Device Letters, Jan. 2018.

6/15/2020 Yogesh Chauhan, IITK

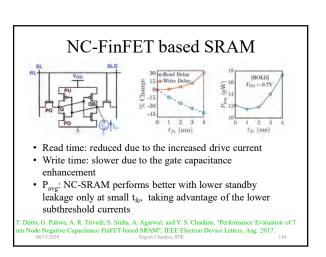

## Relevant Publications

- I. Dutta, G. Pahwa, A. Agarwai, and Y. S. Chauhan, "Performance Evaluation of / nm Node Negative Capacitance FinFET based SRAM", IEEE Electron Device Letters, Aug. 2017.

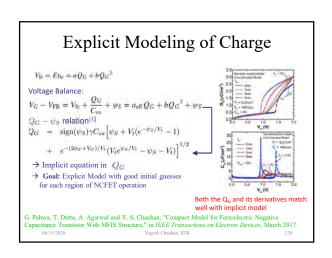

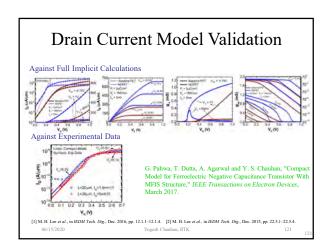

- G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "Compact Model for Ferroelectric Negative Capacitance Transistor with MFIS Structure", IEEE Transactions on Electron Devices, Mar. 2017.

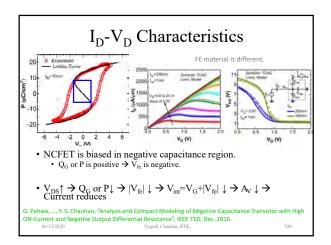

- G. Pahwa, T. Dutta, A. Agarwal, S. Khandelwal, S. Salahuddin, C. Hu, and Y. S. Chauhan, "Analysis and Compact Modeling of Negative Capacitance Transistor with High ON-Current and Negative Output Differential Resistance - Part I, Model description", IEEE Transactions on Electron Devices, Dec. 2016.

- G. Pahwa, T. Dutta, A. Agarwal, S. Khandelwal, S. Salahuddin, C. Hu, and Y. S. Chauhan, "Analysis and Compact Modeling of Negative Capacitance Transistor with High On-Current and Negative Output Differential Resistance - Part II, Model validation", IEEE Transactions on Electron Devices, Dec. 2016.

- G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "Energy-Delay Tradeoffs in Negative Capacitance FinFET based CMOS Circuits", IEEE ICEE, Dec. 2016. (Best Paper Award)

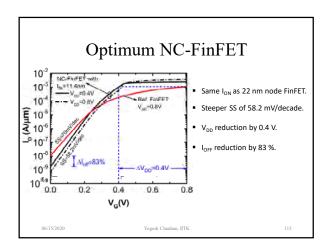

- G. Pahwa, T. Dutta, A. Agarwal, and Y. S. Chauhan, "Designing Energy Efficient and Hysteresis Free Negative Capacitance FinFET with Negative DIBL and 3.5X ION using Compact Modeling Approach", IEEE ESSDERC, Switzerland, Sept. 2016. (Invited)

- G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Compact Modeling of Negative Capacitance Transistor with Experimental Validation", IWPSD, Dec. 2015.

5/2020 Yogesh Chauhan, IITK 1

## Summary

- $\bullet$  Industry standard model development @ IITK

- All models are implemented in the Verilog A code

- Tested on commercial **simulators**

- · Validated with real device data

- Working with major semiconductor and EDA companies

06/15/2020

Yogesh Chauhan, IITk

175