# Wideband Tunable True-Time-Delay Architecture Using a Variable Order All-Pass Filter and its Applications to Continuous-Time Pulse Processing

A THESIS

submitted by

**IMON MONDAL**

for the award of the degree

of

DOCTOR OF PHILOSOPHY

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY MADRAS.

December 2017

©2017, Imon Mondal. All rights reserved.

#### THESIS CERTIFICATE

This is to certify that the thesis titled Wideband Tunable True-Time-Delay Architecture Using a Variable Order All-Pass Filter and its Applications to Continuous-Time Pulse Processing, submitted by Imon Mondal, to the Indian Institute of Technology Madras, for the award of the degree of Doctor of Philosophy, is a bona fide record of the research work done by him under my supervision. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

Nagendra Krishnapura Associate Professor Dept. of Electrical Engineering IIT-Madras, Chennai 600 036

#### To Sharmistha

for being there through thick and thin

D

To my parents

for making me the person I am today

#### **ACKNOWLEDGEMENTS**

Reading the acknowledgment section in a thesis often used to be the interesting bit, partly because, it used to be the only section I could probably fully understand. But I never thought starting to write my own would be such a difficult job; not because I have nothing to acknowledge, but because I have too much to. And as usual gathering my thoughts before they all got jumbled up again took up some time.

The decision to apply for Ph.D. was a leap of faith, and the fact that I never thought of looking back was almost entirely due to my guide, Dr. Nagendra Krishnapura. I would like to express my heartfelt thanks for his guidance, unwavering support, encouragement and innumerable technical discussions that we had. I cannot over-emphasize his contribution in not only shaping my technical abilities, but also in changing the way I think about research. His vision to give us (his research students) an environment that fosters the freedom of individual thinking, while keeping track of everyone's progress is something that I will always be grateful for. As has often been said before, a research program at times can lead to blind alleys. During these times he knew exactly how to get me back on track – looking back I really cannot figure out how. His inputs and guidance while writing a research paper has been immense, and his constant endevour to strive for perfection is inspiring. He has been everything and more that I could have ever asked for in a mentor.

I would like to thank Prof. Shanthi Pavan, whose lectures on Active Filter Design and VLSI Data Conversion Circuits have been constant sources of reference for many years. Thanks for being an inspiring teacher and a researcher.

I would like to thank Prof. Shanthi Pavan, Dr. Nitin Chandrachoodan, Dr. Balakrishna Rao and Prof. Babu Viswanathan for their inputs as my doctoral committee members.

I would also like to thank Dr. Aniruddhan for his lectures on RFIC design, Prof. Pavan Hanumolu for his short course on serial links, Dr. Harish Krishnaswamy for his course on mm-wave circuits and Dr. Sudhakar Pamarti for the course on PLL design.

I would like to thank Mrs. Janaki and Mr. Saranath for quick resolution of administrative and maintenance hurdles.

My guide once told me "One probably learns more from his peers than from his guide." Even though I don't agree with him on this, but he is not too far off either, and for that I have my lab-mates to thank. I had heard somewhere, "You should always get into an argument. If you win, you gain confidence, and if you lose, you gain knowledge." If this is indeed true, I have learnt the most from Sumit. His technical rigor and propensity to question everything (sometimes to the verge of insanity), and an attitude of not accepting anything at face value has bailed me out multiple times. Thanks to Praveen for introducing me to the world of power amplifiers. Thanks to Abhishek Bhat for our discussions on VCOs. I would like to especially thank Sumit, Praveen and Abhishek for helping me review the thesis draft.

Thanks to Naga Rajesh for our discussions on delay lines and beamforming during the initial part of my work. My brief interaction with Pradeep Shettigar about interesting titbits of analog design has remained memorable. Thanks to Animesh and Ashwin for helping me with any issue with CAD tools. I would like to thank Debasish, Ashwin and Sujith for helping me with my PCB debug. Thanks to Debasish for teaching me basic soldering skills and showing me how not to panic even if I messed up a PCB. I would also like to thank Vallabh, Amrith, Ankesh, Radha, Chithra, Ananya, Aditya, Ashish, Ramakrishna, Abhishek Kumar, Rakshit, Aswani, Ravi Teja, Saravana, Aravind, Naresh, Madhavi, Naveen, Rohit and Priya for making this phase of my life a memorable one.

Among the many cherishable memories that I have made the one that will stand out is the attitude of each member in the lab to accept, discuss, debate and answer (seemingly) stupid questions over and over again. Among other things, this gave me the license to say "I don't know" without having to think twice about being judged right from the beginning, and I have everyone to thank for that.

"When you are stuck, prove that it's not meant to work, and you will find a solution more often than not." Thanks to my friend and ex-colleague, Varun Gupta for this suggestion that he once gave me. This has stood me in good stead time and again.

Thanks to Ashique for many interesting and counter-intuitive discussions over the years.

Through out this research journey my better half, Sharmistha, has always stood by my side. Not once did she ask me the dreaded question to a Ph.D. student, "When are you submitting your thesis?" Being my best friend, she understood this journey, and I cannot thank her enough. Long time back she had shown me the beauty of picturing a problem out of the equations embedded in a textbook. I had tried to inculcate the process, and needless to say, as an analog engineer it turned out to be very helpful.

My daughter, Biyas, has been a source of innocence and mischief in my life. I observe her absorb the surroundings and learn from it, and wish I could do so at the same rate too. Also because of her, I have found in myself a reservoir of patience that I never knew existed.

If, whatever happens to us in life is a matter of chance, then I have been blessed. But the luckiest thing to have happened to me was to be born to my loving parents. From my childhood my father taught me how to think, and my mother stood by everything in my life. They have been constant pillars of support on whom I have leaned on countless number of times. Thank you Ma! Thank you Baba!

#### **ABSTRACT**

Delay lines are integral parts of wideband beamforming systems and continuous-time equalizers. Ideal delay lines can only be implemented using lossless transmission lines terminated with its characteristic impedance at both ends. A lumped element realization using an all-pass filter having linear phase can approximate a delay line within its delay bandwidth. Higher the order, more the realizable delay. However, all-pass filter architectures reported in the literature are limited to first and second order filters which can realize limited delays within a given bandwidth. Larger delays are realized by cascading multiple units of the lower order filters. Cascading introduces parasitic poles, thus causing distortions in magnitude or delay characteristics. This limits the maximum number cascadable unit cells, in turn limiting the maximum achievable delay.

This thesis proposes an all-pass filter architecture that can be generalized to high orders, and can be realized using active circuits. Using this a compact true-time-delay element with a widely tunable delay and a large delay-bandwidth product is demonstrated. This is useful for beamforming and equalization in the lower GHz range where the use of LC or transmission line based solutions to realize large delays is infeasible. Coarse tuning of delay is realized by changing the filter's order while keeping the bandwidth constant and fine tuning is implemented by changing the filter's bandwidth utilizing the delay-bandwidth tradeoff. A test chip fabricated in 0.13 µm CMOS process demonstrates a delay tuning range of 250 ps-1.7 ns, over a bandwidth of 2 GHz, while maintaining a magnitude deviation of  $\pm 0.7$  dB. The filter achieves a delay-bandwidth product of 3.4 and a delay per unit area of  $5.8\,\mathrm{ns/mm^2}$ . The filter has a worst case noise figure of 20 dB, and -40 dB IM3 distortion for  $37 \,\mathrm{mV_{ppd}}$  inputs. The chip occupies an active area of  $0.6 \,\mathrm{mm^2}$ , and dissipates  $112 \,\mathrm{mW} - 364 \,\mathrm{mW}$  of power between its minimum and maximum delay settings. Computed radiation pattern with four antennas spaced by 7.5 cm (half wavelength at the maximum frequency of 20 GHz) shows  $\pm 90^{\circ}$ beam steering off broadside.

Exploiting the feasibility of large delay-bandwidth product of this architecture, a high order all-pass filter has been used to demonstrate true-time expansion and compres-

sion of narrow, wideband, finite width, continuous-time pulses. It is based on storing an input pulse as state-variables in a continuous-time filter whose delay exceeds the pulse duration, and, once the pulse is completely "inside" the filter, reducing or increasing its bandwidth. Expansion and compression enable processing and generation of high speed pulses using low speed circuits. The proposed method can be implemented on an IC unlike photonic or microwave implementations based on dispersive media. It is more accurate and less complex than IC implementations using a high frequency chirped VCO and on-chip group delay dispersion. It avoids high speed sampling and is more immune to jitter than sampling the signal on a capacitor array. Pulse expansion and compression by factors of 1.8× and 1.7× respectively are demonstrated in a 0.13 µm CMOS process. The prototype chip includes a filter whose bandwidth can be switched between 870 MHz and 472 MHz and circuitry to generate Gaussian/monopulse for testing. It occupies 1.6 mm² and consumes 370 mW.

### **Contents**

#### **ACKNOWLEDGEMENTS**

#### **ABSTRACT**

| 1 | Con  | tinuous-time Delay Elements for Broadband Signal Processing               |    |

|---|------|---------------------------------------------------------------------------|----|

|   | 1.1  | Introduction                                                              | 1  |

|   | 1.2  | Narrow band beamforming                                                   | 3  |

|   | 1.3  | Broadband beamforming                                                     | 5  |

|   | 1.4  | Integrated circuit delay elements in the literature and their limitations | 9  |

|   | 1.5  | Objective and organization of the thesis                                  | 13 |

|   | 1.6  | Contributions of the thesis                                               | 15 |

|   |      |                                                                           |    |

| 2 | Prop | posed Architecture of the Tunable All-pass Filter                         | 16 |

|   | 2.1  | Selection of $D(s)$                                                       | 19 |

|   | 2.2  | Quantifying the error in a real delay line                                | 20 |

|   |      | 2.2.1 Error due to in-band group delay ripple                             | 22 |

|   | 2.3  | Changing the delay                                                        | 24 |

|   | 2.4  | Delay tunability: fine tuning                                             | 28 |

|   |      | 2.4.1 Errors due to fine tuning                                           | 28 |

| 3 | Imp  | lementation of the Prototype All-pass Filter                              | 31 |

|   | 3.1  | Integrating capacitors                                                    | 31 |

|   | 3.2  | Transconductor                                                            | 33 |

| 7 |      | n Enhanced High Frequency Transconductor With On-Chip Tuned       | .,        |

|---|------|-------------------------------------------------------------------|-----------|

| 6 | Mea  | surement Results for Pulse Expansion and Compression Prototype    | <b>79</b> |

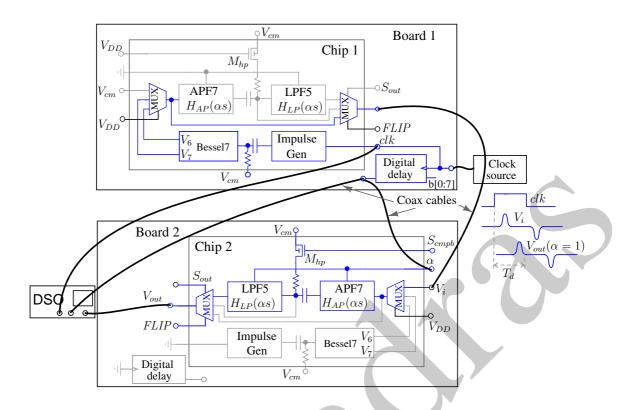

|   | 5.6  | Prototype chip architecture                                       | 77        |

|   | 5.5  | Pulse generator                                                   | 75        |

|   |      | 5.4.1 Summing taps                                                | 74        |

|   | 5.4  | Transconductor                                                    | 71        |

|   |      | 5.3.4 Effect of AC coupling between the two halves                | 67        |

|   |      | filter's bandwidth                                                | 66        |

|   |      | 5.3.3 Mismatch induced transients while dynamically switching the |           |

|   |      | 5.3.2 Filter used for pulse expansion and compression             | 65        |

|   |      | 5.3.1 Delay filter for signal storage                             | 64        |

|   | 5.3  | Filter with switched bandwidth                                    | 64        |

|   | 5.2  | Principle of pulse expansion/compression                          | 61        |

|   | 5.1  | Motivation                                                        | 59        |

|   | _    | tinuous-Time Filters                                              | 59        |

| 5 | Expa | ansion and Compression of Analog Pulses by Bandwidth Scaling of   |           |

| 4 | Mea  | surement Results of the Variable Delay All-Pass Filter            | 45        |

|   | 3.3  | Cinp arcintecture                                                 | 43        |

|   | 3.5  | 3.4.1 Design trade-offs: mismatch and noise                       | 41        |

|   | 3.4  | Distortion and noise                                              |           |

|   | 3.4  |                                                                   | 40        |

|   | 3.3  | Summing taps and gain tuning                                      | 38        |

|   |      | 3.2.2 Bandwidth tuning                                            | 36        |

|   |      | 3.2.1 Effect of device mismatch and $G_m$ sizing                  | 35        |

|   | 7.1   | Introduction                                                      | 88  |

|---|-------|-------------------------------------------------------------------|-----|

|   | 7.2   | Proposed architecture                                             | 89  |

|   | 7.3   | $G_N$ tracking $g_{ds}$                                           | 90  |

|   | 7.4   | Secondary effects and design trade-offs                           | 94  |

|   |       | 7.4.1 Results and discussion                                      | 95  |

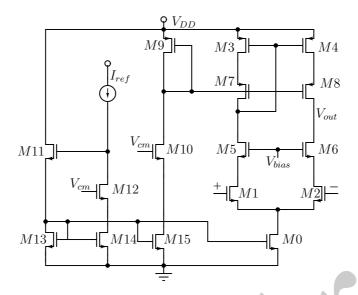

| 8 | Accı  | urate Constant Transconductance Generation Without Off-chip Com-  |     |

|   | pone  | ents                                                              | 98  |

|   | 8.1   | Motivation                                                        | 98  |

|   | 8.2   | Proposed achitecture                                              | 99  |

|   |       | 8.2.1 Generation of accurate on-chip resistance                   | 100 |

|   |       | 8.2.2 Generation of fixed transconductance                        | 101 |

|   |       | 8.2.3 Differential implementation                                 | 101 |

|   | 8.3   | Alternate compact implementation                                  | 104 |

|   | 8.4   | Simulation results and discussion                                 | 107 |

| • | ~     |                                                                   | 400 |

| 9 | Con   | clusion and Future Scope                                          | 109 |

|   | 9.1   | Suggestions for future work                                       | 110 |

| A | Mea   | surement of Noise Spectral Density                                | 113 |

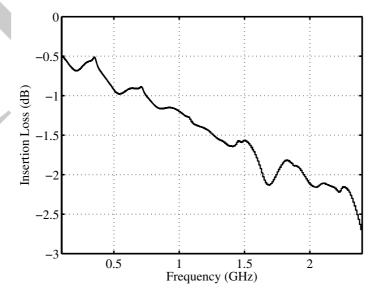

|   | A.1   | Measurment of insertion loss $(\alpha)$                           | 116 |

| В | Mul   | ti-variable Numerical Optimization for Fitting Measured and Simu- |     |

|   | lated | d Filter's Responses Using Space Mapping Technique                | 119 |

# **List of Figures**

| 1.1 | (a) Radiation pattern of an isotropic antenna. (b) Illustration of beam-   |    |

|-----|----------------------------------------------------------------------------|----|

|     | forming using a two antenna system. (c) Illustration of changing the       |    |

|     | beam direction using electronic delays                                     | 1  |

| 1.2 | Phase shift mimicking time delay for a sinusoidal signal                   | 3  |

| 1.3 | (a) Principle of narrow band beamforming using phase shifters for a        |    |

|     | two antenna system. (b) Realization of (a) using LO phase shifting.        | 3  |

| 1.4 | Applications of true-time-delay elements: (a) Beamforming by delay-        |    |

|     | ing and combining at RF[7]. (b) Beamforming at IF by delaying and          |    |

|     | combining after downconversion[9]. (c) Channel response equaliza-          |    |

|     | tion [8]                                                                   | 5  |

| 1.5 | Spatial filtering illustration of an $N+1$ element TTD beamformer for      |    |

|     | a broadband input. Delays are assigned to produce maximum(a) and           |    |

|     | minimum (b) at the output                                                  | 6  |

| 1.6 | (a) Normalized magnitude of the beamformed output for different scan-      |    |

| 1   | ning angles using a narrowband signal. (b) Polar representation of (a).    |    |

|     |                                                                            | 7  |

| 1.7 | (a) Normalized magnitude of the beamformed output for different in-        |    |

|     | cident angles using a broadband Gaussian monopulse input. (b) Polar        |    |

|     | representation of (a)                                                      | 8  |

| 1.8 | (a) An unit lattice filter cell. (b) Higher order all-pass filter realized |    |

|     | using cascades of unit lattice filters [12]                                | 10 |

| 1.9 | Active all-pass delay cells. (a) First order APF in [13] (b) First order   |    |

|     | APF in [14] (c) Second order APF in [15]. $C_L$ at the output of each      |    |

|     | delay cell is the output parasitic capacitance                             | 11 |

| 1.10 | Realization of large delays using cascade of first and second order de-          |    |

|------|----------------------------------------------------------------------------------|----|

|      | lay cells. $D_1(s)$ , $D_2(s)$ , $D_3(s)$ are first or second order polynomials. |    |

|      | Excess phase lag and magnitude droop caused by output parasitic ca-              |    |

|      | pacitance of each delay cell is modeled as $1/(1+s\tau_p)$                       | 12 |

| 1.11 | Scatter plot showing the magnitude deviations of reported delay lines            |    |

|      | with respect to delay (range)-bandwidth product. Red and blue markers            |    |

|      | represent active and passive realizations respectively                           | 12 |

| 2.1  | Forms of $LC$ ladder. (a) Odd order 'capacitor first' (b) Even order             |    |

|      | 'capacitor first' (c) Even order 'inductor first' (d) Odd order 'inductor        |    |

|      | first'                                                                           | 16 |

| 2.2  | All-pass filter architecture using singly terminated $LC$ ladder architec-       |    |

|      | tures of (a) Fig. 2.1(a, c) and (b) Fig. 2.1(b, d)                               | 18 |

| 2.3  | Singly terminated transmission line analogy for delay realization                | 19 |

| 2.4  | Comparison of group delay characteristics of a $9^{th}$ order Bessel filter to   |    |

|      | a $9^{th}$ order EGD filter having the same bandwidth                            | 20 |

| 2.5  | (a) Gaussian monopulse having FWHM $\approx$ 2 s. (b) Normalized spectrum        |    |

|      | of (a)                                                                           | 23 |

| 2.6  | Group delay characteristics of an EGD filter with change in order. (a)           |    |

|      | Constant delay. (b) Constant bandwidth                                           | 24 |

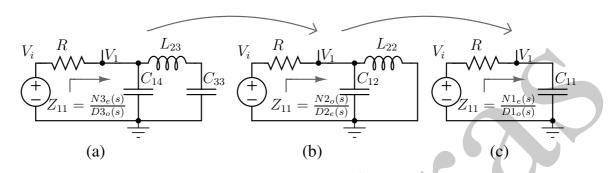

| 2.7  | LC ladder topologies for capacitor first architectures of Fig. 2.1 for (a)       |    |

|      | third order, (b) second order and (c) first order                                | 25 |

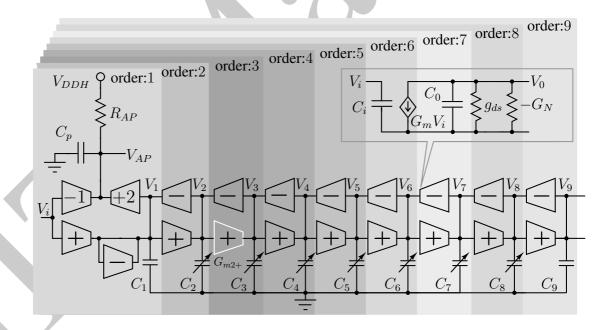

| 2.8  | Single ended representation of the fully differential variable order all-        |    |

|      | pass filter. Transconductors in each shaded box are turned on to config-         |    |

|      | ure the filter in the respective order. Inset: Single ended equivalent of        |    |

|      | the transconductor                                                               | 25 |

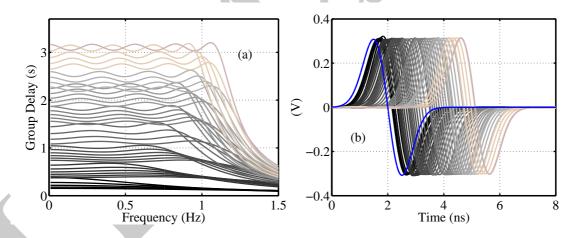

| 2.9  | (a) Group delay characteristics of APF with fine tuning. (b) Transient           |    |

|      | response of the APF with the monopulse input of Fig. 2.5                         | 28 |

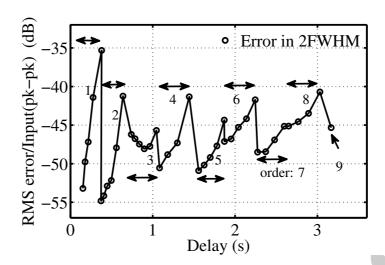

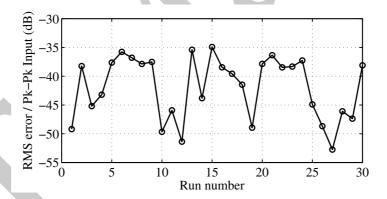

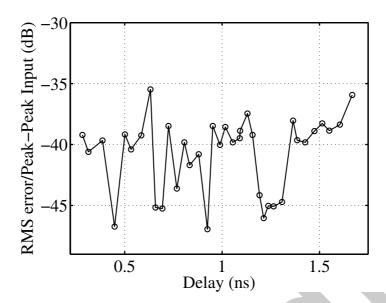

| 2.10 | Simulated rms error between the outputs and the delayed and scaled               |    |

|      | input of Fig. 2.9(b)                                                             | 29 |

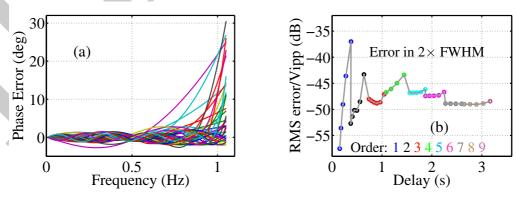

| 2.11       | (a) Simulated phase errors for the delay response of Fig. 2.9(a). (b)                   |      |

|------------|-----------------------------------------------------------------------------------------|------|

|            | RMS error in 2× FWHM of a Gaussian monopulse corresponding to                           |      |

|            | the phase error of (a)                                                                  | 29   |

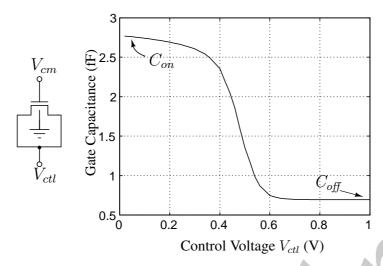

| 3.1        | nMOS gate capacitance versus control voltage                                            | 32   |

| 3.2        | (a) Utilization of differential signaling to generate virtual shorts at drain/so        | urce |

|            | terminals of the MOS transistors. (b) Layout arrangement of the struc-                  |      |

|            | ture [34]                                                                               | 32   |

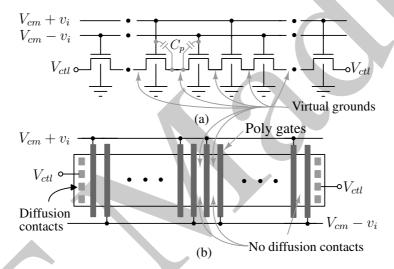

| 3.3        | (a) Transconductor, $G_m$ loaded with negative conductance $G_N$ . (b)                  |      |

|            | Principle of generating a transconductance, $G_N$ , to track the parasitic              |      |

|            | conductance, $g_{ds}$ . (c) Schematic representation of (a)                             | 34   |

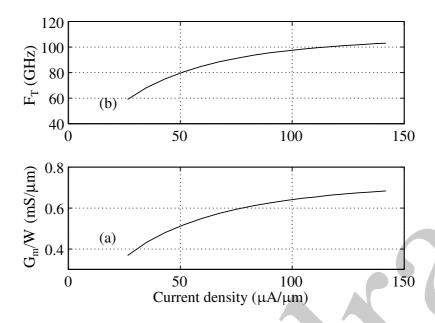

| 3.4        | (a) Dependence of $F_{\rm T}$ of the transconductor in Fig. 3.3 on current den-         |      |

|            | sities in a 0.13 $\mu m$ CMOS process. (b) $G_m$ of the transconductor per              |      |

|            | unit width corresponding the current densities of (a)                                   | 35   |

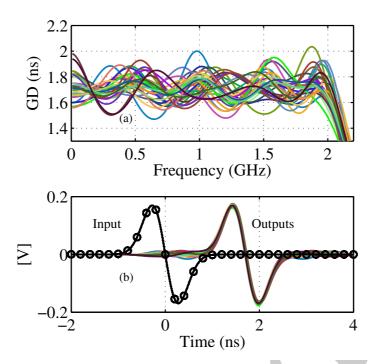

| 3.5        | (a) Group delay characteristics of the ninth order EGD filter with $\mathcal{G}_m$      |      |

|            | mismatch with standard deviation of 2%. (b) Computed transient re-                      |      |

|            | sponse of the EGD APF having delay characteristics of (a) when excited                  |      |

|            | with a monopulse having FWHM=1 ns                                                       | 36   |

| 3.6        | RMS error between the outputs and delayed and scaled input of Fig. 3.5(b).              | 36   |

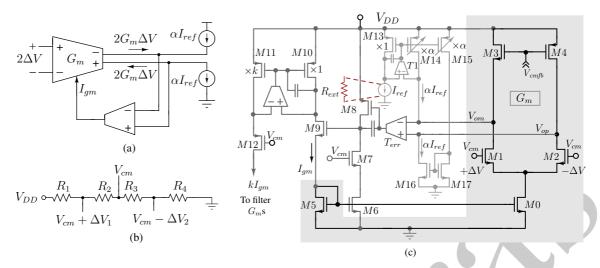

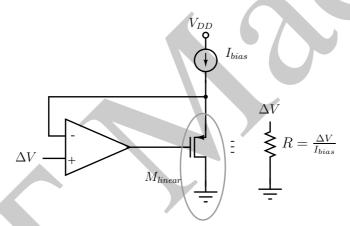

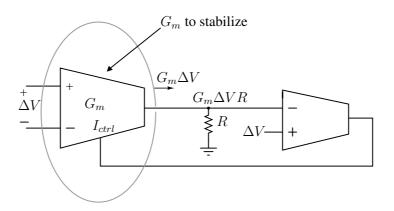

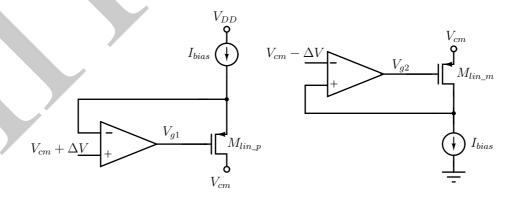

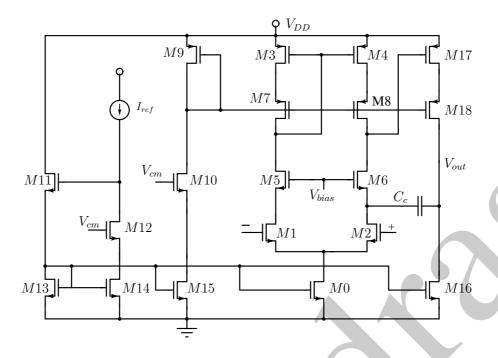

| 3.7        | (a) Principle demonstrating $G_m$ locking to $\alpha I_{ref}/(2\Delta V)$ . (b) Genera- |      |

|            | tion of $2\Delta V$ . (c) Schematic representation of (a)                               | 37   |

| 3.8        | Realization of the APF summer.                                                          | 39   |

| 3.9        | (a) Illustration of the effect of transconductor's mismatch on compo-                   |      |

|            | nent values. (b) Noise analysis using reciprocity. (c) Schematic of the                 |      |

|            | ninth order APF and the normalized signal swings at each state across                   |      |

|            | frequencies                                                                             | 41   |

| 3.10       | Simplified block diagram of the chip.                                                   | 43   |

| 3.11       | Output buffer architecture                                                              | 43   |

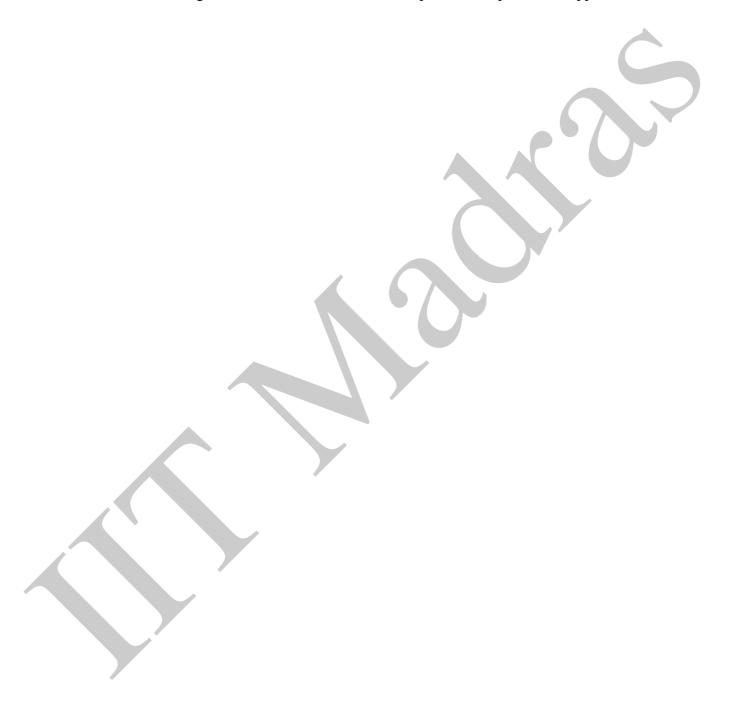

| <i>4</i> 1 | Chin micrograph and snapshot of the test hoard                                          | 45   |

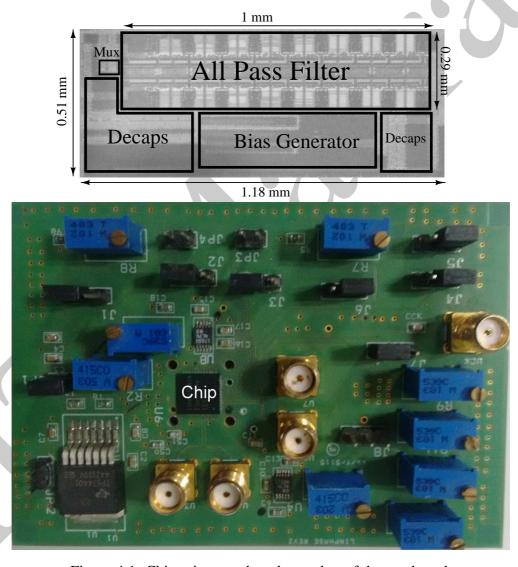

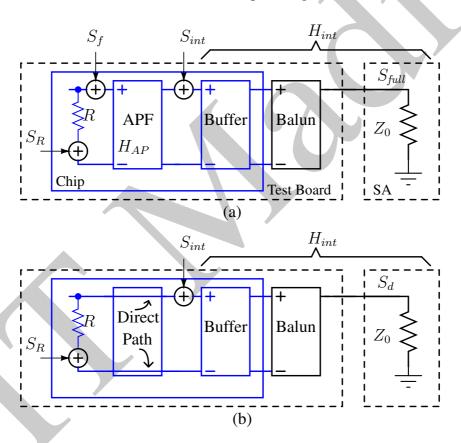

| 4.2  | Simplified measurement setup for characterizing the APF. VNA, SA              |    |

|------|-------------------------------------------------------------------------------|----|

|      | and DSO refer to vector network analyzer, spectrum analyzer, and dig-         |    |

|      | ital storage oscilloscope respectively.                                       | 46 |

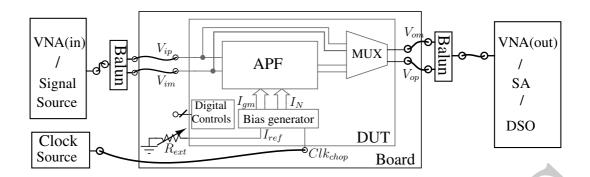

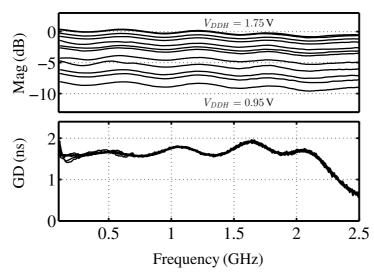

| 4.3  | Measured frequency response of the variable order APF with $V_{DD} =$         |    |

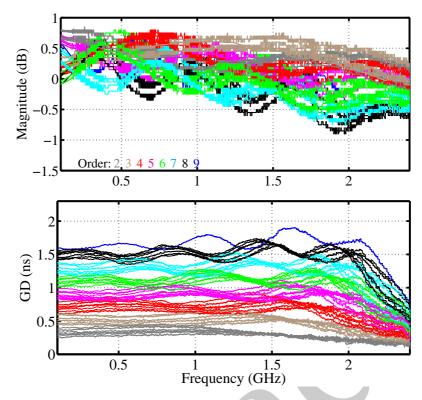

|      | 1.4 V for coarse delay settings                                               | 46 |

| 4.4  | Measured frequency response of the variable order APF with $V_{DD} =$         |    |

|      | 1.4 V for fine delay settings                                                 | 47 |

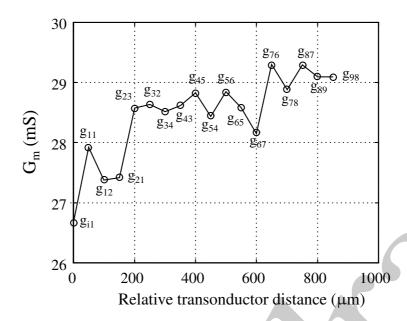

| 4.5  | Back-annotated $G_m$ s of the all-pass filter's transconductors with relative |    |

|      | distance from each other                                                      | 48 |

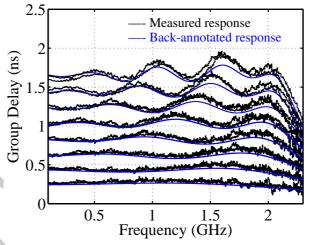

| 4.6  | Measured (from two chips) and back annotated group delay response             |    |

|      | for coarse delay settings                                                     | 48 |

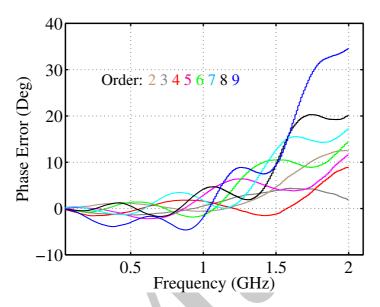

| 4.7  | Computed phase error from the AC response of Fig. 4.3                         | 49 |

| 4.8  | Computed rms error from the AC response of Fig. 4.4 with a Gaussian           |    |

|      | monopulse input using (2.30)                                                  | 50 |

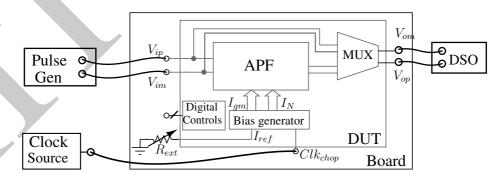

| 4.9  | Test setup for measuring response of the APF to transient inputs              | 50 |

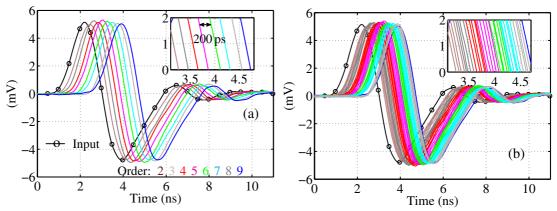

| 4.10 | Measured response to a to a 3.2 ns wide (FWHM) monopulse. (a) Coarse          |    |

|      | delay resolution. (b) Fine delay resolution                                   | 51 |

| 4.11 | (a) Transient plots (computed from AC response of Fig. 4.4) demon-            |    |

|      | strating monotonically varying true-time-delay when a monopulse of            |    |

|      | 1 ns width (FWHM) is fed to the filter. (b) Computed rms error between        |    |

|      | the outputs and delayed and scaled input of (a)                               | 51 |

| 4.12 | Ninth order APF gain and group delay frequency characteristics for dif-       |    |

|      | ferent summing tap voltages, $V_{DDH}$ . $V_{DD}$ set at 1.4 V                | 52 |

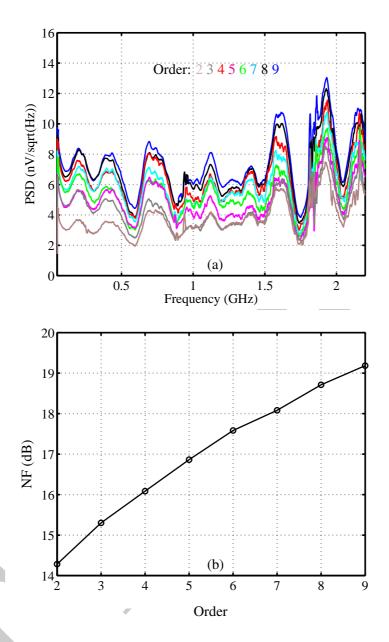

| 4.13 | Measured input referred noise spectral density and the integrated noise       |    |

|      | figure versus order                                                           | 53 |

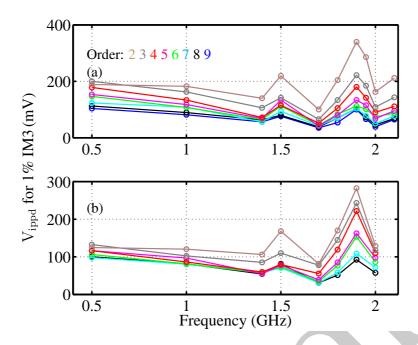

| 4.14 | Measured peak to peak differential input voltage for which IM3 falls          |    |

|      | 40 dB below the applied tones for (a) nominal delay setting, (b) in-          |    |

|      | creased delay setting with fine tuning                                        | 54 |

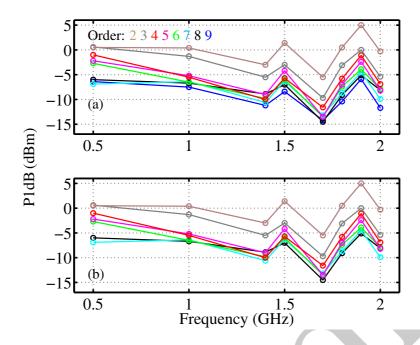

| 4.15 | setting, (b) increased delay setting with fine tuning                                                                                                                                                                          | 55 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.16 | (a) Model of the test setup used for computing radiation pattern. (b) Computed normalized radiation pattern for a four element array with uniform spacing of 7.5 cm ( $\lambda_{\rm fmax}/2$ ) using a monopulse of 1 ns FWHM. | 55 |

| 4.17 | Scatter plot showing the magnitude deviations of the reported delay lines (active and passive) including this work with respect to delay (range)-                                                                              |    |

| ~ 1  | bandwidth product.                                                                                                                                                                                                             | 56 |

| 5.1  | (a) Slowing down a signal by storing the samples at high speed and reading at low speed [44], (b) Slowing down a continuous-time signal [45]                                                                                   | 59 |

| 5.2  | (a) State-space model of a filter, (b) $G_m$ - $C$ realization of (a); Values shown on conductances and transconductances are multipliers of a cer-                                                                            |    |

| 5.2  | tain unit transconductance $G_{m0}$                                                                                                                                                                                            | 61 |

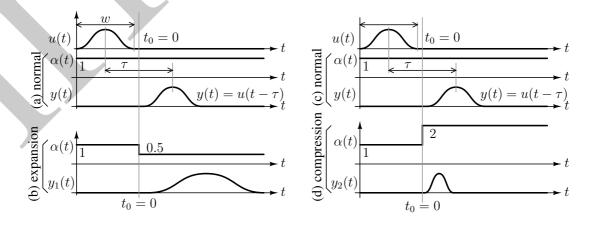

| 5.3  | (a) and (c) Normal operation of a continuous-time filter, (b) Pulse expansion by dynamically reducing $\alpha$ , (d) Pulse compression by dynamically increasing $\alpha$                                                      | 62 |

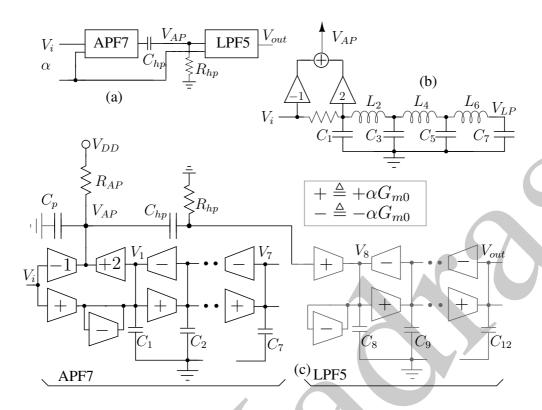

| 5.4  | (a) Cascade of an all-pass and a low pass filter. (b) APF7 using an $LC$ ladder. (c) $G_m$ -C realization of APF7 and LPF5                                                                                                     | 64 |

| 5.5  | Illustration of switching a first order filter between (a) High bandwidth, and (b) Low bandwidth modes. Mismatches between the filter halves                                                                                   |    |

| 5.6  | cause disturbance to the states while switching                                                                                                                                                                                | 66 |

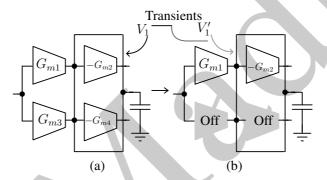

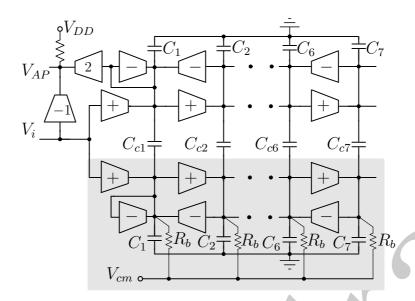

|      | enth order $G_m$ – $C$ filter                                                                                                                                                                                                  | 67 |

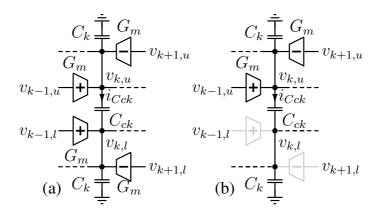

| 5.7  | $k^{th}$ stage of the filter: (a) With both halves turned on, (b) With the lower half turned off. $R_b$ in Fig. 5.6 is assumed to be very high and is                                                                          |    |

|      | not shown here                                                                                                                                                                                                                 | 68 |

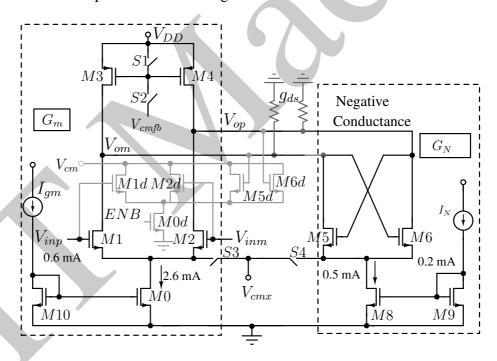

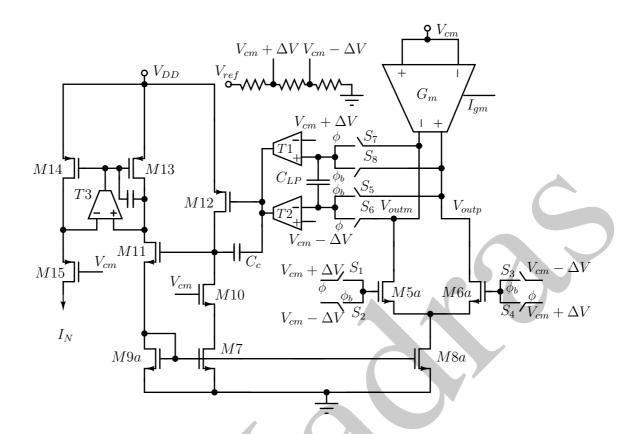

| 5.8  | Schematic of the transconductor used in APF7                                                                                                                                                                                   | 71 |

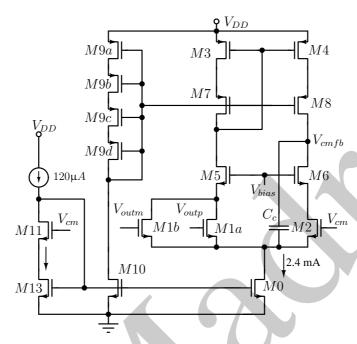

| 5.9  | Common mode feedback circuit for the transconductor in Fig. 5.8                                                                                                                                                                | 72 |

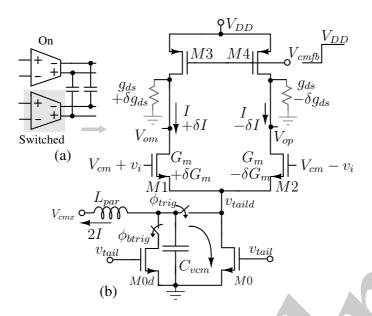

| 5.10 | (a) Switched transconductor in the ladder filter. (b) Unbalanced transcon-                                                                 |          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | ductor while switching (negative conductance not shown)                                                                                    | 73       |

| 5.11 | Simulated bias current settling time of the transconductor of Fig. 5.8.                                                                    | 74       |

| 5.12 | (a) Simplified schematic of the all-pass taps. (b) Architecture of a summing tap unit                                                      | 74       |

| 5.13 | (a) Gaussian and monopulse generation architecture. (b) Schematic of the impulse generator circuit and illustration of impulse generation. | 76       |

| 5.14 | Simulated differential outputs of the impulse, Gaussian pulse and monopuls generators                                                      | se<br>76 |

| 5.15 | Simplified block diagram of the chip                                                                                                       | 77       |

| 5.16 | Output buffer schematic                                                                                                                    | 78       |

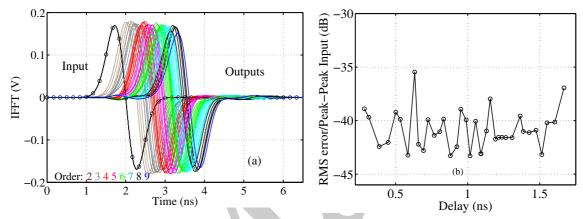

| 6.1  | (a) Chip photograph and (b) snapshot of the test board                                                                                     | 79       |

| 6.2  | Magnitude and group delay of (a) all-pass filter (APF7), and (b) the total                                                                 |          |

|      | filter chain (APF7+LPF5) for both bandwidth settings                                                                                       | 80       |

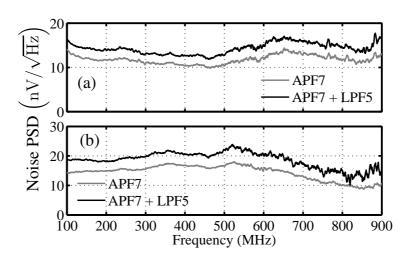

| 6.3  | Measured input noise spectral density for APF7 and APF7 + LPF5 for                                                                         |          |

|      | (a) high bandwidth and (b) low bandwidth mode                                                                                              | 81       |

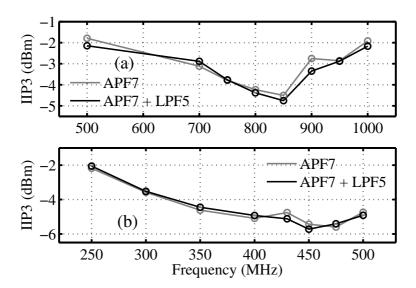

| 6.4  | Measured IIP3 with $50\Omega$ reference resistance for the APF7 and APF7 + LPF                                                             | F5       |

|      | for (a) high bandwidth and (b) low bandwidth mode                                                                                          | 82       |

| 6.5  | Simplified test set up for pulse expansion and compression                                                                                 | 83       |

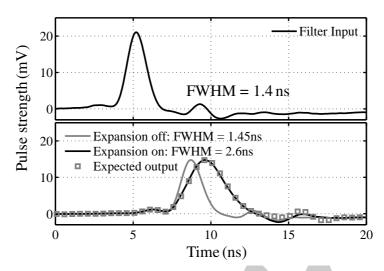

| 6.6  | Demonstration of pulse expansion with Gaussian input pulse with FWHM                                                                       |          |

|      | of 1.4 ns                                                                                                                                  | 84       |

| 6.7  | Demonstration of pulse expansion with a monopulse input with FWHM                                                                          |          |

|      | of 2.4 ns                                                                                                                                  | 84       |

| 6.8  | Compression of a Gaussian input pulse with FWHM = 2 ns                                                                                     | 85       |

| 6.9  | Compression of a monopulse input with FWHM = 3.2 ns                                                                                        | 85       |

| 7.1  | Schematic representation of Nauta transconductor [29]                                                                                      | 89       |

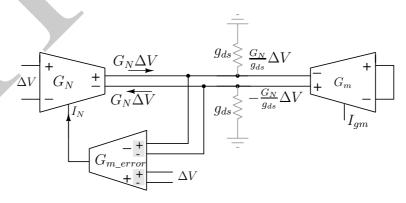

| 7.2  | (a): Transconductor $G_m$ loaded with negative conductance $G_N$ . (b):                   |     |

|------|-------------------------------------------------------------------------------------------|-----|

|      | Symbolic representation of (a)                                                            | 90  |

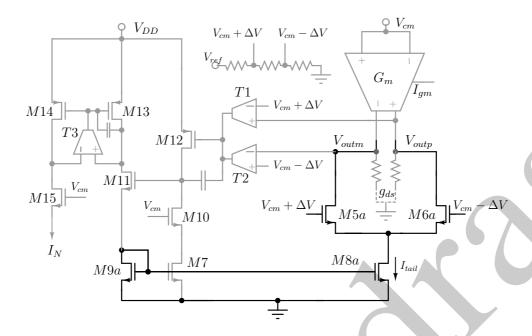

| 7.3  | Common mode feedback circuit                                                              | 91  |

| 7.4  | Principle of conductance tracking by a transconductor                                     | 91  |

| 7.5  | Schematic of transconductance generation circuit to track the output conductance $g_{ds}$ | 92  |

| 7.6  | Schematic of the transconductors $T1, T2, T3$ used in Fig. 7.5                            | 93  |

| 7.7  | Inclusion of chopping to eliminate the effect of offsets in $G_m$ and $G_N$ .             | 94  |

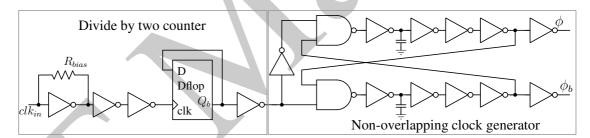

| 7.8  | Schematic for generation of chopping clock                                                | 94  |

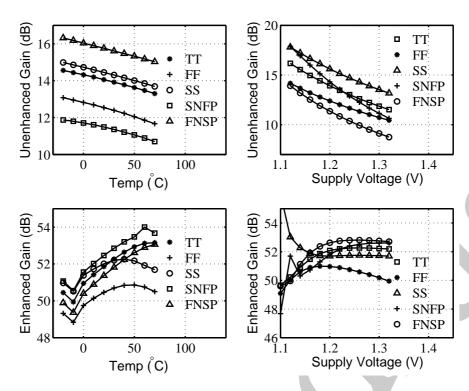

| 7.9  | Transconductor gain variation with temperature and supply voltage across                  |     |

|      | process corners with chopping enabled                                                     | 96  |

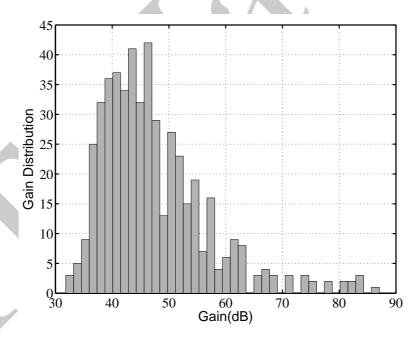

| 7.10 | Transconductor gain distribution with mismatch over 500 Monte-Carlo                       |     |

|      | runs with gain enhancement post chopping                                                  | 96  |

| 8.1  | Block diagram demonstrating principle of operation for generating con-                    |     |

| 0.1  | stant on-chip resistance                                                                  | 100 |

| 8.2  | Block diagram demonstrating principle of $G_m$ tracking $1/R$                             | 101 |

| 8.3  | Generation of constant resistance for differential operation                              | 101 |

| 8.4  | Schematic representation of the two stage opamp used in Fig. 8.3                          | 102 |

| 8.5  | Generation and routing of bias current for fixed transconductance                         | 103 |

| 8.6  | Schematic of the transconductors $T1, T2, T3$ used in Fig. 8.5                            | 104 |

| 8.7  | Principle demonstrating $G_m$ locking to $I_{ref}/\Delta V$                               | 104 |

| 8.8  | Transconductance generation circuit to track $I_{ref}/\Delta V$                           | 105 |

| 8.9  | Inclusion of chopping to eliminate offset of $M1, 4. \ldots$                              | 106 |

| 8.10 | Simulation schematic of the transconductor whose bias current is gen-                     |     |

|      | erated in Fig. 8.9.                                                                       | 107 |

| 8.11 | Simulated variation of $G_{m M1a,M2a}$ of Fig. 8.10 with temperature                      | 107 |

| 8.12 | Simulated variation of $G_{m M1a,M2a}$ of Fig. 8.10 with supply voltage.  | 108 |

|------|---------------------------------------------------------------------------|-----|

| A.1  | Noise contributors in the test setup (a) with filter path enabled and (b) |     |

|      | with direct path enabled                                                  | 113 |

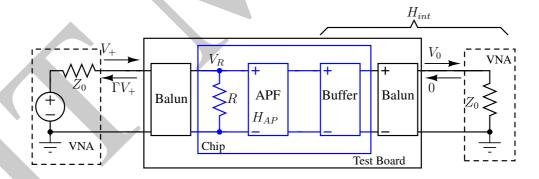

| A.2  | Test setup for evaluating $ H_{AP}H_{int} $                               | 114 |

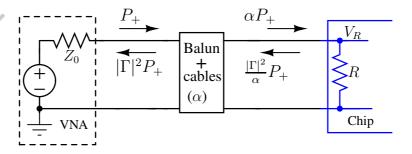

| A.3  | Effect of path loss on power transfer                                     | 115 |

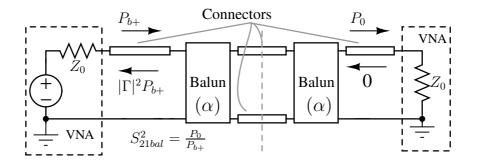

| A.4  | Setup for measuring balun loss under                                      | 117 |

| A.5  | Insertion loss of the balun and the associated connectors                 | 117 |

| B.1  | Schematic of the all-pass filter of Fig. 2.8 with mismatches in the tran- |     |

|      | conductors (other than the summing taps).                                 | 120 |

## **List of Tables**

| 2.1 | Values of integrating capacitors in Fig. 2.8 for all orders normalized to |    |

|-----|---------------------------------------------------------------------------|----|

|     | the minimum capacitance, $C_1$                                            | 27 |

| 4.1 | Comparison of the proposed all-pass filter with the delay element archi-  |    |

|     | tectures                                                                  | 57 |

| 4.2 | Performance summary of the chip                                           | 58 |

| 6.1 | Table comparing expansion/compression architectures                       | 86 |

| 6.2 | Performance summary of the test chip                                      | 86 |

| 7.1 | Comparison of the proposed transconductor (with and without negative      |    |

|     | conductance cancellation) with the state of the art negative conductance  |    |

|     | cancellation based architecture                                           | 97 |

#### **Chapter 1**

# Continuous-time Delay Elements for Broadband Signal Processing

#### 1.1 Introduction

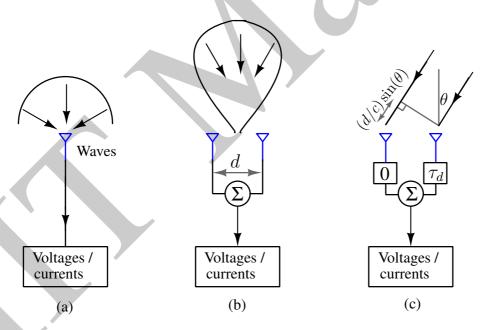

Wireless communication systems use antennas to propagate information through space. When a single antenna is used, the radiation is spread out broadly around the antenna. Fig. 1.1(a) shows an example of an antenna with a radially symmetric radiation pattern. However, there are many applications which demand directional communication where

Figure 1.1: (a) Radiation pattern of an isotropic antenna. (b) Illustration of beamforming using a two antenna system. (c) Illustration of changing the beam direction using electronic delays.

it is required to focus the radiated energy in the desired direction. Using two antennas results in a more focussed beam pattern as shown in Fig. 1.1(b). The radiation pattern from each of the individual antennas constructively interfere at a direction normal to the antenna array and produce a beam maximum, and the radiation intensity rolls off at

angles further from the normal. The beam direction of this antenna array can be pointed to an arbitrary angle  $\theta$ , by applying an appropriate electronic time delay,  $\tau_d$ , to the signal arriving at one of the antennas. This is illustrated in Fig. 1.1(c). The beam rotates to an angle  $\theta$  such that the total path delay of the signal through each of the antenna paths is identical, which implies  $(d/c)\sin(\theta)=\tau_d$ , where d is the spacing between the antennas, and c is the speed of light. This spatial selectivity in the angle of reception is akin to filtering a signal based on the direction of arrival. Such arrangements of two or more antennas are called phased array antennas, and the electronic circuitry controlling the spatial filtering are called beamforming systems.

As a consequence of spatial filtering, phased array systems have the following advantages.

- The antenna array of a phased array transmitter performs a vector summation of the signals in the electromagnetic (EM) domain, and adds in magnitude in the direction of transmission. However, the uncorrelated noise from each of the individual paths adds in power. This increases the signal-to-noise ratio (SNR) of the transmitted and the received signal, thus relaxing the noise specifications of the receiver.

- Thanks to spatial filtering a phased array receiver is able to attenuate strong nearby blocker signals from any unwanted direction while continuing to communicate with a transmitter in another direction. This relaxes the linearity requirements of the circuitry succeeding the beamformer.

The above advantages have made beamforming systems an attractive option for applications like radar and through wall imaging. Also, in the near future the roll out of the fifth generation (5G) wireless standards having carrier frequencies in the range of 28–30 GHz will enable the integration of multiple antennas [1] in a single cell phone, thus paving the way for beamforming systems to infiltrate the world of millions of handheld devices.

From the simplistic illustration of the phased array system in Fig. 1.1, it is evident that the the core of the technique is the electronically controlled variable delay element which is responsible for steering the beam in the direction of choice. The first integrated circuit phased array beamformer was reported in [2] in 2004. There has been a plethora of publications in this domain ever since using variety of delay elements. The following section reviews some of the most widely used beamforming architectures. The rest of the document will concentrate on beamforming receivers unless otherwise mentioned.

#### 1.2 Narrow band beamforming

$$s(t) \rightarrow \tau \rightarrow s(t - \tau)$$

$$\sin(\omega_c t) \rightarrow \tau \rightarrow \sin(\omega_c t - \omega_c \tau)$$

$$\sin(\omega_c t) \rightarrow \Phi \rightarrow \sin(\omega_c t - \Phi)$$

$$\boxed{\text{Make } \Phi = \omega_c \tau}$$

Figure 1.2: Phase shift mimicking time delay for a sinusoidal signal.

A time delay of  $\tau$  to a narrow band signal around a center frequency  $\omega_c/(2\pi)$  can be approximately modeled as shifting of phase of the sinusoidal carrier by  $\omega_c\tau$ . This is shown in Fig. 1.2. Because phase shifters are easier to design than true-time-delay elements in CMOS technologies, architectures based on narrow band phase shifters have become popular. To do this the baseband signal of interest is modulated with a high

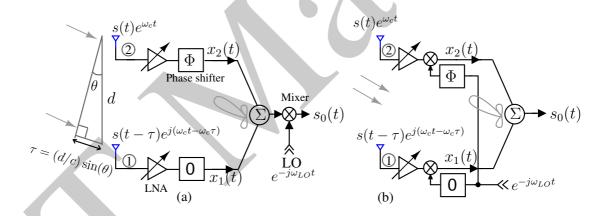

Figure 1.3: (a) Principle of narrow band beamforming using phase shifters for a two antenna system. (b) Realization of (a) using LO phase shifting.

frequency carrier. For most of the reported literature the baseband bandwidth is  $\leq 1\%$  of the carrier frequency [3]. The narrow band nature of the up-converted signal enables the architecture to mimic a time delay with the phase shift of the sinusoidal carrier. The individual outputs are summed to achieve spatial filtering and down-converted back to baseband through a mixer. The underlying assumption behind a narrowband implementation is that, the baseband signal remains *almost* constant across the time delay of interest (about one cycle of the carrier). A conceptual illustration of the same is shown in Fig. 1.3(a) for a two antenna system. d represents the antenna spacing,  $\theta$  the direction of beam arrival, s(t) the baseband signal,  $\omega_c$  the angular frequency of the modulating

carrier,  $\Phi$  the incremental phase shift in the signal path, and  $\omega_{LO}$  the the angular frequency of the LO. For a signal arriving at an angle  $\theta$  from the normal to the antenna array, the delay in arrival experienced by the waveform incident on channel 1, with respect to channel 2, is  $\tau = (d/c)\sin(\theta)$ . Assuming that the phase shifters do not affect the baseband envelope of the high frequency carrier, the the signals in each channel are expressed as

$$x_1(t) = s(t - \tau)e^{-j\omega_c\tau}e^{j(\omega_c - \omega_{LO})t} \quad \text{and} \quad x_2(t) = s(t)e^{-j\Phi}e^{j(\omega_c - \omega_{LO})t}$$

(1.1)

The beamformed signal at the output of the summer can be expressed as

$$s_0(t) = (s(t)e^{-j\Phi} + s(t-\tau)e^{-j\omega_c\tau})e^{j(\omega_c - \omega_{LO}t)}$$

(1.2)

Choosing  $\Phi = \omega_c \tau = \omega_c (d/c) \sin(\theta)$ , and assuming  $s(t) \approx s(t-\tau)$ , yields a maximum at the output (2s(t)) indicating the direction of beam arrival. Since there is a one-to-one relation between  $\theta$  and  $\Phi$  for  $\theta = [-90^o, +90^o]$ ,  $\Phi$  uniquely represents the direction of arrival of the incoming beam.

Fig. 1.3(b) phase shifts the local oscillator (LO) signal [3]. Mixing, phase shifting and summing yields

$$s_0(t) = (s(t)e^{-j\Phi} + s(t-\tau)e^{-j\omega_c\tau})e^{j(\omega_c - \omega_{LO}t)}$$

(1.3)

Again, for narrow band applications  $s(t) \approx s(t - \tau)$ . Thus, if  $\Phi = \omega_c \tau$  the beam maximum (2s(t)) is detected at an angle  $\Phi$  which represents the direction of arrival.

However for both Fig. 1.3(a,b), if the carrier frequency changes from  $\omega_c$ , the angle of observation of beam maximum also deviates from  $\Phi$ . This phenomenon of frequency dependence of the observed beam direction is called beam squinting [4], which eventually limits the bandwidth of the baseband signal.

Also, as the bandwidth of the baseband signal becomes a significant fraction of  $\omega_c/(2\pi)$ ,  $s(t-\tau)$  can no longer be approximated as s(t). This makes observed maximum of the detected beam direction-dependent. If such a system is used for wireless reception of digital signals, this error will lead to degradation in the error vector magnitudes (EVM)[3], especially for standards demanding dense constellation points. This

is likely to make narrow band beamforming challenging for 5G standards, where the baseband signal bandwidth is expected to be around 1 GHz for a carrier frequency of 28 GHz [1]. However, if the phase shifters are replaced by true-time-delays, both beam squinting and EVM degradation are reduced.

In applications like ground penetrating radars or through wall imaging considerable high frequency signal attenuation [5][6] makes modulated carrier based narrowband band beamforming unattractive. Because of these reasons, exploring wideband efficient true-time-delay architectures is of interest.

#### 1.3 Broadband beamforming

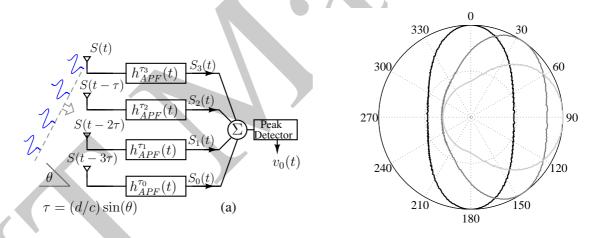

Figure 1.4: Applications of true-time-delay elements: (a) Beamforming by delaying and combining at RF [7]. (b) Beamforming at IF by delaying and combining after downconversion [9]. (c) Channel response equalization [8].

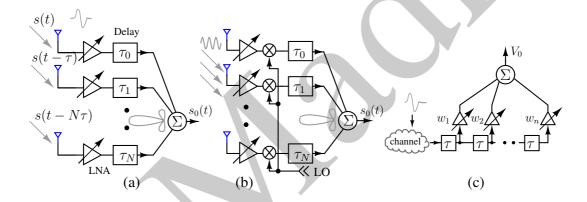

From the discussions in Section 1.2 it is evident that using true-time-delays instead of phase shifters can reduce the challenges like bandwidth limitations and EVM degradation for wideband signals. Fig. 1.4(a) [7] shows an N+1 channel beamforming architecture where the signal received by each element of an antenna array is delayed and combined to achieve directional selectivity.  $\tau$  is the arrival delay of the signal s(t) with respect to its neighbor and  $\tau_{i|0->N}$  are the variable electronic delays in each channel. The beamformed output can be expressed as

$$s_0(t) = \sum_{i=0}^{N} s(t - i\tau - \tau_i)$$

(1.4)

To produce a beam maximum, the extra path delay  $i\tau$  with which the signal arrives

Figure 1.5: Spatial filtering illustration of an N+1 element TTD beamformer for a broadband input. Delays are assigned to produce maximum (a) and minimum (b) at the output.

at the  $i^{th}$  channel is compensated by a frequency independent electronic delay,  $\tau_i = (N-i)\tau$ , to produce (N+1)s(t). The output, (N+1)s(t) is independent of frequency implying that there is no beam squinting. This is shown in Fig. 1.5(a). To detect an incoming beam at an angle  $90^o$  from the normal, and thus support full spatial coverage, the maximum required delay is given by the time taken by the EM wave to traverse the antenna array along its axis, i.e.,

$$\tau_{max} = N(d/c) \tag{1.5}$$

For a given delay range of  $\tau_{max} < N(d/c)$ , the range of angles to which the beam can be steered is given by  $[-\theta_{max}, \theta_{max}]$ , where  $\theta_{max} = \sin^{-1}(\tau_{max}(c/d))$ .

For effective spatial filtering the beam pattern shown in Fig. 1.1(b) should be as narrow as possible. For an N+1 element beamformer the beam patterns of narrowband signals has a maximum of (N+1)s(t), and a minimum of 0. The minimum occurs when the signals from different paths destructively interfere with each other. The beamformed

output for a sinusoidal signal with carrier frequency of  $\omega_c$  incident normal to the antenna array is expressed as

$$s_0(t) = 1 + e^{-j\omega_c \tau_d} + e^{-j2\omega_c \tau_d} + \dots + e^{-jN\omega_c \tau_d}$$

(1.6)

where  $\tau_d$  is the unit delay of the true-time-delay element. The scanning angle  $\theta$  corresponding to the delay  $\tau_d$  can be expressed as  $\theta = \sin^{-1}((c/d)\tau_d)$ . This implies

$$|s_0(t)| = \left| \frac{\sin(\omega_c(N+1)(d/c)\sin(\theta)/2)}{\sin(\omega_c(d/c)\sin(\theta)/2)} \right|$$

(1.7)

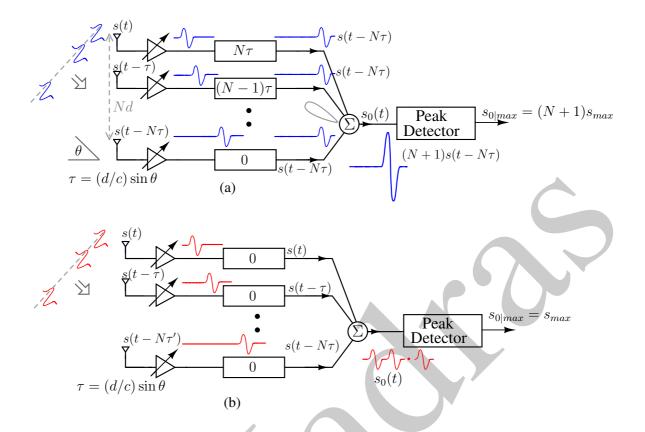

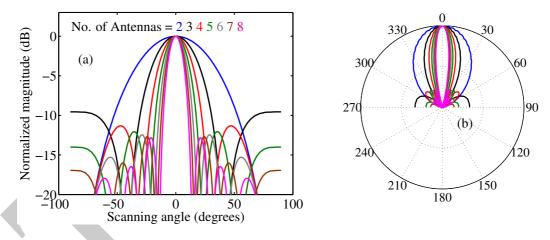

Fig. 1.6(a) shows the beamformed output for a sinusoidal signal with antenna spacing at  $\lambda_{\text{fmax}}/2$  for different number of antennas, where  $\lambda_{\text{fmax}}$  is the wavelength of the EM wave of the frequency  $\omega_c$ . Fig. 1.6(b) is the polar representation (a). From (1.7) and Fig. 1.6(a, b) it is evident that the beam patterns become sharper with increasing number of antenna elements.

Figure 1.6: (a) Normalized magnitude of the beamformed output for different scanning angles using a narrowband signal. (b) Polar representation of (a).

Beam patterns using wideband pulses depend on the type of pulses and their widths with respect to the time taken by the EM wave to traverse the antenna array. It can be verified with numerical simulations that increasing the number of antennas leads to sharper broadband radiation patterns. This is shown in Fig. 1.7 for a Gaussian monopulse having width 1 = 2(d/c)

The intuition behind this can be illustrated from Fig. 1.5. When the time delay

<sup>&</sup>lt;sup>1</sup>Width of a Gaussian monopulse is defined as the time interval between half its maximum and minimum values. For a more elaborate discussion on the choice of the pulse the reader is referred to Section 2.2.

Figure 1.7: (a) Normalized magnitude of the beamformed output for different incident angles using a broadband Gaussian monopulse input. (b) Polar representation of (a).

elements are adjusted to align the input waveforms in time, the output has a maximum value of  $(N+1)\times s(t)_{max}$ . This is shown in Fig. 1.5(a). Conversely, when the time delays are set such that none of the pulses in any of the channels overlap on each other, the output has maximum of  $s(t)_{max}$ . This is shown in Fig. 1.5(b). The ratio of the maximum and minimum of the beam pattern is N+1. The beam width becomes smaller with the increase in the number of antennas in the array. As beam patterns become narrower, beam steering with smaller resolutions becomes necessary to ensure full spatial coverage between  $\pm \theta_{max}$ . This requires finer granularity in the delays of the delay elements.

The spatial filtering, resolution and the SNR of these beamforming systems improve as the number of antenna elements increases. Its implication from (1.5) is an increase in the required maximum delay. All the above analysis and conclusions are also valid for modulated carrier based communication systems after downconversion as shown in Fig. 1.4(b) [9]. Fig. 1.4(c) shows a continuous-time equalizer. Here again, the longer the impulse response of the channel, the longer must be the delay span of the equalizer. The group delay has to be uniform over the signal bandwidth. Continuous-time wideband pipelined ADCs such as the one reported in [10] requires 1.5 times the clock cycle delays to compensate for the time delay between the continuous-time analog input and the continuous-time DAC output for calculating residues at each stage. Since the input is wideband, the delay element also needs to have a wide bandwidth.

Therefore, for beamforming with a large number of antennas or for realizing large-span equalizers, or even in some modern continuous time piplelined ADCs, there is a need to realize delay elements which maintain a large, flat group delay over a wide bandwidth. In other words, true-time-delay elements with a *large delay-bandwidth product* (DBW) are necessary.

# 1.4 Integrated circuit delay elements in the literature and their limitations

A true-time-delay element imparting a delay  $T_d$  has a transfer function of  $e^{-sT_d}$ , which has linear phase and constant magnitude characteristics. This is realizable only using ideal transmission lines (or passive realization of the same) terminated with the characteristic impedance [7]. For applications targeted at lower GHz frequencies like ground penetrating radars, wall imaging systems [5], or beamforming at baseband [9] in millimeter-wave communication, the length of the transmission lines or size of the inductors is impractically large for integrated circuit realizations. Moreover, the insertion loss of transmission lines increase with their lengths and the the inductor losses increase with increase in their sizes. This causes roll-off of the magnitude characteristics, which eventually limit the operating frequency of the delay lines [7][11].

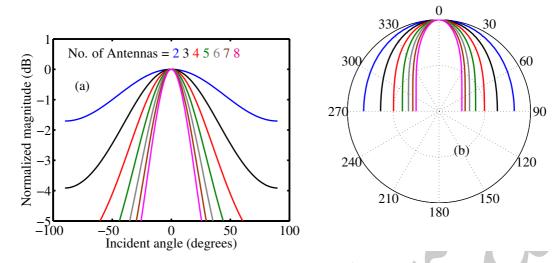

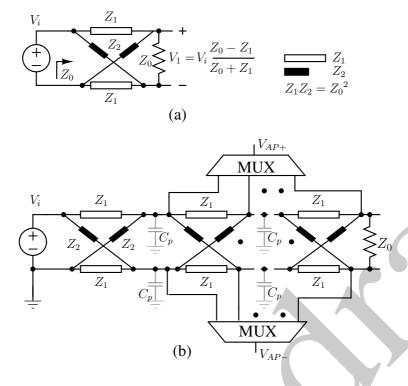

All-pass filters (APFs) having linear phase over a range of frequencies have unity magnitude response and a flat delay response over the same frequency range. Lattice APF [12] is a passive element based filter architecture which is systematically synthesizable. Synthesis of a lattice filter based APF is shown in Fig. 1.8. Fig. 1.8(a) shows an unit cell of the filter. If the impedances  $Z_1$  and  $Z_2$ , are related with the termination impedance  $Z_0$  as  $Z_0^2 = Z_1 Z_2$ , it can be shown [12] that the output voltage  $V_1 = V_0 \frac{Z_0 - Z_1}{Z_0 + Z_1}$ . Let  $Z_1$  and  $Z_2$  be a capacitor and an inductor having impedances 1/sC and sL respectively such that  $L/C = R^2$ . For  $Z_0 = R$ ,  $V_1 = \frac{1 - sCR}{1 + sCR}$ , which is a first order all-pass transfer function, having magnitude response of unity and a nominal delay of 2RC. Also, since the input impedance of this unit cell is equal to  $Z_0$  [12], multiple such blocks can be cascaded to realize longer delays. Variable delays can be generated by using a multiplexer (MUX) as shown in Fig. 1.8(b). Multiplexing stages adds output parasitic capacitance at each stage (due to the input capacitance of the MUX). This de-

Figure 1.8: (a) An unit lattice filter cell. (b) Higher order all-pass filter realized using cascades of unit lattice filters [12].

grades the all-pass transfer function by introducing magnitude and delay droops. This degradation becomes more severe as the number of stages increases, eventually limiting the maximum number of stages that can be cascaded. Along with with the insertion loss of the inductors, this eventually limits the maximum realizable delay.

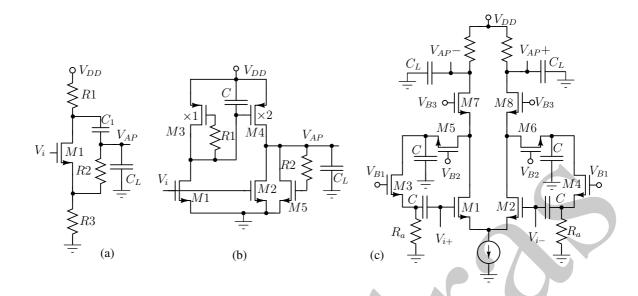

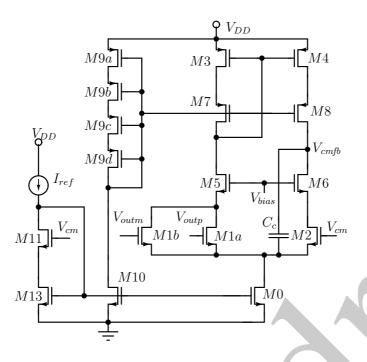

Inductorless, active-RC implementations of long time constants can lead to compact realizations which can be tiled to form large arrays. In the literature, active true-time-delays are implemented using all-pass filters (APFs) [14][13] which have a transfer function of the form  $H_{AP}(s) = D(-s)/D(s)$ , where D(s) is a polynomial of s. An APF has a flat magnitude response, and twice the delay of the corresponding lowpass filter 1/D(s), and is a better alternative for realizing a true-time-delay element. For realizing a true-time-delay, D(s) can be chosen to be some polynomial approximation to the ideal exponential  $e^{sT_d}$ , such as those used for Bessel or equiripple group delay (EGD) filters. The higher the order, the better the approximation. To realize long delays over wide bandwidths, i.e. a large delay-bandwidth product, a high order filter is necessary. But unlike lowpass filters which can be systematically synthesized for any order, APF architectures in the literature are mostly limited to first and second orders. Examples of these are shown in Fig. 1.9 ([13, 15, 14]). In the absence of parasitic poles

Figure 1.9: Active all-pass delay cells. (a) First order APF in [13] (b) First order APF in [14] (c) Second order APF in [15].  $C_L$  at the output of each delay cell is the output parasitic capacitance.

Fig. 1.9(a) and (b) have first order all-pass transfer function of the form

$$H_{AP1}(s) = \frac{1 - s/\omega_1}{1 + s/\omega_1} \tag{1.8}$$

and Fig. 1.9(c) has a second order transfer function of the form

$$H_{AP2}(s) = \frac{1 - s/(\omega_2 Q) + (s/\omega_2)^2}{1 + s/(\omega_2 Q) + (s/\omega_2)^2}$$

(1.9)

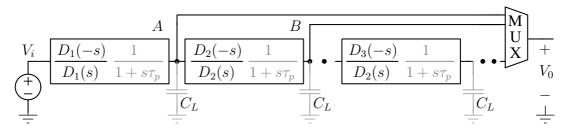

where  $\omega_1$ ,  $\omega_2$ , and Q are functions of the circuit components. Both (1.8) and (1.9) have unity magnitude response and their phase response can be tailored to provide linear phase by modifying  $\omega_1$ ,  $\omega_2$ , and Q, by adjusting the component values. However, the parasitic capacitances at the output (and at some internal node) of each of these architectures introduce one or two additional parasitic poles which introduce magnitude and phase deviations. Higher order APFs are realized using a cascade of first or second order filters and their outputs multiplexed to realize a variable delay as shown in Fig. 1.10. Cascading and multiplexing of stages adds to the output parasitic capacitance and lowers the parasitic pole frequency, worsening the roll-off and limiting the bandwidth of the system. Techniques like inductive peaking are used to counter the phase roll-off [14], but this causes in-band gain deviations for different delay settings [14]. This limits the number of cells which can be cascaded, and consequently the maximum achievable delay.

Figure 1.10: Realization of large delays using cascade of first and second order delay cells.  $D_1(s)$ ,  $D_2(s)$ ,  $D_3(s)$  are first or second order polynomials. Excess phase lag and magnitude droop caused by output parasitic capacitance of each delay cell is modeled as  $1/(1+s\tau_p)$ .

Hayahara's structure [16] is an example of an active filter based higher order APF which can be systematically synthesized without cascading unit cells. However, like the lattice filter based architecture, this too suffers from the effect of parasitic capacitances to ground.

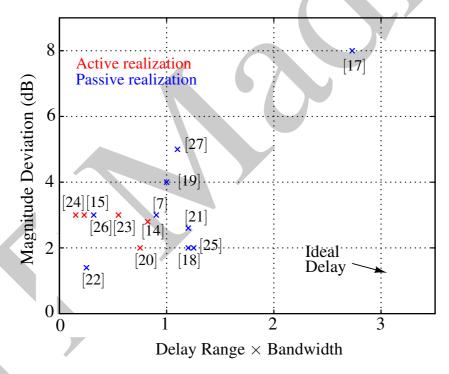

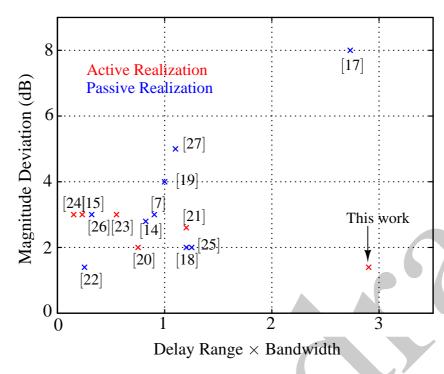

Figure 1.11: Scatter plot showing the magnitude deviations of reported delay lines with respect to delay (range)-bandwidth product. Red and blue markers represent active and passive realizations respectively.

To summarize, efficacy of delay lines (both passive and active) is limited by the magnitude deviations they incur while realizing large delay-bandwidth products. The trade-off between large delay-bandwidth product and magnitude flatness can be captured by plotting the gain variation of the reported delay lines in literature versus delay bandwidth product. This is shown in Fig. 1.11. This is a scatter plot of the *measured* magnitude deviation versus the *measured* delay-bandwidth product of most of the re-

ported<sup>2</sup> monolithic implementations of the true-time-delay cells in IEEE $\mathbb{R}$ . The points marked in red and blue represent active and passive realizations respectively. An ideal delay line with a large delay and flat magnitude response will be positioned far right on the x axis in Fig. 1.11. However, it can be observed that, an attempt to achieve higher delay has invariably led to larger magnitude variations.

#### 1.5 Objective and organization of the thesis

The previous sections discussed about the necessity and architectures of the true-time-delay elements reported in literature. From these discussions it was concluded that even though delay lines realizing large delays over wide bandwidths are necessary for many applications like wideband beamforming, equalization, and even modern continuous-time pipelined ADCs, realization of large delay-bandwidth products have hit a bottle-neck due to the distortion of magnitude and/or delay characteristics of the delay lines due to effects of insertion loss and interface parasitic effects arising out of cascading of multiple stages. Expectedly, these effects are more prominent in the architectures realizing higher delay-bandwidth products. Active implementations of delay lines trying to equalize these artifacts and realize compact area efficient solutions using unit delay cells have been handicapped by the interface parasitic capacitances of these units. Keeping these design issues in the forefront, one of the objectives of this thesis is to break the trade-off between realization of large delays and compromising on the flatness of the magnitude response and realize a delay line architecture to validate the objective.

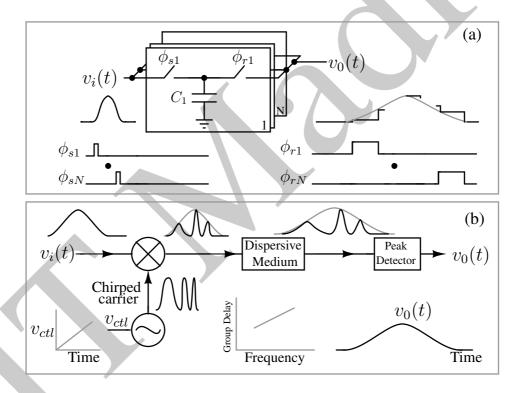

In the latter half the proposed delay line architecture has been used in an application of expansion and compression of continuous-time analog pulses hitherto not reported in literature. This is an IC realization of the method proposed in [28] using the proposed delay line with the objective of realizing a monolithic solution and reducing the chip area of the pulse expansion and compression architectures.

Chapter 2 proposes the all-pass filter architecture used to realize the true-time-delay line. An analysis of the efficacy of the architecture for maintaining flat magnitude

<sup>&</sup>lt;sup>2</sup>To the best of our knowledge this diagram contains all the reported architectures of TTD implementations which contain measured data for both group delay and magnitude till Sep. 2017. Some implementations of the same architecture for different applications have been omitted. [11] has been left out due to its extremely large gain droop of 35 dB.

response regardless of the delay is presented. An analysis technique to quantify the error due to distortion of the AC response of the delay line is presented.

Chapter 3 discusses the design and circuit details of the all-pass filter introduced in Chapter 2. Methods to realize a range of delays from the single active delay line are introduced. Several design trade-offs between noise, mismatch and distortions are discussed.

Chapter 4 presents the measurement results of the delay line architecture introduced thus far. The proposed delay line is benchmarked with the state-of-the art architectures reported in literature and its efficacy validated.

Chapter 5 discusses the motivation behind realizing expansion and compression of continuous-time analog pulses, and the architectures reported in literature. The usefulness of the proposed delay line in realizing an area efficient IC implementation of pulse expansion/compression is discussed. The design challenges, techniques to mitigate them, and circuit details are presented.

Chapter 6 presents the measurement results demonstrating expansion and compression of continuous-time wideband analog pulses. The proposed solution is benchmarked with the state-of-the-art architectures realizing pulse expansion and compression and its efficacy in reducing the chip area validated.

The building block of the all-pass filter which is used as a delay line in this work is a gain-enhanced high frequency transconductor. This is proposed in Chapter 7. The design details, theoretical analysis of its operating conditions and simulation results of the architecture are presented.

Chapter 8 presents two architectures for realizing constant (process, voltage and temperature independent) transconductance for the transconductors realizing the all-pass filters.

Chapter 9 concludes the thesis and puts forth suggestions for future work.

#### 1.6 Contributions of the thesis

This thesis presents an architecture for realizing large tunable delays over a wide bandwidth using variable order all-pass filter and uses the proposed architecture to demonstrate true-time expansion and compression of continuous-time, high frequency, analog pulses. The contributions of the thesis are summarized below.

- Active all-pass filters reported in literature have been used to realize delay lines. But their usefulness has not been exploited to the fullest due to the use of cascade of unit cells which introduces interface artifacts. This thesis proposes and realizes an architecture of a delay line based on an all-pass filter topology which does not use cascade of delay cells to realize large tunable delays. It does not have any unwanted interfaces distorting the AC response of the delay line except for the final output node. The topology is systematically synthesizable using well known LC ladder synthesis techniques and can be extended to realize large delays without compromising on magnitude response. Measurement results of a prototype variable order all-pass filter validates the architecture.

- A comprehensive analysis of the effect of distortion of the AC repose of a delay line on a wideband input signal is presented. It is shown that the error energy between the input and the output of a wideband pulse travelling through a real delay line depends on the square of phase error and the fourth power of the magnitude deviation of the real delay line, and is not directly related to the group delay flatness. This quantifies the amount of acceptable phase deviations as per the requirement of any application and quantifies the importance of magnitude deviation in contributing to pulse shape distortion. This is in contrary to the reported literature on the delay lines which mostly concentrate on maintaining group delay flatness and not the magnitude response.

- In the latter half of the thesis the proposed all-pass filter is used to demonstrate expansion and compression of continuous-time wideband analog pulses based on the technique proposed in [28]. Due to the compactness of the all-pass filter architecture it was possible to realize this in almost three times less chip area than the state-of-the art architectures reported in literature, which mostly used narrow band techniques based on chirped carrier based modulation and dispersive delay lines to realize pulse expansion and compression.

- The building block of the all-pass filter is a high frequency transconductor without any internal nodes. This is needed to avoid excess phase lags necessary to avoid unwanted peaking in the AC response. The transconductor uses negative conductance to cancel the parasitic conductance of a single stage differential amplifier. This thesis proposes a technique to ensure that the cancellation takes place automatically across process, voltage and temperature variations.

- Transconductances of the transconductors in active filters need to be invariant of the process, voltage and temperature variations. This thesis presents a solution of the same which is independent of the model of the transistor and is based on negative feedback and the linear behaviour of a non-linear element within a range of voltages.

#### Chapter 2

### **Proposed Architecture of the Tunable All-pass Filter**

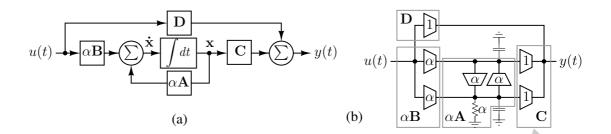

Realization of large delay-bandwidth product by cascading multiple delay cells leads to undesired parasitic poles, which causes phase and magnitude deviations eventually imposing an upper limit to the number of cells that can be cascaded. This limits the maximum realizable delay-bandwidth product for an architecture. In contrast, if a filter topology has just as many nodes as its order, all parasitic capacitors can be absorbed into the integrating capacitors of the filter [29]. This will not distort the frequency response. Such architectures for realizing lowpass filters are widely used in literature [29][30]. However, due to the absence of a systematic design procedure for realizing higher order all-pass filters, these filter design techniques have not been utilized.

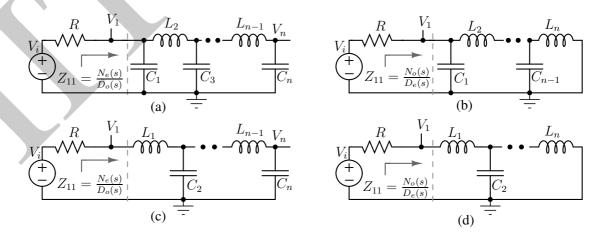

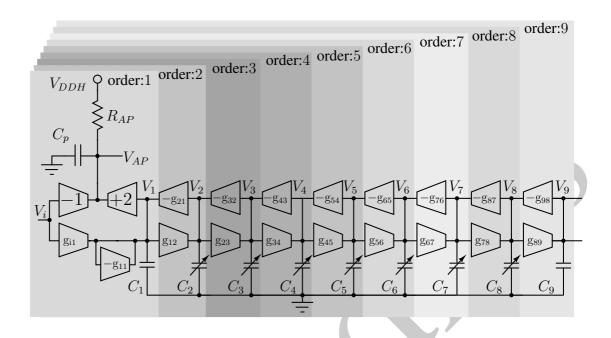

This chapter introduces a tunable delay variable order APF architecture based on a singly terminated ladder filter which can be systematically synthesized for any transfer function. It can realized using a transconductor with no internal nodes. This allows realization of large delay-bandwidth product without the need to cascade multiple units or multiplex high frequency analog signals. Consider the singly terminated LC ladder

Figure 2.1: Forms of LC ladder. (a) Odd order 'capacitor first' (b) Even order 'capacitor first' (c) Even order 'inductor first' (d) Odd order 'inductor first'.

in Fig. 2.1(a) or Fig. 2.1(c) where the termination resistor R is the only dissipative element. The driving point impedance,  $Z_{11}(s)$ , looking into the lossless LC network can be represented as [31]

$$Z_{11}(s) = \frac{N_e(s)}{D_o(s)} \tag{2.1}$$

where  $N_e(s)$  and  $D_o(s)$  are polynomials with only even and odd powers of s respectively. For example,

$$Z_{11}(s) = \frac{s^2 C_1 L_2 + 1}{s^3 C_1 L_2 C_3 + s(C_1 + C_3)}$$

(2.2)

for a third order filter having configuration of Fig. 2.1(a), or

$$Z_{11}(s) = \frac{s^2 L_1 C_2 + 1}{s C_2} \tag{2.3}$$

for a second order filter having configuration of Fig. 2.1(c). For filters like those in Fig. 2.1(b), or Fig. 2.1(d) the driving point impedance,  $Z_{11}(s)$ , looking into the lossless LC network can be represented as [31]

$$Z_{11}(s) = \frac{N_o(s)}{D_e(s)} \tag{2.4}$$

where  $N_o(s)$  and  $D_e(s)$  are polynomials with only odd and even powers of s respectively

such as

$$Z_{11}(s) = \frac{sL_2}{s^2L_2C_1 + 1}$$

(2.5)

for a second order filter having configuration of Fig. 2.1(b), or

$$Z_{11}(s) = \frac{s^3 L_3 C_2 + s(L_1 + L_3)}{s^2 L_3 C_2 + 1}$$

(2.6)

for a second order filter having configuration of Fig. 2.1(d). In Fig. 2.1(a, c) the node voltage,  $V_1(s)$  can be represented as

$$V_1(s) = V_i \frac{Z_{11}(s)}{Z_{11}(s) + R}$$

(2.7)

i.e.

$$V_1(s) = V_i \frac{N_e(s)}{N_e(s) + RD_o(s)}$$

(2.8)

i.e.

$$V_1(s) = \frac{V_i}{2} \frac{N_e(s) - RD_o(s)}{N_e(s) + RD_o(s)} + \frac{V_i}{2}$$

(2.9)

Let

$$H_{AP}(s) = \frac{N_e(s) - RD_o(s)}{N_e(s) + RD_o(s)}$$

(2.10)

which implies

$$V_1(s) = \frac{V_i}{2} H_{AP}(s) + \frac{V_i}{2}$$

(2.11)

Since  $N_e(s)$  and  $D_o(s)$  contain only even and odd powers of s respectively,  $N_e(j\omega)$  is purely real and  $D_o(j\omega)$  is purely imaginary. Therefore,

$$|H_{AP}(j\omega)| = \left| \frac{N_e(j\omega) - RD_o(j\omega)}{N_e(j\omega) + RD_o(j\omega)} \right| = 1.$$

(2.12)

Proceeding as above it can be shown that

$$H_{AP}(j\omega) = \frac{N_o(j\omega) - RD_e(j\omega)}{N_o(j\omega) + RD_e(j\omega)}$$

(2.13)

for the configurations of Fig. 2.1(b, d).

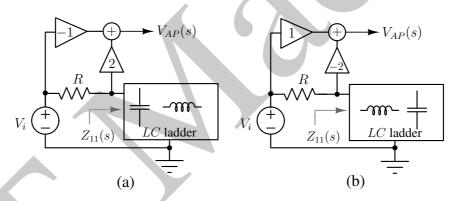

Figure 2.2: All-pass filter architecture using singly terminated LC ladder architectures of (a) Fig. 2.1(a, c) and (b) Fig. 2.1(b, d)

Thus  $H_{AP}(s)$  is an all-pass transfer function. Denoting  $V_{AP}(s) = H_{AP}(s)V_i$  and rearranging (2.11), results in  $V_{AP}(s) = 2V_1(s) - V_i$ . Thus, a weighted summation of the input voltage  $V_i$  and the first node voltage of the filter  $V_1$  results in an all-pass function. This is shown in Fig. 2.2(a). Note that, if  $N_e(j\omega) + RD_o(j\omega)$  has linear phase (constant group delay) within the signal bandwidth, so will  $H_{AP}(j\omega)$ . Thus, if the components of the LC ladder in Fig. 2.2(a) are chosen such that  $V_n/V_i$  is a Bessel lowpass filter,  $H_{AP}(s)$  will be a filter with a constant delay within the signal band, and unit magnitude across all frequencies. Since the order of the filter is the same as that of the singly terminated ladder it can be made arbitrarily large. This opens up possibilities for realizing arbitrarily large delays without compromising the magnitude flatness.

Fig. 2.2(a, b) summarize the proposed all-pass filter realizations. The expressions for the all-pass outputs are as follows.  $V_{AP}(s) = 2V_1(s) - V_i(s)$  for LC ladders in Fig. 2.1(a, c), and  $V_{AP}(s) = V_i(s) - 2V_1(s)$  for LC ladders in Fig. 2.1(b, d). Also note that the lowpass transfer function 1/D(s) can also be simultaneously realized by tapping the last state-variable of the LC ladder (capacitor voltage or inductor current, e.g.  $V_n$  in Fig. 2.1(a)).

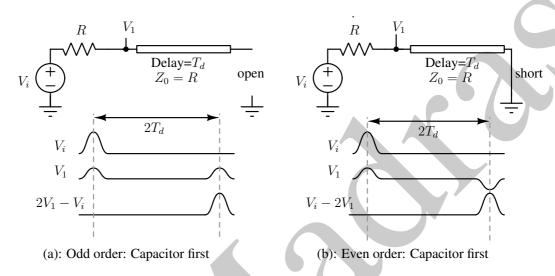

Figure 2.3: Singly terminated transmission line analogy for delay realization.

This all-pass structure can also be understood by analogy with transmission lines. This is shown in Fig. 2.3. The singly terminated ladders in Fig. 2.1(a, c) are equivalent to a transmission line terminated by an open circuit (Fig. 2.3(a)) and those in Fig. 2.1(b, d) are equivalent to a transmission line terminated by a short circuit (Fig. 2.3(b)). Voltage  $V_1$  at the input of the line consists of the attenuated version of input pulse ( $V_i/2$ ) and the reflected pulse which arrives  $2T_d$  later, where  $T_d$  is the one-way delay of the transmission line. The reflected pulse is in phase with the input with an open circuit termination and out of phase with the input with a short circuit termination. Thus taking  $2V_1 - V_i$  in Fig. 2.3(a) or  $V_i - 2V_1$  in Fig. 2.3(b) cancels the incident pulse and leaves only the reflected pulse, which is the input pulse delayed by  $2T_d$ .

# **2.1** Selection of D(s)

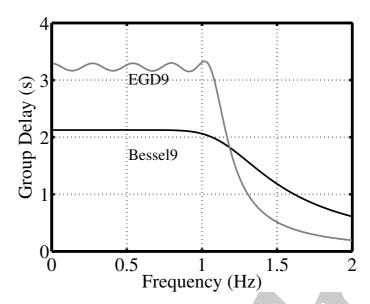

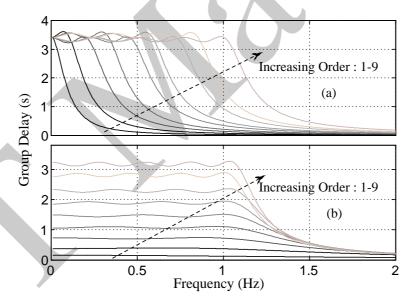

One of the ways to realize flat group delay for  $H_{AP}(s) = D(-s)/D(s)$  is to ensure that 1/D(s) has the characteristics of a Bessel filter. Fig. 2.4 shows the group delay of ninth-order Bessel and equiripple group delay (EGD) all-pass filters. Since EGD filters

Figure 2.4: Comparison of group delay characteristics of a  $9^{th}$  order Bessel filter to a  $9^{th}$  order EGD filter having the same bandwidth.

have higher group delay than their Bessel counterparts [31] for the same bandwidth, the former has been chosen for this implementation. The effect of the in-band group delay ripple is explained in following section.

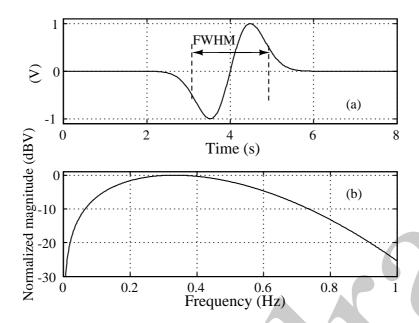

# 2.2 Quantifying the error in a real delay line

An ideal delay line offering a delay  $T_d$  to an input  $v_i(t)$  has an output  $v_i(t-T_d)$ . In the frequency domain the output can be represented as  $V_i(j\omega)e^{-j\omega T_d}$ , where  $V_i(j\omega)$  is the Fourier transform of  $v_i(t)$ . The output of a real delay line of Fig. 2.2 is  $H_{AP}(j\omega)V_i(j\omega)$ . For a real delay line

$$H_{AP}(j\omega) = |H_{AP}(j\omega)|e^{-j\omega T_d - j\phi_e(\omega)}$$

(2.14)

where  $\phi_e(\omega)$  is the phase deviation of the real delay line from its ideal counterpart. The error  $V_e(j\omega)$  is quantified as

$$V_e(j\omega) = H_{AP}(j\omega)V_i(j\omega) - V_i(j\omega)e^{-j\omega T_d}.$$

(2.15)

Using Parseval's theorem the error energy can be expressed as

$$\int_{-\infty}^{\infty} (v_0(t) - v_i(t - T_d))^2 dt = \frac{1}{2\pi} \int_{-\infty}^{\infty} |V_e(j\omega)|^2 d\omega$$

(2.16)

where  $v_0(t)$  is the time domain output. A high frequency broadband pulse has most of its energy concentrated within a narrow time duration. If  $T_p$  represents this duration of interest an rms error can be obtained by modifying (2.16) as

$$E_{rms} = \sqrt{\frac{1}{T_p} \int_{-\infty}^{\infty} (v_0(t) - v_i(t - T_d))^2 dt} = \sqrt{\frac{1}{2\pi T_p} \int_{-\infty}^{\infty} |V_e(j\omega)|^2 d\omega}.$$

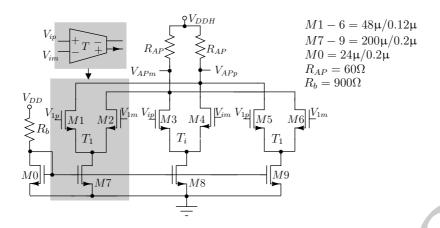

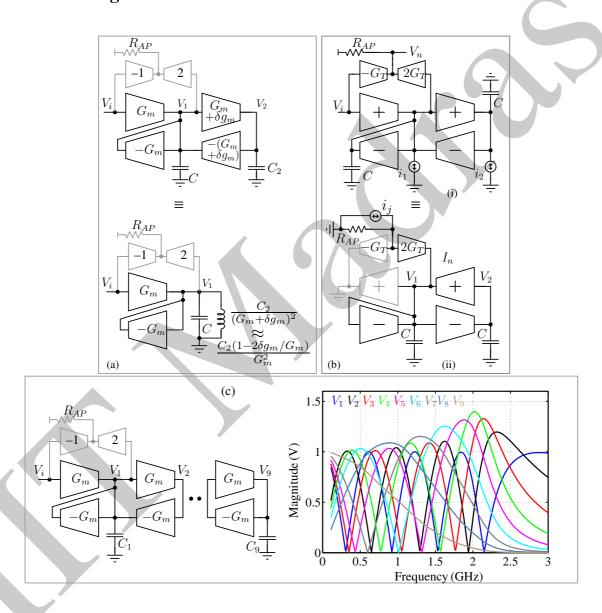

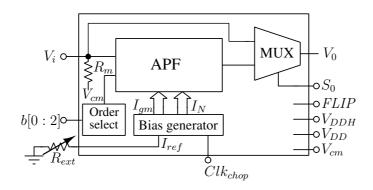

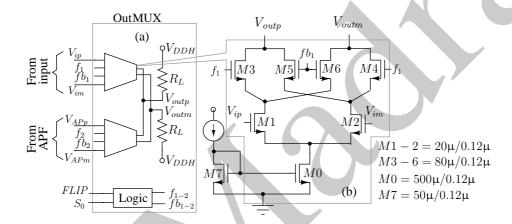

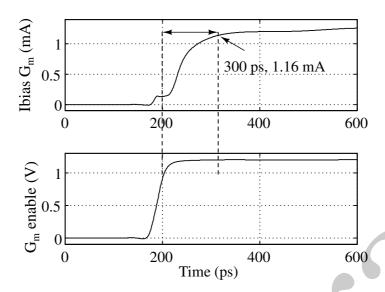

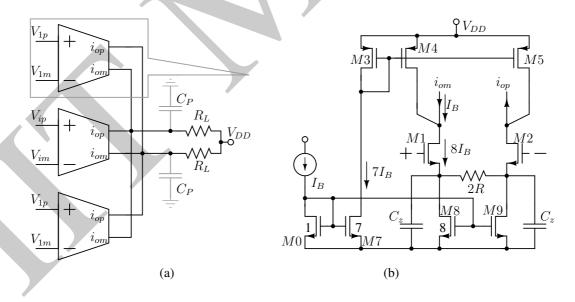

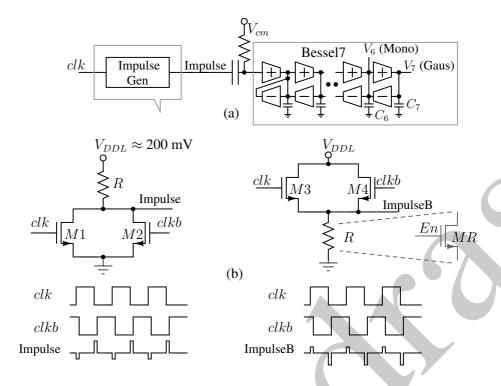

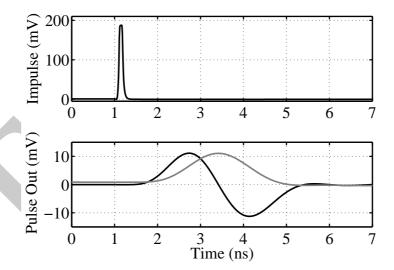

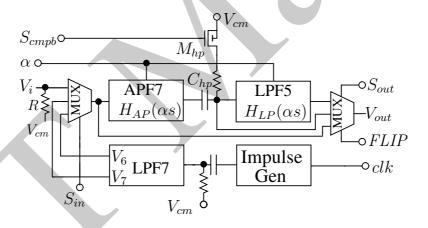

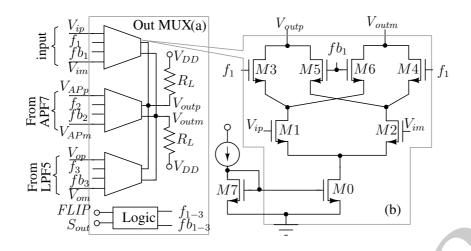

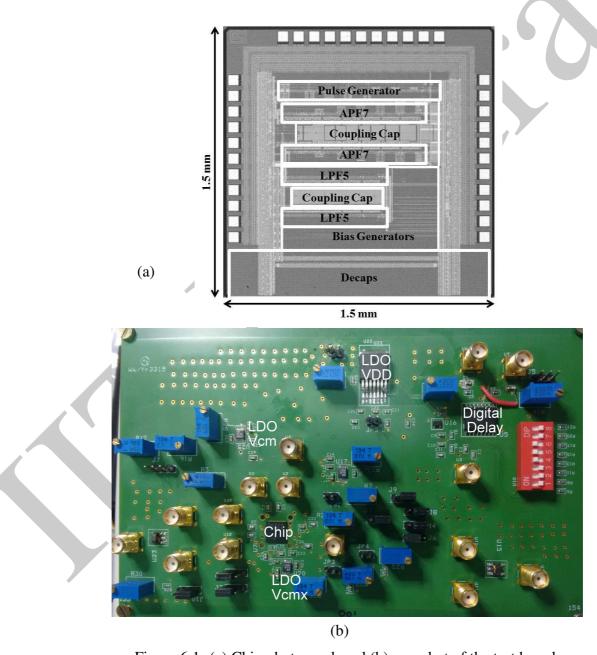

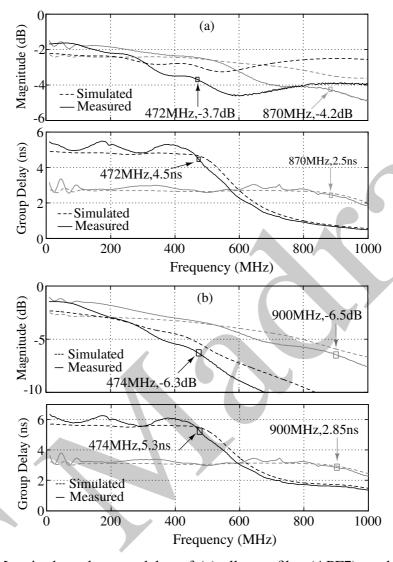

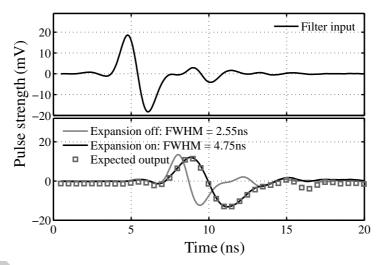

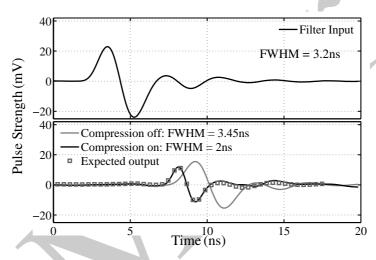

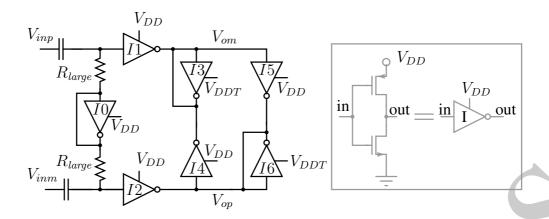

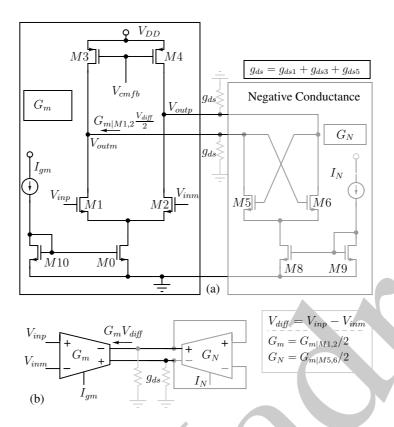

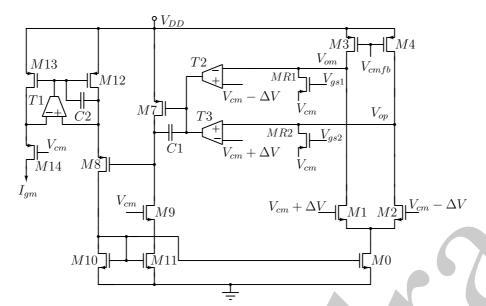

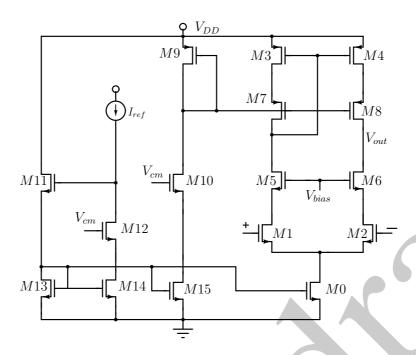

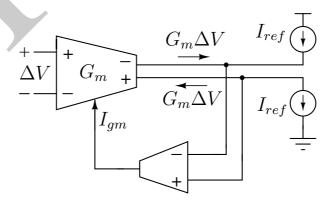

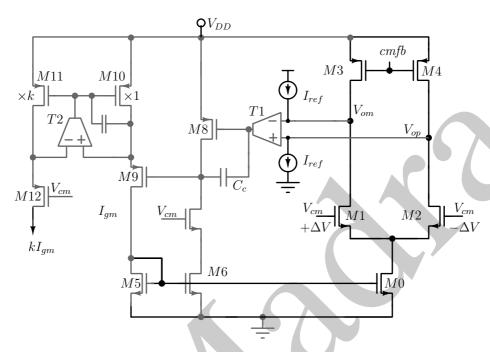

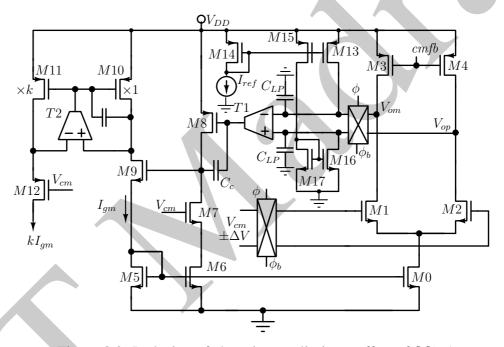

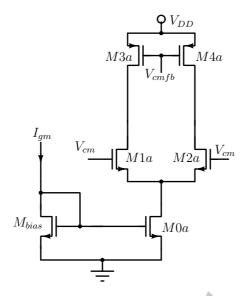

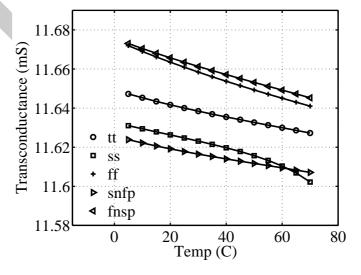

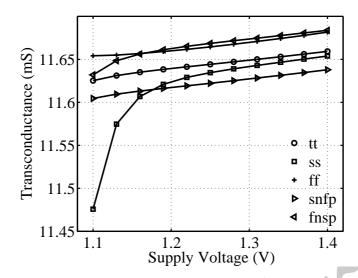

(2.17)