## Optical Packet Switching Architectures Incorporating Various Buffering Techniques using Fiber Delay Lines

by

### RAJAT KUMAR SINGH

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY KANPUR

May, 2007

## Optical Packet Switching Architectures Incorporating Various Buffering Techniques using Fiber Delay Lines

A Thesis Submitted

in Partial Fulfilment of the Requirements

for the Degree of

### DOCTOR OF PHILOSOPHY

by

### RAJAT KUMAR SINGH

(Y120463)

to the

# DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY KANPUR

May, 2007

# THESIS SUBMITTED ON .2.2.5.10.3.10

## **CERTIFICATE**

It is certified that the work contained in the thesis entitled "Optical Packet Switching Architectures Incorporating Various Buffering Techniques using Fiber Delay Lines" being submitted by Mr. Rajat Kumar Singh has been carried out under my supervision. In my opinion, the thesis has reached the standard fulfilling the requirement of regulation of the Ph.D. degree. The results embodied in this thesis have not been submitted elsewhere for the award of any degree or diploma.

Dr. Yatindra Nath Singh

Associate Professor

Department of Electrical Engineering

Indian Institute of Technology Kanpur

Kanpur, INDIA

13 May, 2007

# Acknowledgements

People prefer to follow those who help them, not those who intimidate them.

— C. Gene Wilkes

I feel immense pleasure in expressing my profound sense of gratitude to my thesis supervisor Dr. Y. N. Singh under whose supervision and inspiring guidance, I had privilege to carry out my research work. I am indebted to him for his constant and ungrudging encouragement, valuable suggestions and ingenious ideas. He showed me different ways to approach a research problem and the need to be persistent to accomplish any goal.

I express my heartiest thanks to Prof. P. K. Kalra, Head of the Department of Electrical Engineering, IIT Kanpur for providing me necessary facilities. I am grateful to all the faculty members of my department, for their support and encouragement. I also thank to the staff members of the department, for their cooperation and help during this period. I extend my thanks to Dr. S. Balasubramanian and Dr. V. K. Chaubey of BITS Pilani, for encouraging me to pursue higher studies.

I thank my colleagues and friend Mr. Rajiv Srivastava and Vipin Mangal for their intellectual contributions to this work. They need special mention as they contributed by way of in-depth discussion and suggestion on various topics in my research.

I would especially like to mention the kind support and selfless help I got from

Acknowledgements

my friends Jindal, Nath 'sir', Anupam, Ritesh, Tony, Ankur, Vivek, Patelji and Vikas. During the crucial times of stress and distress, they helped me and eased my restoration to my normal self. I greatly admire the love, care and concern shown by them. I am also thankful to my friends Balan, Swapnil, Kaka, Akshay, Sachin, Sonkar, Tathagat, Nagendra, Dwivedi, Pathak, Gangele, Singhvi and many others for making my stay at IITK enjoyable and memorable.

I wish to express my deep gratitude to my wife Neetu for her valuable advice, consistent help and encouragement to boost my morale and confidence. Her love and support have been an invaluable source of inspiration to me. I do believe that without ardent support of her, this work probably would not have seen the ray of the day.

Though it is beyond the scope of any acknowledgement for all that I have received from my parents by way of inspiration, patience and encouragement at all times but most conspicuously during this period, yet I make an effort to express my heartfelt and affectionate gratitude to them. May God guide me to the wishes of my parents so that they feel the joy of having lived a contented life in my conduct to them.

(Rajat Kumar Singh)

# Synopsis

Name of the Student : Rajat Kumar Singh

Roll Number : Y120463

Degree for which submitted : **Ph.D.**

Department : Electrical Engineering

Thesis Title : Optical Packet Switching Architectures

Incorporating Various Buffering Techniques

using Fiber Delay Lines

Thesis Supervisor : Dr. Yatindra Nath Singh

Month and year of submission : May, 2007

The bandwidth demand due to more and more data intensive applications and growth in userbase, is increasing day by day. Optical networks are the most suitable option for satisfying this increased bandwidth requirements, due to the availability of large bandwidth in the fiber [16, 68]. The optical network implementations can have electronic or all-optical switches. In optical transport networks, the current approach is to use optical circuit switches to set up light paths [1, 49, 59]. These all-optical switches are transparent to information carried over the light path. The possibility of packet switching using photonic technologies, allows all-optical packet switched networks where packets remain in optical form without undergoing optoelectronic conversion at intermediate nodes.

One of the major issues involved in optical networking is the switch/router architecture which can perform the switching operation efficiently at such high data rates.

Synopsis vi

The purpose of switching is to route the packet to the destined output port. The important aspects of photonic packet switching are control, packet synchronization, clock recovery, packet routing, contention resolution and packet header replacement [18, 64]. Contention is one of these problems, which occurs when two or more packets arrive at same time for same destination. To avoid this contention, one of the contending packets, is directed to the intended output port and other packets are either stored or dropped. All-optical memory suitable for optical storage has not yet been developed. The alternative is to use deflection routing [13] or optical fiber delay lines (in traveling or recirculating type configuration). Different techniques for optical buffering by using fiber delay lines have been proposed [7, 31, 32, 56], and still research is going on to explore better solutions. Optical buffering can be introduced in three ways: input buffering, output buffering and shared buffering [2, 6, 15, 29].

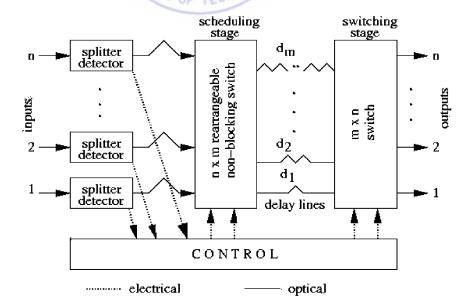

In this thesis, different aspects of optical buffering are investigated in various architectures for optical packet switching. Some new architectures have also been proposed alongwith the buffering techniques and their analysis. The main objective of the thesis, is to identify the optimal buffering parameters to provide least packet loss probability and reasonable average delay using the given resources.

The thesis is organized in the following nine chapters.

In **Chapter 1**, first we have explained the evolution of lightwave communication techniques. Then, we have given a review of related literature, providing a motivation to the study carried out in this thesis.

In Chapter 2, we have given the basic overview of the photonic packet switching architectures. We also discuss the switching/buffering technologies and the optical components used in the switch architectures.

Synopsis

Chapter 3 proposes a modification in the Staggering switch architecture [28], by adding the fiber delay line (FDL) to improve its performance. The effectiveness of modification, has also been discussed.

In Chapter 4, we have presented a new approach of switching in Data Vortex switch architecture [71] to improve its performance. Simulations have been done and the results are analyzed to find the advantages. Throughput analysis is also done, which is not performed so far.

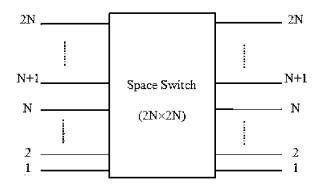

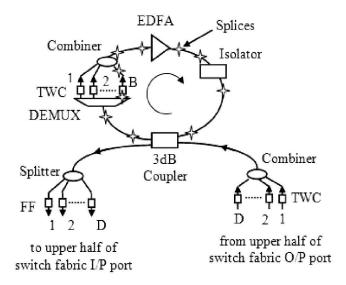

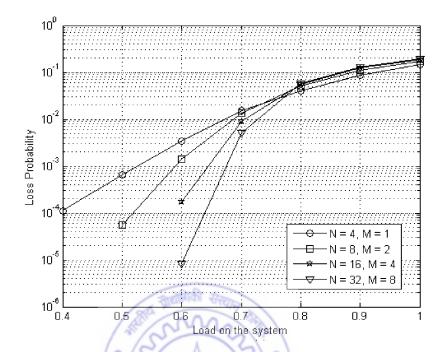

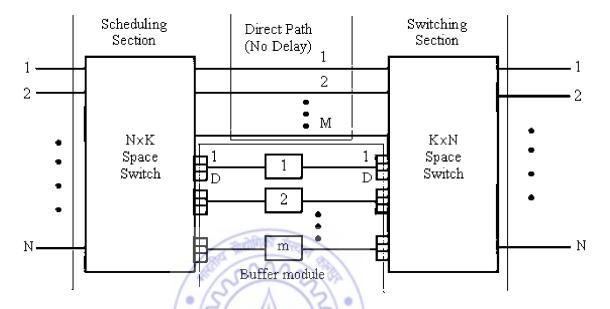

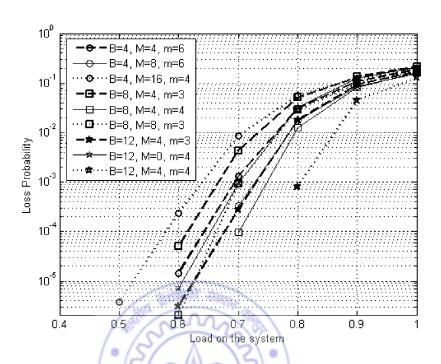

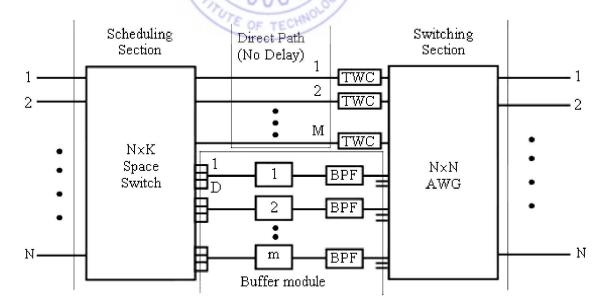

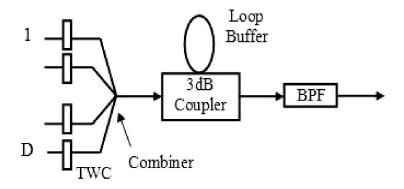

In Chapter 5, we have proposed a new optical packet switch architecture which uses shared loop buffer modules in feedback configuration. WDM based fiber delay lines are used to store the contending packets, and a space switch fabric is used to direct them appropriately. These delay lines incorporate various optical components which induce loss in the signal power, during recirculation of signal in the loop. We have done the power budget analysis considering the effect of noise to calculate the number of maximum allowed circulations for a packet, in the loop buffer. The buffering duration in the recirculating loop, is limited by this circulation limit. The results for packet loss probability and average delay, are obtained using a specific scheduling algorithm and simulation techniques. The mathematical analysis has also been done to validate the simulation results.

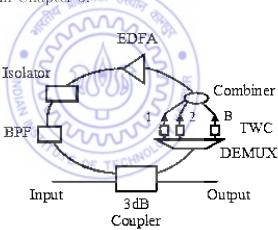

Chapter 6 discusses about the enhancement in the optical packet switch architecture proposed in Chapter 5. The main disadvantage of this architecture, is very high loss in signal power, which reduces the number of maximum allowed circulations in loop buffer modules. Thus to reduce the power loss, we have proposed two modifications. The main objective of these modifications is to increase the number of maximum allowed circulations. This will provide a relaxation in the circulation limit, which in turn

Synopsis

results in better packet loss probability and average delay by effectively utilizing the available buffer capacity.

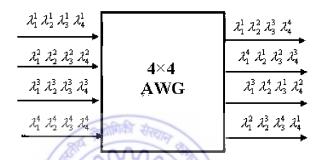

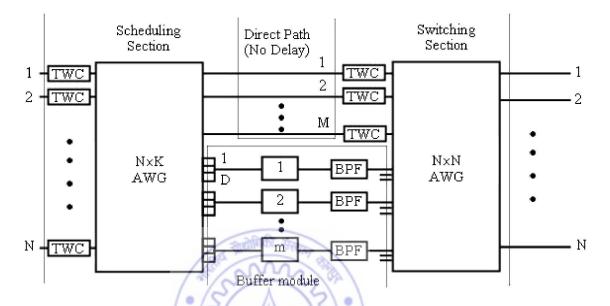

In Chapter 7, we have proposed three architectures for optical packet switching based on wavelength routed feed-forward shared buffer modules. These architectures are developed by selecting three different combinations of space switch and Arrayed Waveguide Grating (AWG). The buffer modules are constructed using recirculating type fiber delay lines incorporating various optical components. One of these architectures is also analyzed in terms of power loss and noise power, due to the presence of various optical components in loop buffer memory. The performance is predicted on the basis of operational insights. Further, the same has been verified by getting results for the packet loss probability and average delay by simulations.

Chapter 8 presents the comparative analysis of various optical packet switch architectures, discussed in the previous chapters. The comparison is done on the basis of optical cost of switch architectures and performance for bursty traffic arrival.

Finally, **Chapter 9** provides conclusion of the thesis, and suggestion for the future research in this area.

# Contents

| Lı | st of        | Figures                                                     | XV   |

|----|--------------|-------------------------------------------------------------|------|

| Li | st of        | Tables                                                      | xxi  |

| Li | ${ m st}$ of | 15/00/01/21                                                 | xiii |

| Li | st of        | Acronyms                                                    | xiv  |

| 1  | Intr         | roduction OF TECHNOLO                                       | 1    |

|    | 1.1          | Evolution of Communication Techniques                       | 1    |

|    | 1.2          | Optical Networks                                            | 3    |

|    | 1.3          | Optical Packet Switching                                    | 4    |

|    | 1.4          | Outline of Thesis                                           | 5    |

| 2  | Ph           | otonic Packet Switching Architectures - A Literature Survey | 7    |

|    | 2.1          | Electronic Packet Switching Technologies                    | 7    |

|    | 2.2          | Optical Packet Switching Technologies                       | 10   |

|    |              | 2.2.1 Photonic Packet Switching                             | 10   |

CONTENTS x

|   |     | 2.2.2  | Optical Burst Switching (OBS)                    | 22 |

|---|-----|--------|--------------------------------------------------|----|

|   | 2.3 | Optica | al Switching Components                          | 23 |

|   |     | 2.3.1  | Optical Fiber                                    | 23 |

|   |     | 2.3.2  | Couplers                                         | 25 |

|   |     | 2.3.3  | Isolators and Circulators                        | 27 |

|   |     | 2.3.4  | Filters, Multiplexers and Demultiplexers         | 28 |

|   |     | 2.3.5  | Array Waveguide Grating                          | 29 |

|   |     | 2.3.6  | Optical Cross Connect                            | 30 |

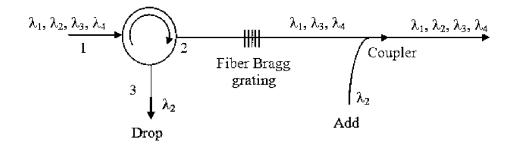

|   |     | 2.3.7  | Optical Add-Drop Multiplexer                     | 31 |

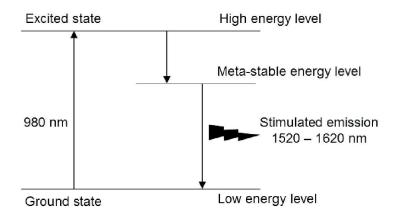

|   |     | 2.3.8  | Optical Amplifier - Erbium Doped Fiber Amplifier | 32 |

|   |     | 2.3.9  | Wavelength Converter                             | 34 |

|   | 2.4 | Summ   | Wavelength Converter                             | 35 |

| 3 | Mo  |        | Architecture for Staggering Switch               | 37 |

|   | 3.1 | Stagge | ering Switch: A brief detail                     | 37 |

|   |     | 3.1.1  | Switch Architecture and Operation                | 38 |

|   | 3.2 | Descri | ption of the modification                        | 39 |

|   | 3.3 | Perfor | mance evaluation                                 | 41 |

|   |     | 3.3.1  | Utilization of Delay Lines                       | 44 |

|   | 3.4 | Summ   | ary                                              | 46 |

| 1 | ΔΙ  | Νοω Δ  | pproach to Data Vortey Switch Architecture       | 18 |

CONTENTS

|   | 4.1 | Data Vortex: an overview                                                                         | 49         |

|---|-----|--------------------------------------------------------------------------------------------------|------------|

|   | 4.2 | Description of the modification                                                                  | 52         |

|   |     | 4.2.1 Addition of extra delay lines at every input port                                          | 52         |

|   | 4.3 | Throughput Analysis                                                                              | 57         |

|   | 4.4 | Summary                                                                                          | 59         |

| 5 |     | Architecture for Optical Packet Switch based on WDM Loop<br>fer Memory in feedback configuration | <b>6</b> 0 |

|   | 5.1 | Description of the switch                                                                        |            |

|   | 5.2 | Working of the switch architecture                                                               | 63         |

|   | 5.3 |                                                                                                  |            |

|   |     | Switch without circulation limit                                                                 | 66         |

|   |     | 5.3.2 Performance Analysis and Results                                                           | 68         |

|   | 5.4 | Switch with circulation limit                                                                    | 74         |

|   |     | 5.4.1 Power Budget Analysis                                                                      | 74         |

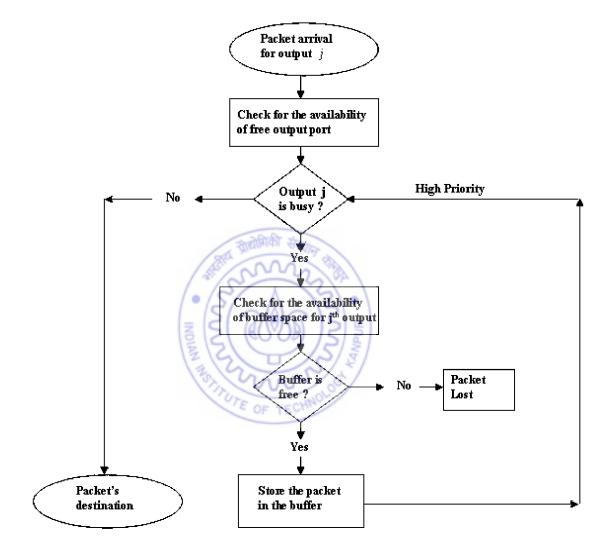

|   |     | 5.4.2 Scheduling algorithm                                                                       | 86         |

|   |     | 5.4.3 Performance Analysis and Results                                                           | 87         |

|   | 5.5 | Mathematical Analysis                                                                            | 93         |

|   |     | 5.5.1 Induction Proof of the Formula for Input Pattern (IP)                                      | 96         |

|   |     | 5.5.2 Comparison of Mathematical and Simulation Analysis                                         | 98         |

|   | 5.6 | Summary                                                                                          | 99         |

CONTENTS

| Ò | AW<br>Buf | G and EDFA based Optical Packet Switch using Feedback Shared fer   | 101 |

|---|-----------|--------------------------------------------------------------------|-----|

|   | 6.1       | Feedback Optical Packet Switch Architectures: An overview          | 102 |

|   | 6.2       | Proposed Modifications in Optical Packet Switch Architectures      | 103 |

|   |           | 6.2.1 Placement of an optical amplifier (EDFA)                     | 103 |

|   |           | 6.2.2 Replacement of space switch with AWG                         | 104 |

|   | 6.3       | Power Budget Analysis                                              | 106 |

|   |           | 6.3.1 Mod-EDFA                                                     | 106 |

|   |           | 6.3.2 Mod-AWG                                                      | 109 |

|   |           | 6.3.3 Calculation                                                  | 111 |

|   | 6.4       | Simulation Analysis and Results                                    | 111 |

|   | 6.5       | Summary                                                            | 115 |

| 7 |           | welength routed shared buffer based feed-forward architectures for |     |

|   | opti      | ical packet switching                                              | 116 |

|   | 7.1       | Description of the Architecture A1                                 | 117 |

|   | 7.2       | Scheduling Algorithm                                               | 119 |

|   |           | 7.2.1 Performance Evaluation                                       | 121 |

|   | 7.3       | Power Budget Analysis for Architecture A1                          | 126 |

|   |           | 7.3.1 Loss Analysis                                                | 127 |

|   |           | 7.3.2 Power Analysis                                               | 128 |

|   |           | 7.3.3 Noise Analysis and Calculation                               | 129 |

| CONTERNITE | •••  |

|------------|------|

| CONTRACTO  | 3/11 |

| CONTENTS   | XII  |

|            |      |

|    |              | 7.3.4 Simulation Results                                        | 30 |

|----|--------------|-----------------------------------------------------------------|----|

|    | 7.4          | Description of the Architectures A2 and A3                      | 34 |

|    | 7.5          | Comparison among three architectures                            | 36 |

|    |              | 7.5.1 Link Loss Analysis                                        | 36 |

|    |              | 7.5.2 Control Complexity                                        | 37 |

|    | 7.6          | Summary                                                         | 38 |

| 8  | $\mathbf{A}$ | comparative analysis of Optical Packet Switch Architectures for |    |

|    | Opt          | ical Cost and Bursty Traffic 13                                 | 39 |

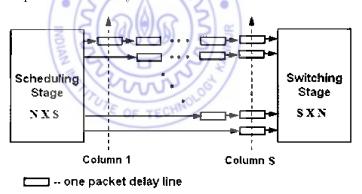

|    | 8.1          | Switch Architectures - an overview                              | 39 |

|    | 8.2          | Optical cost analysis                                           | 40 |

|    |              | 8.2.1 Estimation of Optical cost                                | 42 |

|    | 8.3          | Bursty traffic analysis                                         | 45 |

|    |              | 8.3.1 Bursty traffic model                                      | 45 |

|    |              | 8.3.2 Performance evaluation and Results                        | 48 |

|    | 8.4          | Summary                                                         | 53 |

| 9  | Co           | nclusions and Scope for Future Work                             | 54 |

|    | 9.1          | Conclusions                                                     | 54 |

|    | 9.2          | Scope for Future Work                                           | 56 |

| Bi | ibliog       | raphy 1                                                         | 58 |

CONTENTS

List of Publications 167

# List of Figures

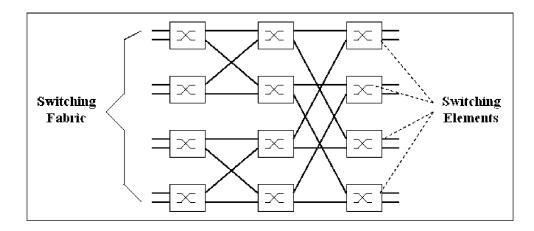

| 2.1  | Multi-stage Interconnection Network              | 8  |

|------|--------------------------------------------------|----|

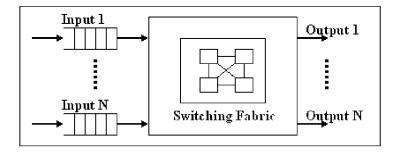

| 2.2  | Input buffering arrangement                      | 9  |

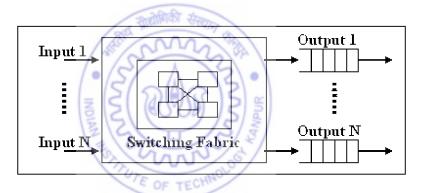

| 2.3  | Output buffering arrangement                     | 9  |

| 2.4  | Shared buffering arrangement                     | 9  |

| 2.5  | General Architecture of Photonic Packet Switch   | 11 |

| 2.6  | SOA gate based space division switch             | 13 |

| 2.7  | Broadcast-and-select photonic packet switch      | 13 |

| 2.8  | Wavelength routed photonic packet switch         | 14 |

| 2.9  | Different types of optical buffers               | 19 |

| 2.10 | Wavelength Conversion                            | 20 |

| 2.11 | A $2 \times 2$ coupler                           | 26 |

| 2.12 | Isolator                                         | 27 |

| 2.13 | A 4-port circulator                              | 28 |

| 2.14 | Wavelength filter, multiplexer and demultiplexer | 29 |

| 2.15 | Structure of AWG                                 | 30 |

LIST OF FIGURES xvi

| 2.16 | Routing Pattern of AWG                                                                                                          | 30 |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 2.17 | Optical add/drop element based on FBG and circulator                                                                            | 31 |

| 2.18 | Energy level diagram for spontaneous emission of Erbium atom                                                                    | 33 |

| 2.19 | Erbium doped fiber amplifier                                                                                                    | 33 |

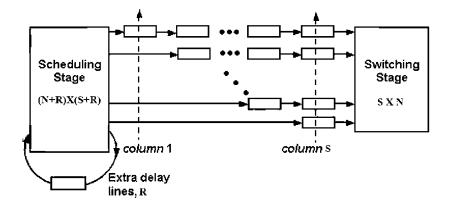

| 3.1  | Architecture of the Staggering Switch                                                                                           | 38 |

| 3.2  | Definition of Scheduling algorithm                                                                                              | 39 |

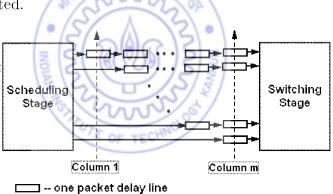

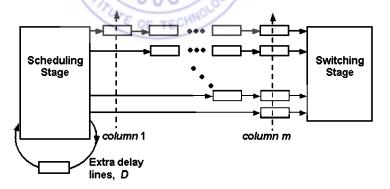

| 3.3  | Modified Architecture                                                                                                           | 40 |

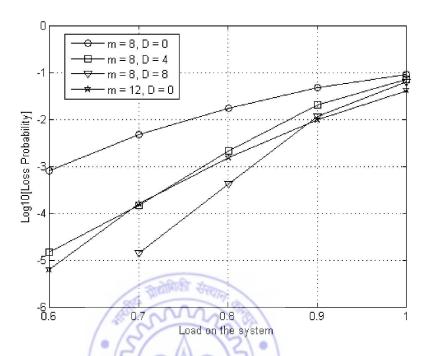

| 3.4  | Loss probability for various values of $D$ and $m$ with $n=8$                                                                   | 43 |

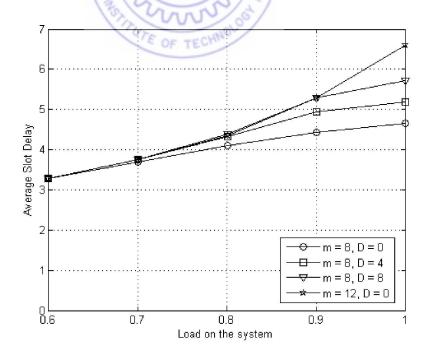

| 3.5  | Average delay for various values of $D$ and $m$ with $n = 8 \ldots \ldots \ldots$                                               | 43 |

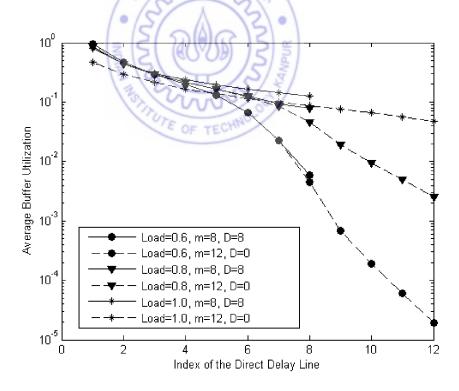

| 3.6  | Average buffer utilization for various values of $D$ and $m$ with $n=8$ under different loading conditions                      | 44 |

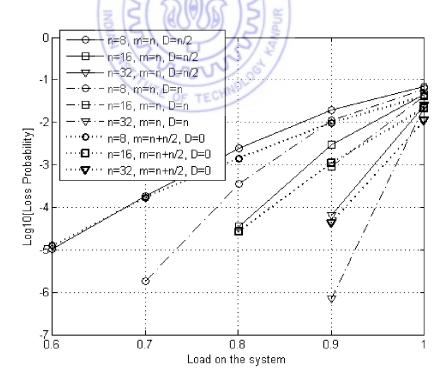

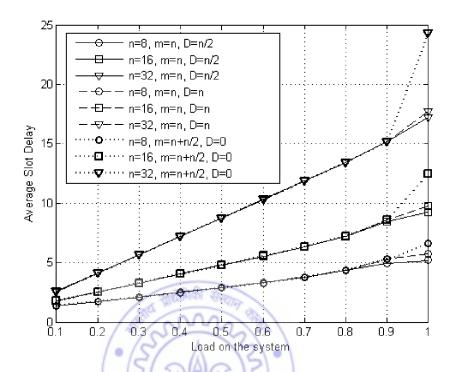

| 3.7  | Loss probability for various $D$ and $m$ with increasing $n$                                                                    | 45 |

| 3.8  | Average delay for various $D$ and $m$ with increasing $n$                                                                       | 46 |

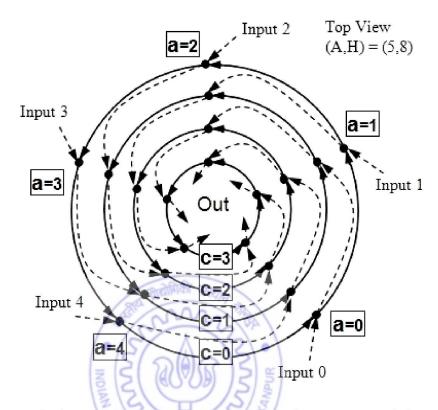

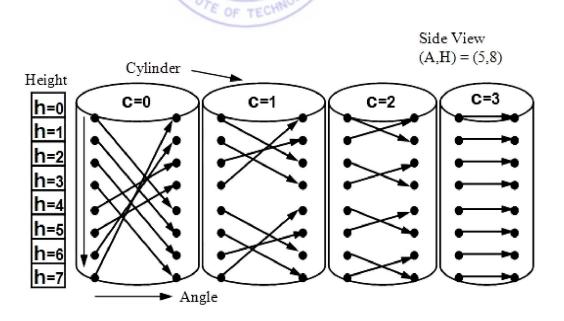

| 4.1  | Architecture of the Data Vortex switch: <i>Top view</i> of the cylinders                                                        | 50 |

| 4.2  | Architecture of the Data Vortex switch: Side view of the cylinders                                                              | 50 |

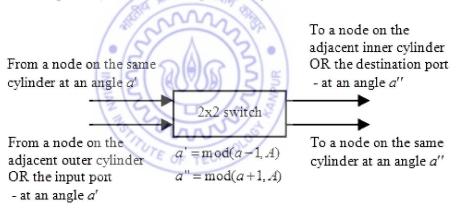

| 4.3  | Switching port on all the cylinders                                                                                             | 51 |

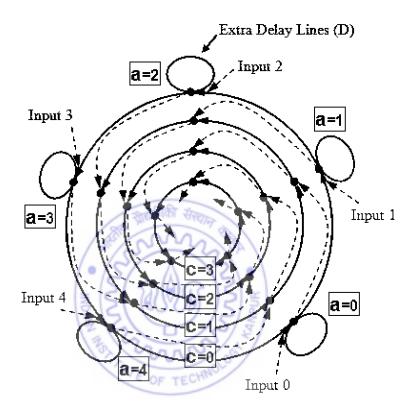

| 4.4  | Modified Data Vortex switch (Top view)                                                                                          | 53 |

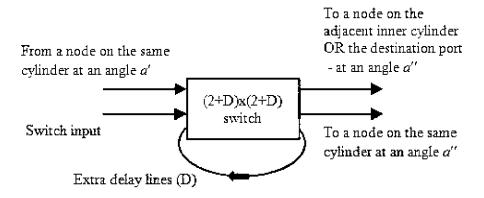

| 4.5  | Modified switching port on the outermost cylinder. Other switching ports will remain same as shown in Figure 4.3                | 53 |

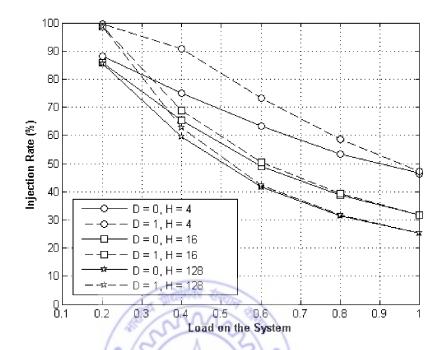

| 4.6  | Injection Ratio after adding a single extra delay line for $A=5$ . Straight line: Actual results, Dashed line: Modified results | 55 |

LIST OF FIGURES xvii

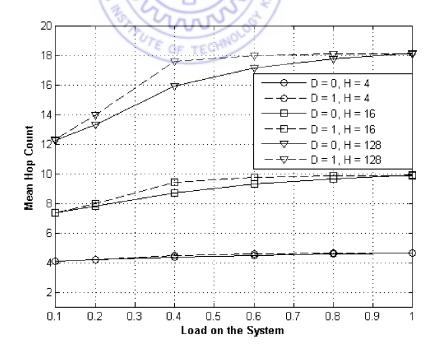

| 4.7  | Average Delay after adding a single extra delay line for $A = 5$ . Straight line: Actual results, Dashed line: Modified results   | 55 |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

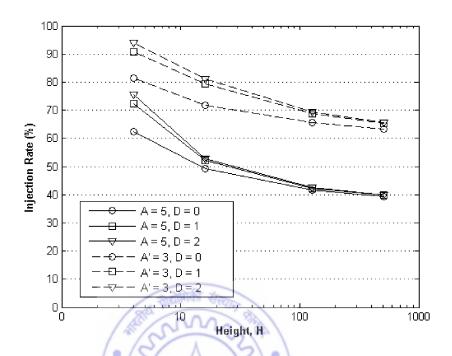

| 4.8  | Modified results for IR with Height under $\rho=0.6$ . Straight line: Symmetrical data, Dashed line: Asymmetrical data            | 56 |

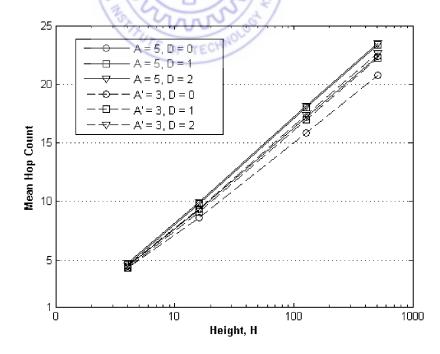

| 4.9  | Modified results for Average Delay with Height under $\rho=0.6$ . Straight line: Symmetrical data, Dashed line: Asymmetrical data | 56 |

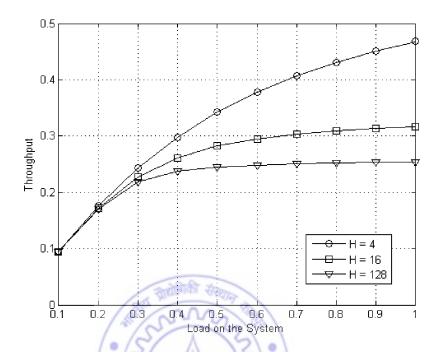

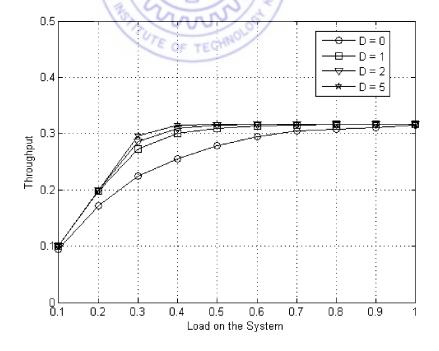

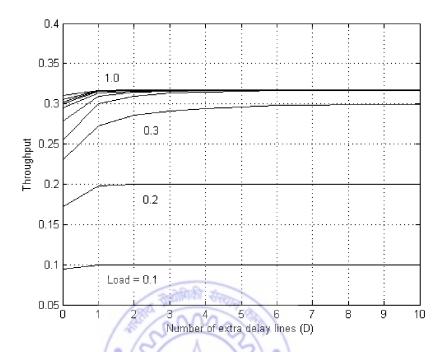

| 4.10 | System 'Throughput' under symmetrical data for $A=5.$                                                                             | 58 |

| 4.11 | Modified results for system 'Throughput' for $A=5$ and $H=16$ for various values of $D.\ldots$                                    | 58 |

| 4.12 | Modified results for system 'Throughput' for $A=5$ and $H=16$ at various loads                                                    | 59 |

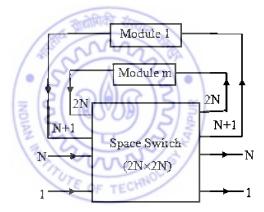

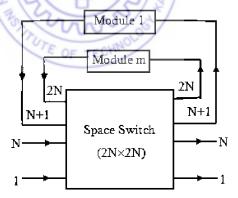

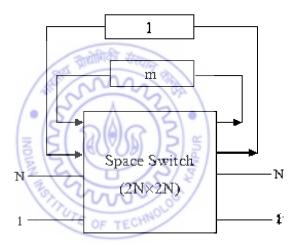

| 5.1  | Optical packet switch architecture. Modules (1 to m) represent optical loop buffer memories                                       | 61 |

| 5.2  | Architecture of the core switch                                                                                                   | 61 |

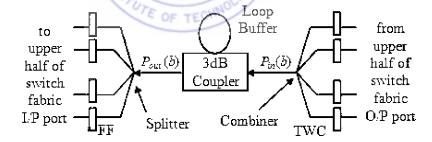

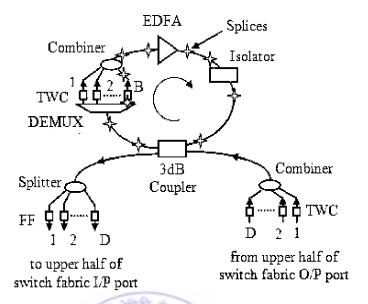

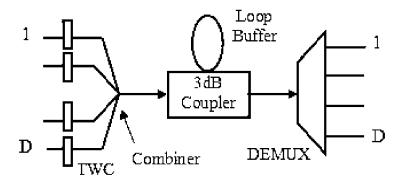

| 5.3  | Loop Buffer Module                                                                                                                | 62 |

| 5.4  | Flow Chart for the Scheduling Algorithm                                                                                           | 68 |

| 5.5  | Number of module is maximum for each case at $B=4.$                                                                               | 70 |

| 5.6  | Total number of modules in each case is $M$ (= $p \times N/D$ ) and buffer capacity equals to $MB$ at $B=D=4$ and $\rho=0.7$      | 72 |

| 5.7  | Number of module is maximum for each case at $B=4.$                                                                               | 72 |

| 5.8  | Total number of modules in each case is $M$ (= $p \times N/D$ ) and buffer capacity equals to $MB$ at $B=D=4$ and $\rho=0.5$      | 73 |

| 5.9  | Total buffer capacity is equal to $MB$ at $B=4$                                                                                   | 73 |

LIST OF FIGURES xviii

| 5.10 | Model of Loop Buffer Memory Module                                                                                                      | . 74  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|

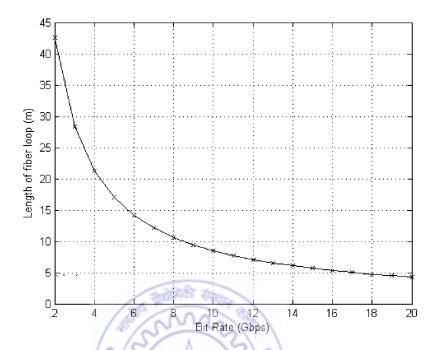

| 5.11 | Variation of loop length with data rate                                                                                                 | . 84  |

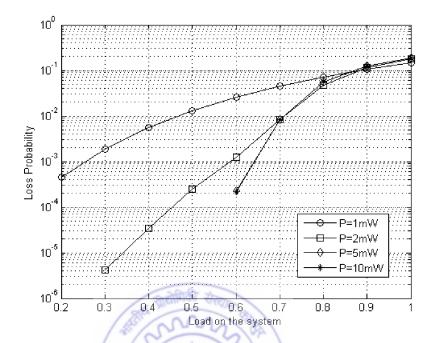

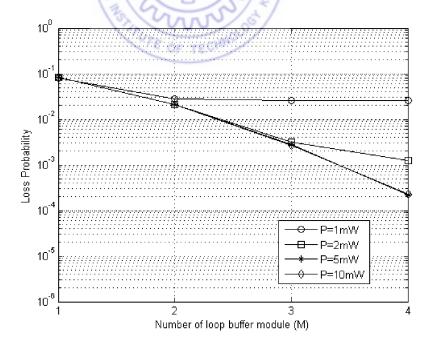

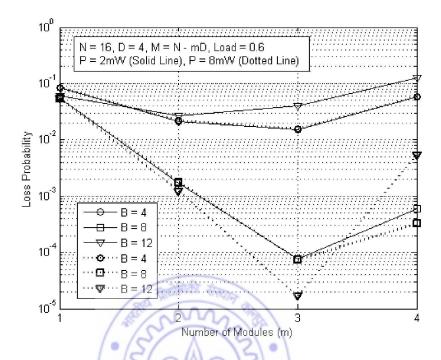

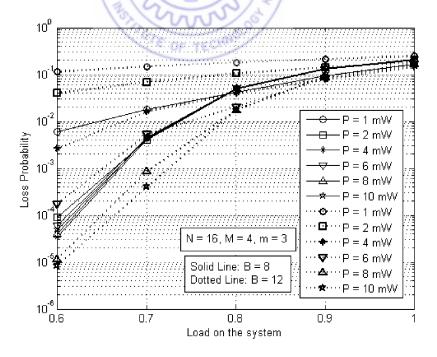

| 5.12 | Probability of packet loss with Load on the system for $N=16,M=4$ at different values of signal power $(P)$                             | . 88  |

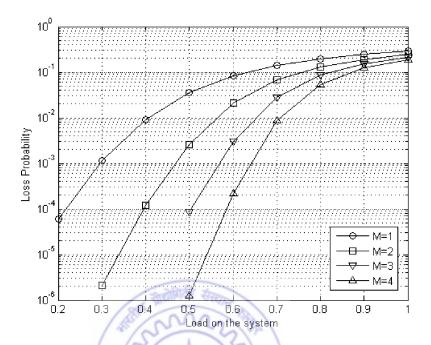

| 5.13 | Probability of packet loss with Load on the system for $N=16,P=5mW$ at different values of number of buffer modules $(M),\ldots,\ldots$ | . 89  |

| 5.14 | Probability of packet loss with number of buffer module $(M)$ for $N=16$ , $\rho=0.6$ at different values of signal power $(P)$         | . 89  |

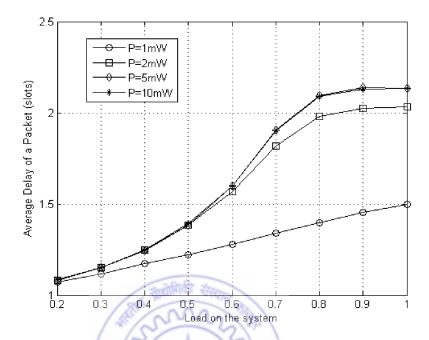

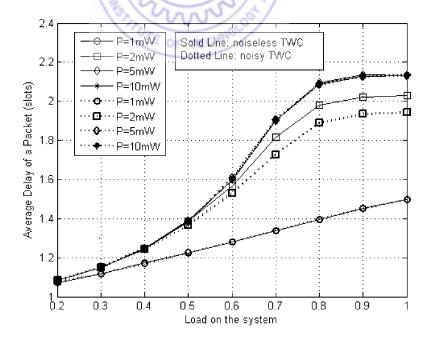

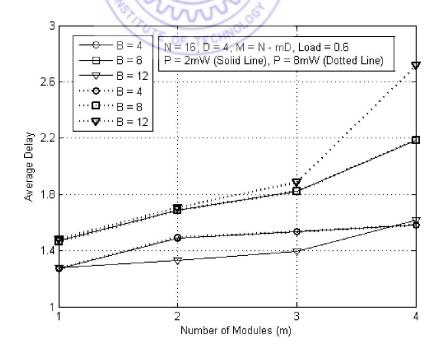

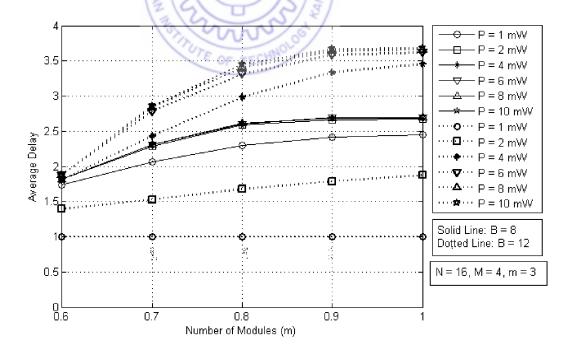

| 5.15 | Average Delay with Load on the system for $N=16,M=4$ at different values of signal power $(P),\ldots,\ldots,\ldots$                     | . 90  |

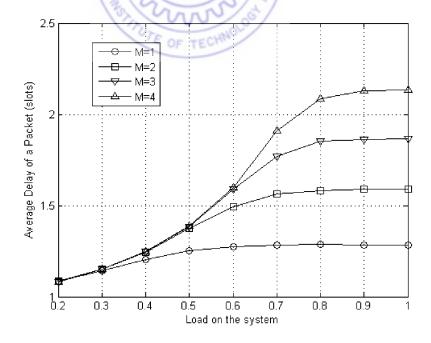

| 5.16 | Average Delay with Load on the system for $N=16,\ P=5mW$ at different numbers of module $(M),\ldots,\ldots,\ldots$                      | . 90  |

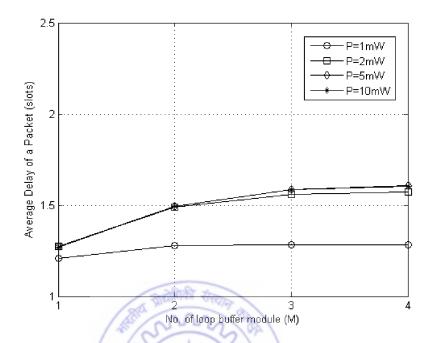

| 5.17 | Average Delay with number of buffer module $(M)$ for $N=16, \rho=0.6$ at different values of signal power $(P)$                         | . 91  |

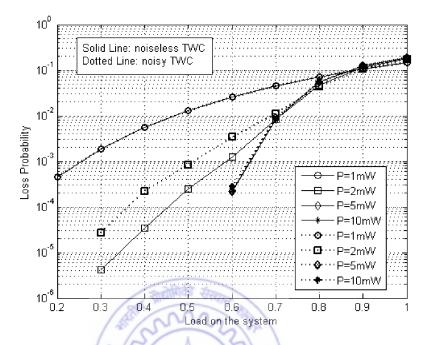

| 5.18 | Comparative results for Probability of packet loss at $N=16, B=4, M=4$ (noiseless TWC vs. noisy TWC)                                    | . 92  |

| 5.19 | Comparative results for Average Delay at $N=16, B=4, M=4$ (noiseless TWC vs. noisy TWC)                                                 | . 92  |

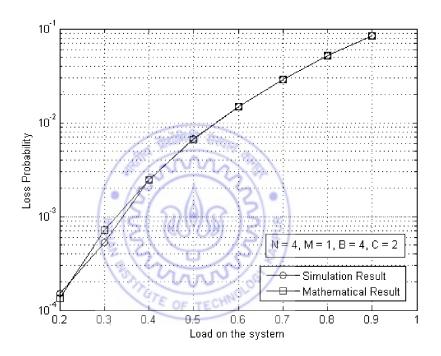

| 5.20 | Comparative results for simulation and mathematical method                                                                              | . 99  |

| 6.1  | Optical packet switch architecture. Modules (1 to $m$ ) represent loop buffer modules, each with $B$ wavelength                         | . 102 |

| 6.2  | Loop Buffer Module                                                                                                                      | . 103 |

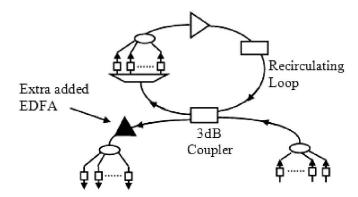

| 6.3  | Modified Loop Buffer Module: Placement of an extra EDFA in each buffer module                                                           | 104   |

LIST OF FIGURES xix

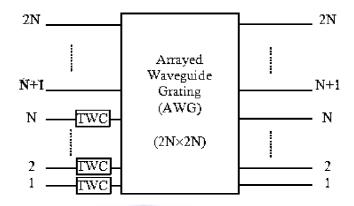

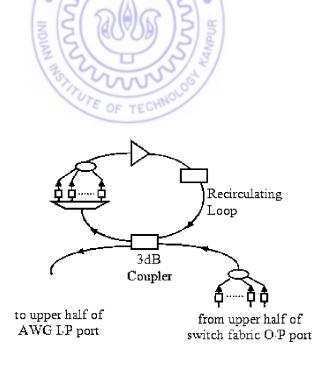

| 6.4  | Modified switch: Replacement of core space switch with AWG 105                    |

|------|-----------------------------------------------------------------------------------|

| 6.5  | Modified Loop Buffer Module for AWG as the core of switch architecture. 105       |

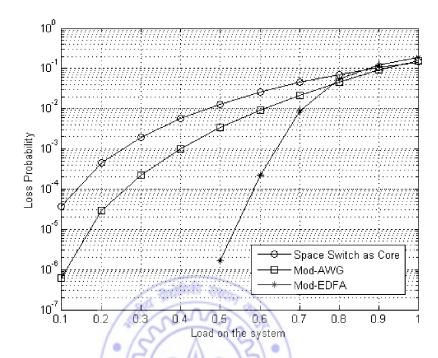

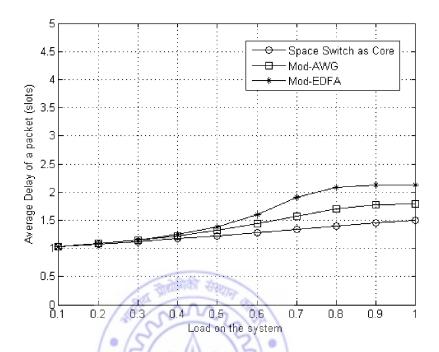

| 6.6  | Loss probability for $2N=32,\ D=4,\ B=4,\ M=N/D$ and $P=1mW.$ 113                 |

| 6.7  | Loss probability for $2N=32,\ D=4,\ B=4,\ {\rm Load}=0.6$ and $P=1mW.$ 113        |

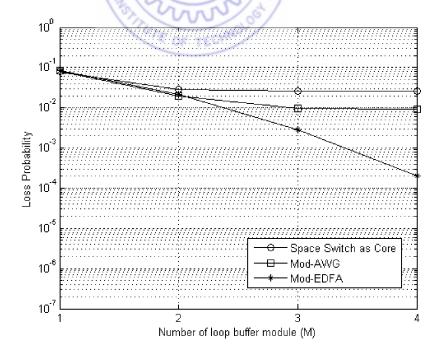

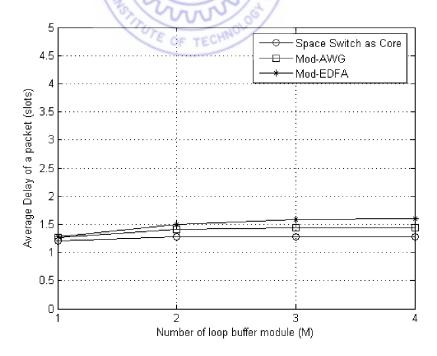

| 6.8  | Average delay for $2N=32,\ D=4,\ B=4,\ M=N/D$ and $P=1mW$ 114                     |

| 6.9  | Average delay for $2N=32,\ D=4,\ B=4,\ {\rm Load}=0.6$ and $P=1mW.$ . 114         |

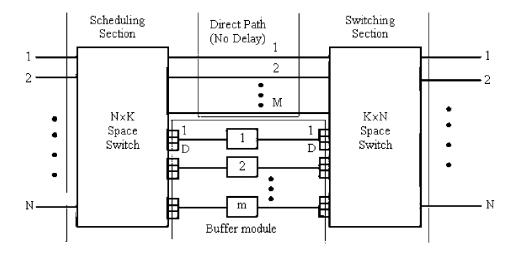

| 7.1  | Switch Architecture - A1                                                          |

| 7.2  | Buffer module for A1                                                              |

| 7.3  | Architecture of recirculating loop                                                |

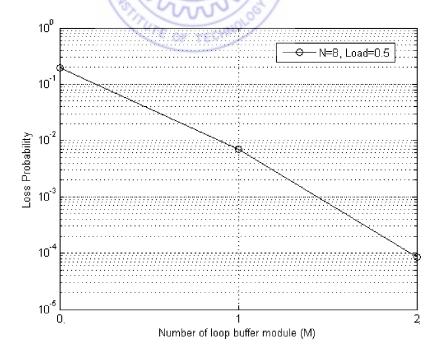

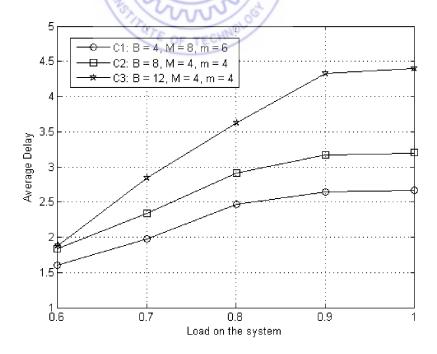

| 7.4  | Loss probability for $N=16$ with various combination of $B,M$ and $m$ 122         |

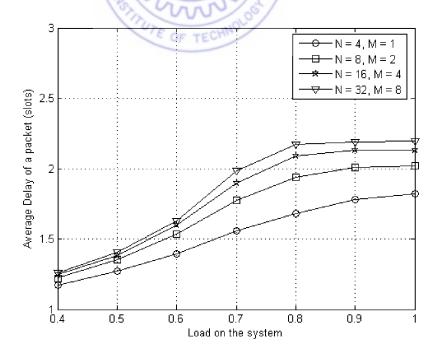

| 7.5  | Comparison of Average Delay for $C1,\ C2,\ C3$ at $D=4$ and $N=16$ 122            |

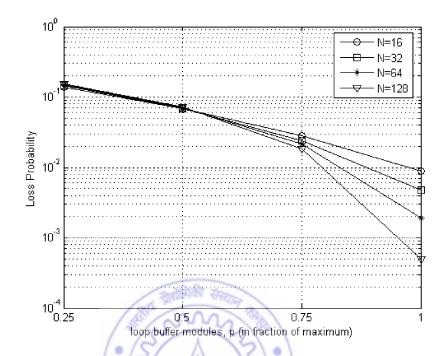

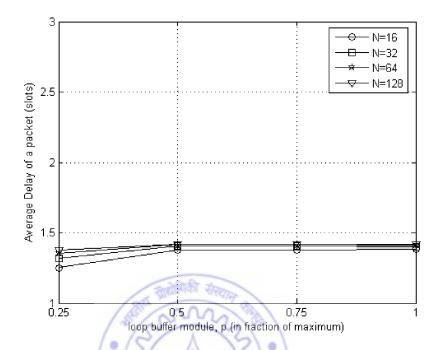

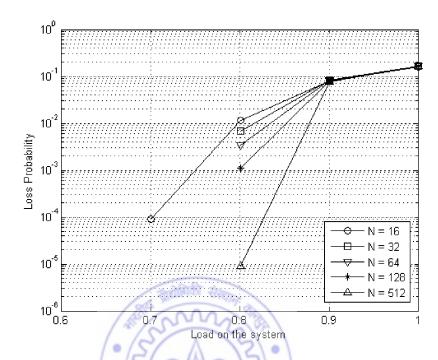

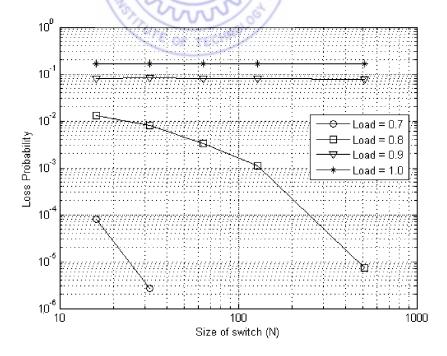

| 7.6  | Loss probability for various switch size using $C2$ at $D=4$                      |

| 7.7  | Loss probability under various load on system using $C2$ at $D=4$ 125             |

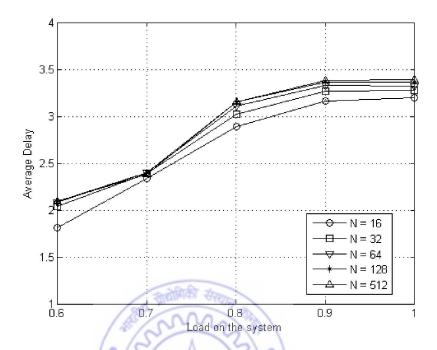

| 7.8  | Average Delay for various switch size using $C2$ at $D=4$                         |

| 7.9  | Optimization of $B$ and $m$ for $N=16$ in terms of loss probability 131           |

| 7.10 | Optimization of $B$ and $m$ for $N=16$ in terms of average delay (slot count).131 |

| 7.11 | Probability of packet loss for various power levels at $D=4$ 132                  |

| 7.12 | Average delay (slot count) for various power levels at $D=4$                      |

| 7.13 | Switch Architecture - A2                                                          |

| 7.14 | Switch Architecture - A3                                                          |

LIST OF FIGURES xx

| 7.15 | Buffer module for A2 and A3                                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.1  | Switch Architecture - A1                                                                                                                                       |

| 8.2  | Switch Architecture - A2                                                                                                                                       |

| 8.3  | Switch Architecture - A3                                                                                                                                       |

| 8.4  | Switch Architecture - A4                                                                                                                                       |

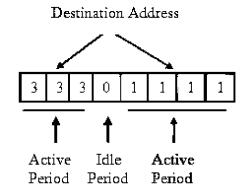

| 8.5  | Packet sequencing for bursty traffic                                                                                                                           |

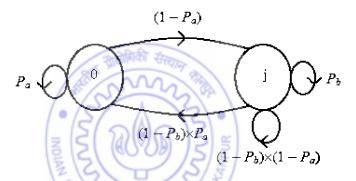

| 8.6  | Markov chain model for bursty traffic                                                                                                                          |

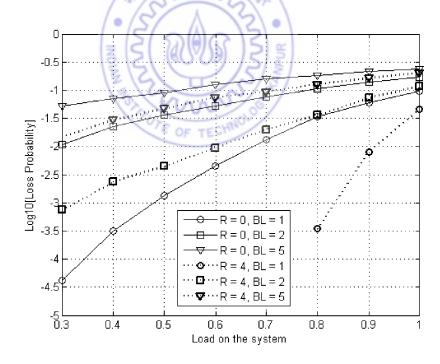

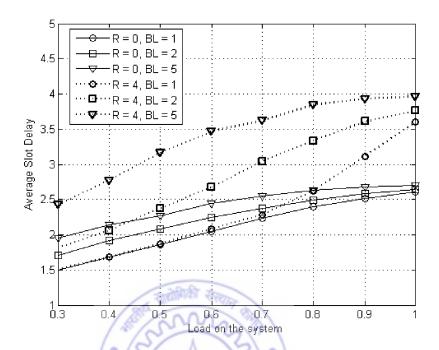

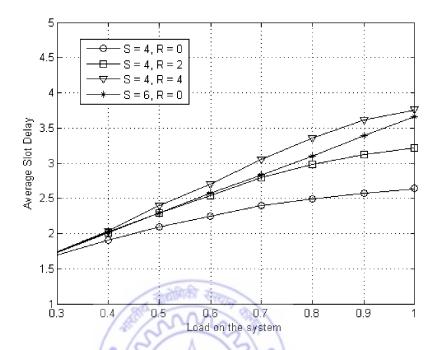

| 8.7  | Loss probability for various length of bursty traffic applied on switch of $N=4$ and $S=4$ . At is represented by $R=0$ while $R=4$ is used for A2 149         |

| 8.8  | Average delay for various length of bursty traffic applied on switch of $N=4$ and $S=\overline{4}$ . At is represented by $R=0$ while $R=4$ is used for A2 150 |

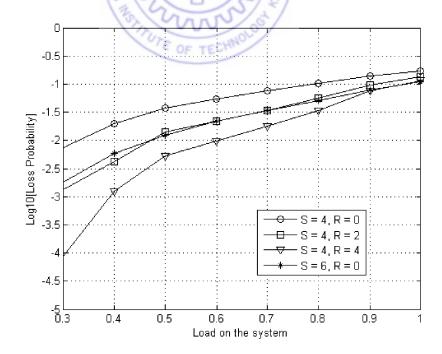

| 8.9  | Comparison of Loss probability using various combination of $S$ & $R$ for $BL=2$                                                                               |

| 8.10 | Comparison of Average delay using various combination of $S$ & $R$ for $BL=2$                                                                                  |

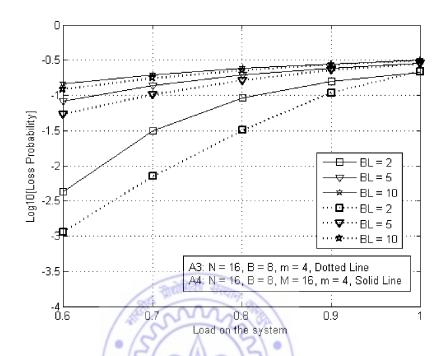

| 8.11 | Loss probability for Feedback switch (A3) and Feed-forward switch (A4). 152                                                                                    |

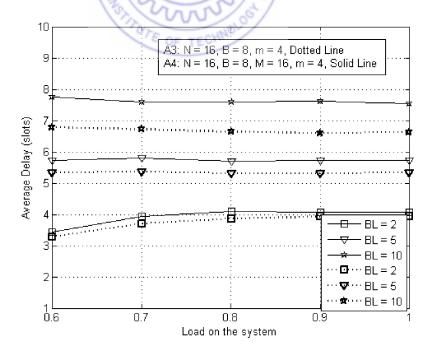

| 8.12 | Average delay for Feedback switch (A3) and Feed-forward switch (A4) 152                                                                                        |

# List of Tables

| 3.1 | Comparison of different parameters for various combinations of $m$ and                                                                        |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | $D$ at $n = 8 \dots \dots$                    | 42  |

| 3.2 | Theoretical value of average utilization of delay lines for various combi-                                                                    |     |

|     | nations of $m$ and $D$ at $n = 8 \dots \dots$ | 45  |

|     | (.5/2)                                                                                                                                        |     |

| 5.1 | Value of Different Parameters                                                                                                                 | 76  |

| 5.2 | Length of the EDFA to provide the required gain                                                                                               | 83  |

| 5.3 | Maximum number of allowed circulations $(C)$ for various sizes of core                                                                        |     |

|     | switch $(2N)$ and buffer wavelength $(B)$ at different power levels $(P)$ for                                                                 |     |

|     | D=4, considering TWC as the noiseless device                                                                                                  | 85  |

| 5.4 | Maximum number of allowed circulations ( $C$ ) for switch of size $N=16$                                                                      |     |

|     | and for various values of $D$ and $B$ at different power levels                                                                               | 86  |

| 5.5 | Maximum number of allowed circulations $(C)$ for various sizes of core                                                                        |     |

|     | switch $(2N)$ at different power levels $(P)$ for $D=4$ , considering TWC                                                                     |     |

|     | as the noisy device                                                                                                                           | 86  |

| 5.6 | Feasible number of input pattern (IP) for switch of size N                                                                                    | 96  |

|     |                                                                                                                                               |     |

| 6.1 | Maximum number of allowed circulations $(C)$ for switch of size $2N =$                                                                        |     |

|     | 32, $B = 4$ , $D = 4$ at different power levels                                                                                               | 112 |

| LIST OF TABLES | xxii |

|----------------|------|

|                |      |

| 7.1 | Complexity analysis of major component used in architecture A1 for                                                                                           |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | three efficient combinations at $D=4$ and $N=16$                                                                                                             | 24 |

| 7.2 | Number of maximum allowed circulations $(C)$ for various sizes of switch $(N)$ and buffer wavelength $(B)$ at different power levels $(P)$ considering $D=4$ | 30 |

| 8.1 | Optical cost function of the components 14                                                                                                                   | 12 |

# List of Symbols

R Responsivity

$n_{sp}$  Population inversion factor

*h* Planck's Constant

*B<sub>e</sub>* Electrical Bandwidth

B<sub>o</sub> Optical Bandwidth

q Electronic charge

ε Extinction Ratio

$R_L$  Load Resistance

T Temperature

*K*<sub>B</sub> Boltzmann constant

$L_{3dB}$  3dB coupler Loss

$L_{Com}$  Combiner Loss

$L_{SP}$  Splitter Loss

$L_{DEMUX}$  DEMUX Loss

$L_{AWG}$  Array Waveguide Grating Loss

$L_{TWC}$  TWC Loss

$L_{FF}$  Fixed Filter Loss

$L_S$  Splice Loss

$L_{F1} = L_{F2}$  Fiber Loss

$L_S$  Splice Loss

$L_{BPF}$  Band Pass Filter Loss

$L_{SS}$  Space Switch Loss

$\Gamma$  Confinement Factor

γ Scattering Loss

$P_p$  Pump Power

# List of Acronyms

AGC Automatic Gain Control

ASE Amplified Spontaneous Emission

ATM Asynchronous Transfer Mode

AWG Array Waveguide Grating

BER Bit Error Rate

BL Burst Length

BPF Band Pass Filter

DEMUX Demultiplexer

DWDM Dense Wavelength Division Multiplexing

DXC Digital Cross Connect

E/O Electronic to Optical Conversion

EDF Erbium Doped Fiber

EDFA Erbium Doped Fiber Amplifier

FCC Fiber-to-Chip Coupling FCFS First-Come-First-Serve

FDL Fiber Delay Line

FF Fixed Filter

FIFO First-In-First-Out

ITU International Telecommunication Union

IP Input Pattern

IR Injection Ratio

MSN Manhattan Street Network

O/E Optical to Electronic Conversion

OADM Optical Add-Drop Multiplexer

OBS Optical Burst Switching

OPS Optical Packet Switching

OXC Optical Cross Connect

RCP Routing Control Processor

SNR Signal to Noise Ratio

SOA Semiconductor Optical Amplifier

TAG Tell-and-Go

TDM Time Division Multiplexing

TWC/TOWC Tunable Wavelength Converter

WDM Wavelength Division Multiplexing

# Chapter 1

## Introduction

The word telecommunications is made up of two words: tele (over a distance) and communications (exchange of information). Thus the exact meaning of telecommunication can be defined as the transmission of information over long distance using suitable equipments e.g., telephone. Most of the time, the information to be exchanged with others are voice, video and/or data. The information in these forms is transmitted using the transmitter. The transmitter processes the information appropriately (by multiplexing and/or modulating it) into the suitable format (electrical or optical signal) and then transmits it. The signal travels through communication links (transmission media) which can be copper wire, coaxial cable, optical fiber or free space. The intended receiver accepts this transmitted signal from the channel and processes it (by demodulating and/or demultiplexing it) to recover the information.

## 1.1 Evolution of Communication Techniques

In the first quarter of  $19^{th}$  century, the evolution of electrical communication was led by the invention of telegraphy. Data transmission was done with rates up to 10b/s by the

application of coding techniques such as Morse code. Alexander Graham Bell invented the telephone in 1876 and the first telephone line ever, which ran between the second floor and the basement of Bell's house, was an example of what's today called a point-to-point link. That dedicated link gave birth to the modern telecommunications, and this technique has dominated the communication systems for almost a century. With the use of coaxial cable, the system capacity increased up to 100Mb/s in 1970s.

In the past (till 18<sup>th</sup> century), the common method for transmission of information was fire and smoke signals as well as the reflecting mirror. Then some improvements had been done by the introduction of devices such as flags, signaling lamps or semaphores. Bell tried to send speech over a visible light beam in 1860 for distances of several hundred meters using photophones [4]. But these photophones were impractical because of the requirement of line of sight and the presence of the atmospheric disturbances such as rain, snow, fog, dust and turbulence. Maiman developed the laser in 1960 and this was the first production of coherent light [41]. The use of optical fiber based on silica glass as transmission medium had been proposed in 1966 [37]. These developments gave rise to the first generation of lightwave communication systems. The data rate achievable at that time was much better than that of electrical signal but still it was limited because of attenuation and dispersion in the fiber. In the initial phase, the fiber was operated at wavelength near  $0.8\mu m$  due to the availability of cheaper silicon detector. In the second generation of lightwave systems, the laser and detectors were invented for operation at  $1.3\mu m$  with attenuation of 0.35 dB/km and produced the optical data at 2Gb/s in 1980s [69]. The third generation of fiber optics communications is functional at  $1.55\mu m$  and 10Gb/s with attenuation of 0.2dB/km [22]. Simple optical communication links have been evolved to an extent where optical components and fibers are used to form the current fast growing optical networks.

## 1.2 Optical Networks

The bandwidth demand due to more and more data intensive applications is increasing day by day. Optical networks are the most suitable option for this increased bandwidth requirements due to the availability of large bandwidth in the fiber [16, 53, 68]. The optical network implementations can have electronic or all-optical switches. Electronic switches are easy to implement due to mature electronics technology but they have fundamental limitations on rates at which data can be transported from one switch to another switch. This limit is not because of communication channel (i.e., optical fiber) but due to modulation and demodulation limits in electronic transmitters and receivers respectively.

In optical transport networks, the current approach is to use optical circuit switches to set up light paths [1, 49, 59]. These all-optical switches are transparent to information carried over the light path. At the same time, optical circuit switching technology has made it feasible to have virtual topologies over an actual physical fiber topology (layout). It allows us to rapidly deliver the enormous bandwidth of WDM networks to the customer, while remaining inefficient at the physical layer. One requires packet switching for efficient use of the physical layer. The possibility of packet switching using photonic technologies allows all-optical packet switched networks where packets remain in optical form without undergoing optoelectronic conversion at intermediate nodes. Thus, photonic packet switching offers high speed (data rate), format transparency, efficiency and flexibility in configuration due to the switching operation in physical layer. Since the data is generated by electronic sources, the only motivation to build the all-optical packet switch is when ingress routers aggregate the large number of packets optically for very high bit rate payload. This can be attached with low bit rate

header and pushed into the core network. The all-optical packet switches in the core will convert the header of the packet to electrical form and keep the payload in optical form. The header information can be used to route the packet. Once the packet reaches the egress node, the aggregated packets can be separated optically and passed onto the client network [18, 19, 26, 33, 36, 48]. We can call them as aggregate core transport networks.

Wavelength division multiplexing (WDM) allows transmission of hundreds of channels in a single fiber where each channel may operate at the speed of 10Gbps to 40Gbps. Thus it increases the network capacity tremendously by harnessing the large available bandwidth of optical fiber, and it can also satisfy the ever increasing bandwidth demand [14, 17, 43, 46, 54].

# 1.3 Optical Packet Switching

One of the major issues involved in optical networking is the switch/router architecture which can perform the switching operation efficiently at such high data rates. In the last decade, several research works have been reported on the design of switches/routers. These switches are of various types: electronic, 'all'-optical or 'almost-all'-optical. The purpose of switching is to route the packet to the destined output port. The important aspects of photonic packet switching are control, packet synchronization, clock recovery, packet routing, contention resolution and packet header replacement [18, 64]. These are considered as the key issues for successful operation of an optical packet switch. Contention is one of these issues, which occurs when two or more packets arrive at the same time for the same destination. To avoid this contention, one of the contending packets is directed to the intended output port and other contending packets are either

1.4 Outline of Thesis 5

stored or dropped. All-optical memory suitable for optical storage has not yet been developed. The alternative is to use deflection routing [13] or optical fiber delay lines (in traveling or recirculating type configuration). Different techniques for optical buffering by using fiber delay lines have been proposed [7, 28, 31, 32, 56, 65] and still, the research is going on to explore better solutions. Optical buffers are much better than the electronic buffers because in case of optical buffers, the data path is: i) all-optical i.e., O/E and E/O conversion not required, ii) having larger bandwidth, iii) data rate transparent and iv) capable of supporting WDM. Optical buffering can be introduced in three ways: input buffering, output buffering and shared buffering [2, 6, 15, 20, 29, 31, 56]. Shared buffer optical switches are more advantageous as compared to the other two categories because it also provides switching alongwith buffering. These shared type buffers can be implemented in the optical switches either in the feedback or in the feed-forward manner [12, 30, 40, 74]. Both of these configurations have their advantages and disadvantages, and are used as per the requirement of the switch architecture.

## 1.4 Outline of Thesis

In the thesis, different aspects of optical buffering are investigated for various architectures of optical packet switching. Some new architectures are also proposed alongwith the buffering techniques and their analysis. The main objective is to utilize the optimal buffering parameters to provide least packet loss probability and reasonable average delay with the given resources.

The rest of the thesis is organized in following manner. Chapter 2 gives the basic overview of photonic packet switching architectures and the optical components used in these architectures. Chapter 3 deals with the proposed modification in the architectures.

1.4 Outline of Thesis

ture of staggering switch to improve its performance. In Chapter 4, we present a new approach of switching for data vortex architecture. Chapter 5 proposes a new optical packet switch architecture which uses loop buffer modules in feedback configuration. Power budget analysis is performed by taking care of various types of noise in the loop buffer module, and the number of maximum allowed circulations in the loop buffer is calculated. Mathematical analysis is also done to validate the simulation results as well as the proposed architecture. Chapter 6 discusses enhancements to the optical packet switch architecture proposed in Chapter 5. The main objective of these enhancements is to increase the number of maximum allowed circulations. In Chapter 7, we propose three architectures for optical packet switching based on wavelength routed feed-forward shared buffer modules. These architectures are developed by selecting three different combinations of space switch and Arrayed Waveguide Grating (AWG). One of these architectures is also analyzed in terms of power loss and noise power, due to the presence of various optical components in the loop buffer memory. Chapter 8 presents the comparative analysis of various optical packet switch architectures (discussed in the previous chapters), on the basis of optical cost and bursty traffic arrival. Finally, Chapter 9 concludes the thesis along with some suggested future works.

# Chapter 2

# Photonic Packet Switching Architectures - A Literature Survey

In this chapter, we briefly discuss the issues related to photonic packet switching and their architectures<sup>1</sup>. We will also give a brief detail of few optical components which are commonly used in various switch architectures of the following chapters.

## 2.1 Electronic Packet Switching Technologies

The goals of a packet switching system are high throughput, low latency, low packet loss and effective prioritized processing. At the architectural level, several parameters need to be chosen/rejected before converging onto a suitable design. Some of these parameters are switching fabric structure, buffering and queuing strategy, scheduling algorithm and flow control. Basic switching fabric can be of different sizes depending upon several constraints such as maximum permitted blocking probability. One can configure the switching fabric in the form of either a large element in single stage or

$<sup>^1</sup>$  "An overview of photonic packet switching architectures," IETE Tech. Rev., Vol. 23, No. 1, pp. 15-34, 2006.

Figure 2.1: Multi-stage Interconnection Network

several small elements in multiple stages. Multistage interconnection networks e.g., Clos network and Banyan network (Figure 2.1), can be used for configuring larger switches using smaller ones [34].

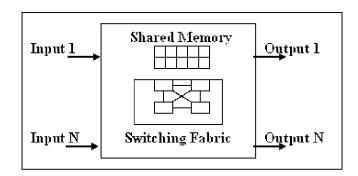

Multiple packets arriving at the same time from different input ports may be destined to the same output port, and will cause contention for that output port. In this condition, one of the contending packets will be passed to the destination and the rest of the contending packets will be stored, if possible, in the buffers to avoid the loss of packets. These buffered packets are queued using an appropriate algorithm and delivered to the designated output port in later free time slots. These buffers can be placed at different locations in the switch [70] and depending upon the placement, buffering can be classified as Input buffering (Figure 2.2), Output buffering (Figure 2.3) and Shared buffering (Figure 2.4).

Figure 2.2: Input buffering arrangement

Figure 2.3: Output buffering arrangement

Figure 2.4: Shared buffering arrangement

# 2.2 Optical Packet Switching Technologies

Optical packet switching can be categorized as 'almost-all' and 'all' optical switching. In both types, the data path is fully optical, but they differ in control functionality. In 'almost-all' optical switching, the control of switching operation is done electronically while in 'all' optical switching, the control is expected to be fully optical or optoelectronic. Optical packet switching can be further subdivided into (a) Photonic Packet Switching, and (b) Optical Burst Switching.

#### 2.2.1 Photonic Packet Switching

Photonic packet switching combines high capacity of optical links as well as fine granularity and efficient multiplexing of packet switching. The wide bandwidth of photonic components, combined with the flexibility of WDM and the high speed capabilities of optical devices, provides the potential for building packet switched networks with throughputs in the range of terabits per second (Tbps) [64, 72]. Some of the critical issues involved in designing and implementing photonic packet switches are:

- 1. Switch Architecture,

- 2. Header and packet format,

- 3. Routing Strategies,

- 4. Contention Resolution and Switching,

- 5. Synchronization, and

- 6. Header Regeneration.

#### 2.2.1.1 Switch Architecture

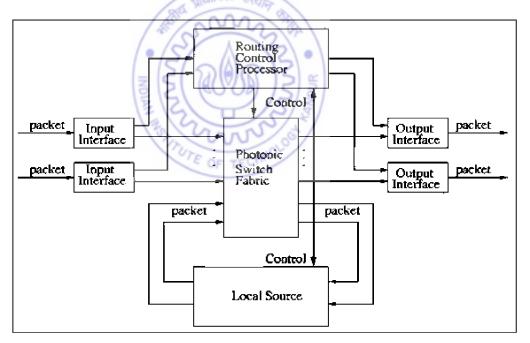

Photonic packet switches can be modelled in terms of the constituent subsystem (Figure 2.5) i.e., the photonic switch fabric, the routing control processor (RCP) and the input & output interface units [7]. The switch fabric creates optical connection between input and output, which may be one-to-one, one-to-many or many-to-one. The RCP sets the connection state of the switch, while taking care of internal blocking state and output port contentions. Several photonic packet switch architectures have been proposed, and all of them use photonic means to perform packet buffering and routing; while electronics is used for address processing, routing and buffering controls [64].

Figure 2.5: General Architecture of Photonic Packet Switch

These switch architectures are classified in the following ways:

(a). Space-Switch based Photonic Packet Switch: A space division switch simply provides the ways for the transmission of packets from inputs to the respective

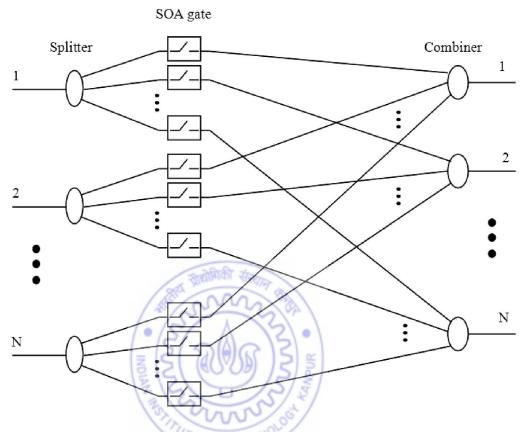

outputs. For an example, space switches can be implemented using semiconductor optical amplifiers (SOA) as the basic transmission gate. An  $N \times N$  space-switch based on SOA gate is shown in Figure 2.6. It consists of N splitters of  $1 \times N$  size,  $N^2$  SOA gates and N combiners of  $N \times 1$  size. Each input i split to N gates and if the signal at that input is to be switched to output j, then the  $j^{th}$  gate is switched to ON state and all others are kept in OFF state.

In the context of photonic packet switching, optical space switches are required to have a switching speed in the range of several nanoseconds as the switching time has to be less than 10% of a packet time to achieve a high utilization in transmission. Further, low crosstalk and low power loss is desirable. The staggering switch [28] (described in chapter 3) is an example of space switching based optical packet switch. It uses space switches to perform packet routing and buffering.

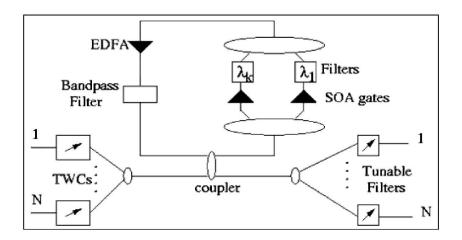

(b). Broadcast-and-Select Packet Switch: In this approach, information from all the signal sources is multiplexed by a star coupler and distributed to all the receivers where each receiver selects the desired packets. Both TDM and WDM can be used in this approach. An example of this type of switch is shown in Figure 2.7. It consists of N tunable wavelength converters at the input, a random wavelength accessible recirculating loop buffer, and N tunable filters at the output [5]. The loop buffer is shared by all the packets from all the inputs. Before entering the buffer, each packet is assigned a wavelength not being used by any other packet within the buffer. All the packets in the buffer are broadcast to all the outputs. The tunable filter at each output selects appropriate packets by tuning its transmission wavelength. The packets which are selected by the tunable filters are cleared out of the buffer by turning off the corresponding gate switches in the buffer. An electronic controller tracks N packet queues corresponding to N outputs of the switch.

Figure 2.6: SOA gate based space division switch

Figure 2.7: Broadcast-and-select photonic packet switch

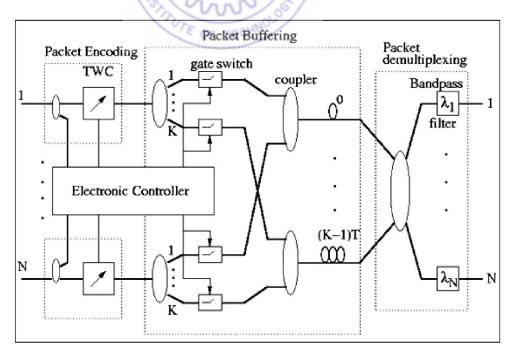

(c). Wavelength-Routed Photonic Packet Switch: This type of packet switch uses wavelength coding for packet routing and buffering. An example is shown in Figure 2.8. It consists of three functional blocks: a packet encoding block, a buffering block and a packet demultiplexing block [64]. The packet encoding block comprises of N optical tunable wavelength converters (TWCs), and each of these convert the incoming packets to the wavelength corresponding to its desired output i.e., a packet addressed to the  $i^{th}$  output is assigned a wavelength  $\lambda_i$ . The buffering block consists of an  $N \times K$  SOA gate switch matrix followed by a set of K optical delay lines whose lengths range from 0 to (K-1) packet times. The wavelength encoded packets are provided access to appropriate delay lines using SOA gate switch matrix. This is done in such a way that the packets, destined for a given output, leave the switch following the first in first out (FIFO) scheme. FIFO is a queuing discipline where the packet entering earlier in the queue for an output is always sent to that output, earlier than all the packets arriving later.

Figure 2.8: Wavelength routed photonic packet switch

The demultiplexing block consists of a  $K \times N$  star coupler followed by a set of N bandpass filters, one at each output to select packets whose wavelengths matches with its passband. An electronic controller is used to control the TWCs and space switches to implement the switching function. In this architecture, the number of SOA gates required in the buffering blocks increases proportionally to the product of N and K. Also, the optical power loss of a packet is proportional to  $NK^2$  (for N < K) or  $N^2K$  (for N > K). This limits the scalability of the switch.

#### 2.2.1.2 Header and packet format

A packet can be functionally described using a layered model. At the physical level, there are effectively two such layers: the header and the payload. The *header* contains information processed only by the switches. It may include destination address, priority, packet empty-full bit and packet length. The *payload* contains information processed only by the sources and destinations. It may include data, packet number and source address.

In electronic networks, routers or switches will process the header information arriving at the same data rate as the payload. In an N port switch, the control processor should be able to process on an average  $N \times L$  headers in a slot duration. Here, L is the maximum loading per line for which, that switch is designed. This will ensure that no packet is dropped because of the unprocessed header. In an optical network, the bandwidth is much larger than their electronic counterpart and hence, the slot duration for packets will also be small. As a consequence the number of headers which can be processed in a slot time, reduces drastically for the same processor thereby limiting the switch size. Alternatives to resolve this problem are as follows: i) to use larger packet size and hence larger slot size or ii) for smaller slot size, use smaller size switches with

their own processors and interconnect them to make a large switching network; this is distributed switch or iii) make the header format simple enough for faster processing.

In the literature [7], three basic categories for optical packet coding have been proposed to make the header processing faster. These are bit-serial, out-of-band-signaling, and bit-parallel. Each of these techniques exploit the data rate and format transparency of optical devices. These techniques are well described in [7, 59] alongwith their comparative analysis.

#### 2.2.1.3 Routing Strategies

Routing is the mechanism which chooses a preferred path to send a packet from its source to destination. Routing control is a mechanism which configures the paths in switches to facilitate the movement of a packet to the next chosen switch. It may be centralized or distributed. Centralized control involves a single processor monitoring the network and setting up the switch state according to the routing request. But, as the networks become large or incorporate more switches, centralized control increases latency, degrades throughput, and also increases processing complexity. In Distributed control, packets carry destination information for independent processing at each node. This form of processing reduces the burden on a centralized processor and increases the switch/network throughput. Additionally, the distributed routing decisions are based on local information, whereas the centralized routing decision are made on global and perhaps obsolete information. A hybrid of centralized and distributed routing control may provide optimal performance by combining advantages of both the techniques.

#### 2.2.1.4 Contention Resolution and Switching

In a packet switched network, each packet has to pass through a number of nodes (switches) to reach its destination. When the packets are being switched, contention occurs whenever two or more packets are trying to leave the switch from the same output port at the same time. The contention is resolved using various techniques: deflection routing, optical buffering and wavelength conversion. If contention cannot be resolved then one of these contending packets, chosen using a certain algorithm, is passed and others are dropped.

- (a). Deflection Routing: Internal conflicts between two packets can be resolved by correctly routing one packet while deflecting the second packet to another available outgoing link. Routing decisions for deflection of packets are based on destination address and packet priorities. Deflection routing techniques require that the network topology should be multi-path or re-circulatory, so that the deflected packets can be routed to the destination following an alternate path [13]. The priority of deflected packet is increased to reduce the end-to-end latency and to avoid deflecting a packet indefinitely. The number of input links to a switching node should be equal to the number of output links. Performance of this technique decreases monotonically as the number of nodes increases [7]. This degradation can be compensated either by increasing the link speed or by reducing the probability of deflection.

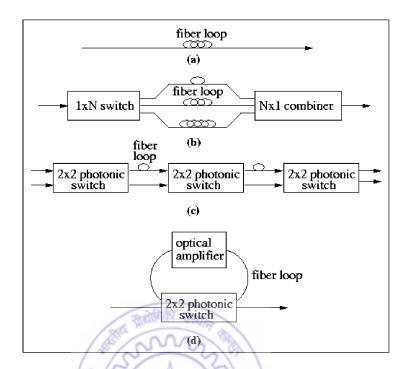

- (b). Optical Buffering: The storage of optical data in the fiber delay lines (FDL) is known as optical buffering. This technique is classified into two basic categories: traveling and recirculating type. A traveling type buffer generally consists of several FDLs whose lengths are equal to the integral multiples of a packet duration T. It also incorporates optical space switches to select from the available delay lines. The storage

time of a packet is simply determined by the delay line through which the packet is propagating. A recirculating type buffer consists of a single FDL forming a loop with a circulation time equal to one packet duration. The storage time of a packet in such a recirculating type buffer is determined by the number of times the packet circulates in the delay line. Both types of the buffers are able to store multiple packets with the constraints that only one packet enters and leaves the buffer at any point of time.

The recirculating type buffer is more flexible than the traveling type buffer as the packet storage time is adjustable by changing the number of recirculations. On the other hand, the storage time of a traveling type buffer is predetermined by the length of FDLs. The problem associated with recirculating type buffer is that the signal has to be amplified after a few circulations to compensate for the power loss. This results in accumulation of amplified spontaneous emission (ASE) noise from the optical amplifier, which eventually limits the maximum buffering time [57]. In addition, the gain from the optical amplifier has to be carefully controlled i.e., the product of gain and the loss in one circulation should be slightly less than unity to prevent optical signal lasing.

Optical buffers can be placed at the input or output of the optical cross connects. They can be configured in different forms (Figure 2.9): (a) Fiber delay line, (b) Programmable fiber delay line, (c) Feed-forward time slot interchanger, and (d) Active switched recirculating delay line.

(c). Wavelength Conversion: Deflection routing and Optical buffering could be regarded as deflection in general, one in the space domain and the other in the time domain respectively. Both have their advantages and disadvantages: deflection is easier to implement but cannot offer ideal network performance while buffering offers better network throughput but involves more hardware and control. When combined with

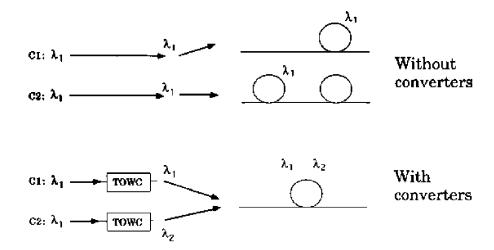

Figure 2.9: Different types of optical buffers

wavelength conversion, these disadvantages could be overcome or minimized. The wavelength domain presents one more dimension for deflection of the contending packets. In a switching node applying wavelength conversion and buffering, the input stage demultiplexes wavelength channels and the wavelength converters transfer them to available wavelength. A nonblocking space switch selects the output port or appropriate delay line for switching of these transformed packets. Wavelength conversion has been shown to reduce the number of optical buffers (Figure 2.10) and also the packet loss probability [17]. When the nodes are provided with a number of optical receivers/transmitters equal to the number of wavelengths, hot-potato routing in conjunction with wavelength conversion [8] becomes an interesting option for mesh topologies such as Manhattan Street Network (MSN) [13] and ShuffleNet [38].

However, wavelength conversion provides noise suppression and signal reshaping while the delay lines are more effective in solving contention. Therefore, the use of

Figure 2.10: Wavelength Conversion

wavelength conversion depends on the specific network. In a network with only a small number of wavelengths, buffering might be more desirable whereas in the networks with a large number of wavelengths capacity and full wavelength conversion capabilities at nodes, buffers may not be the appropriate choice. Some times both are jointly used to utilize the advantage of optical buffering as well as wavelength conversion.

E OF TECY

#### 2.2.1.5 Synchronization

Synchronization is a fundamental issue that must be addressed when combining individual photonic switches into centralized or distributed switching networks [21]. In order to perform successful routing, proper alignment of packets within the switch fabric and that of headers within the RCP is needed to be done.

In general, optical packet switched networks can be divided into two categories based on synchronization: slotted (synchronous) and unslotted (asynchronous). Since the state of the switch fabric can only be changed at discrete times, it is crucial for the network designer to decide whether (or not) to have all the input packets aligned before they enter the switch fabric. In both these cases, bit-level synchronization and fast clock recovery are required for packet header recognition and packet delineation.

In a slotted network, all the packets have same size. They are placed together with the header to form a fixed time slot. The duration of this slot will be kept longer than the total duration of packet and header. This provides sufficient guard band between packets. In most cases, optical buffering is implemented by using fiber loops or delay lines with a propagation delay either equal to or a multiple of the time slot duration. This leads to the requirement that all input packets arriving at the ports have the same size and are aligned in phase with a local clock reference. In an unslotted network, the packet may or may not have the same size. Packets arrive and enter the switch without being aligned. Here, the chance of contention is larger because the behavior of packets is more unpredictable and less regulated. Buffering in optical domain in these networks is much more complex [72]. On the other hand, these switching networks will be more robust and flexible than the slotted networks. With careful design of node architectures and protocols according to the network specifications, satisfactory performance can be achieved even in unslotted systems.

#### 2.2.1.6 Header Regeneration

Header regeneration involves computing, generating and reinserting a header with the associated payload before it leaves the appropriate switch output port. There are several circumstances where this functionality is required e.g., in an all-optical photonic packet switch where the header is completely removed from the payload for processing, or where the routing strategies require a modification of the packet header. It is important that the header regeneration technique should be able to operate for cascaded switches and is independent of the number of switches, the packet traverses.

#### 2.2.2 Optical Burst Switching (OBS)

Optical packet switching (OPS) technology still faces cost and technology hurdles, the most notable of which is the non-existence of random access optical buffer memory. An alternative technique named as optical burst switching represents a balance between circuit and packet switching [3, 11]. It provides an optical networking solution that delivers the benefits of OPS while avoiding the need of optical buffer memory and other hurdles. OBS sends control packets on separate wavelengths ahead of a variable length data burst in order to reserve the bandwidth resources as a 'burst circuit' prior to the arrival of each data burst. As the burst passes, the resources are released. Functionally, such instantaneous circuit switching avoids the need of buffer memory along the path to handle the traffic bursts. In addition, synchronization requirements are less stringent than in OPS due to looser coupling between control signals and data in OBS. Finally, since control packets are much smaller than the data payloads, one or two control wavelengths can support a large number of data wavelengths. Optical burst switching can be summarized in the following points:

- a) A control header is sent first along a separate control channel to set up a connection while data packets awaiting transport are accumulated into a data burst, and are stored in electronic memory at the edge of the network.

- b) After an offset time, the data burst is sent without waiting for an acknowledgment that the connection was established. This one-way reservation protocol is similar to tell-and-go (TAG) switching and results in reduced latency.

- c) By choosing an offset time larger than the total processing time of the control packet all along the path, the data burst passes straight through without any

buffer requirement at any intermediate nodes on the path.

- d) The ability to accumulate and send from one to thousands of packets using one control packet results in low processing and synchronization overhead per unit data.

- e) In a situation when either the path is not feasible or the consumed processing time for header exceeds the offset, the burst is dropped.

The wavelength on a link used by a burst, is released as soon as the burst passes through. This allows multiple bursts to share the same wavelength on the same link in a manner that is time shared and multiplexed statistically. This yields high bandwidth utilization, high adaptivity to congestion/faults and sub-wavelength granularity for low-bandwidth customers and services. When more than one burst contend for a resource, only one burst is permitted as per the resolution algorithm.

# 2.3 Optical Switching Components

# 2.3.1 Optical Fiber

All the telecommunications were done by copper wire till 1980's i.e., before the evolution of fiber as mature technology as another form of transmission media. The optical fiber medium provides several advantages over copper e.g., lower attenuation and no electromagnetic interference. The major advantage of optical fiber is very high optical bandwidth of the order of tera-hertz (THz). Although the fibers are lighter and stronger than copper, they have some problems such as dispersion, attenuation and nonlinear refraction. A fiber consist of a core which is surrounded by the cladding, both of which

are made by pure silica glass but having different refractive index. The refractive index of the core is slightly greater than the cladding.

The transmission of light inside fiber is possible due to the phenomenon of total internal reflection. Alternatively, one can use Maxwell equations solutions with appropriate boundary conditions to determine the field profiles (modes) which can be guided inside the fiber. The optical fiber can be either single-mode or multimode. Modes are labelled as  $TE_{MN}$  or  $TM_{MN}$  depending upon the value of the transverse electrical field  $(E_Z)$  or the transverse magnetic field  $(H_Z)$  at the surface of the fiber core in the transverse direction. Fibers that support many modes are known as multimode, and those that support only one mode are known as single mode. The core diameter of multimode fiber is much larger than that of single mode fiber.

# 2.3.1.1 Optical power penalties

The propagation of light inside the fiber is affected by various types of parameters, few of these are described below.

- (a) Attenuation: Attenuation is the decrement in the power of an optical signal during its propagation in the fiber. This decrease in signal strength is caused by absorption, scattering and radiative losses. Silica glass fibers have minimum attenuation near 1550nm (0.25dB/Km) which is the most commonly used wavelength for long haul telecommunication applications. Radiative loss is minimized by designing the fibers with sufficiently thick cladding ( $\simeq 125\mu m$ ) and by minimizing bending losses. Scattering losses can be limited by making optical fiber using very high purity raw materials.

- (b) Dispersion: Dispersion refers to the broadening of optical signals as they propagate along the fiber. As the pulses broaden, they tend to interfere with adjacent

pulses and limits the maximum achievable data rate. Also, it leads to inter-symbol interference in communication links thereby increases the BER (bit-error rate). In multimode fibers, there are two dominant types of dispersion: modal and chromatic. *Modal dispersion* refers to the fact that different modes will travel with different propagation constants and cause pulse broadening. The *chromatic dispersion* occurs because different wavelengths of light propagate at different velocities in the fiber. The single-mode fiber does not suffer from modal dispersion.

(c) Crosstalk: Crosstalk denotes any distortion of a channel caused by the presence of another channel [25, 50]. Two types of crosstalk arise in a WDM system: (i). Heterodyne crosstalk due to interference of small power levels that appear outside the bandwidth of the channel and cause bit error rate increment when detecting the signal of interest. It is also known as interchannel crosstalk where the crosstalk signal is at a wavelength sufficiently different from the desired signals's wavelength and the difference is larger than the receiver's electrical bandwidth. (ii). Homodyne crosstalk results from interference within the channel's bandwidth. It is also known as intrachannel crosstalk where the crosstalk signal is at the same wavelength as that of the desired signal or sufficiently closed to it, and the difference in wavelength is within the receiver's electrical bandwidth. Intrachannel crosstalk effects can be much more severe than interchannel crosstalk. But in both the cases, crosstalk results in power penalty.

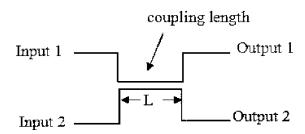

# 2.3.2 Couplers

Couplers are passive optical components which are used to combine and split signals in the optical networks [50]. A  $2 \times 2$  coupler consists of two input and two output ports as shown in Figure 2.11. It can be constructed by carefully fusing two fibers together

Figure 2.11: A  $2 \times 2$  coupler

in the middle by keeping a certain coupling length (L). The coupler can be modelled by two parameters: a) insertion loss and b) split ratio. The coupler takes a fraction  $\alpha$ (coupling coefficient) of the left over power after insertion loss from input 1 and places it on output 1, and the remaining fraction  $1 - \alpha$  is given out on output 2. Similarly, a fraction  $1 - \alpha$  of the left over power after insertion loss from input 2 is distributed to output 1, and the remaining power  $(\alpha)$  to output 2. Hence, if  $P_1$  is the power input at port 1 and  $P_2$  at port 2 then the power output at port 1 and port 2 is given by

$$\begin{bmatrix} (P_1)_{out} \\ (P_2)_{out} \end{bmatrix} = (1 - L_i) \begin{bmatrix} \alpha & (1 - \alpha) \\ (1 - \alpha) & \alpha \end{bmatrix} \begin{bmatrix} (P_1)_{in} \\ (P_2)_{in} \end{bmatrix}$$

(2.3.1)

Here,  $L_i$  is the insertion loss which happens due to scattering and coupling into radiative modes. The  $\alpha$  depends upon the length of the coupling region.

The couplers are used to tap off a small portion of the power from the incoming signal for detecting the header of the packet and for other monitoring purposes. These are designed with values of  $\alpha$  close to 1 i.e., 90 or 95%. The 3dB coupler is commonly known as  $2 \times 2$  coupler which divides the incoming powers equally and transmits it to each of the output ports. It can be made by choosing such coupling length which provides  $\alpha = 0.5$ . One can also make an  $N \times N$  star coupler,  $1 \times N$  splitter and  $N \times 1$  combiner by appropriately interconnecting a certain number of 3dB couplers.

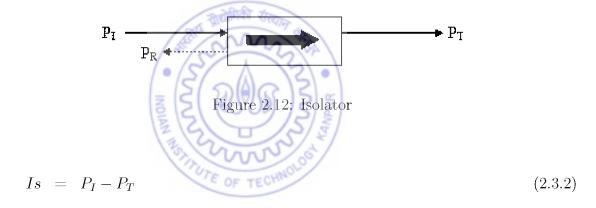

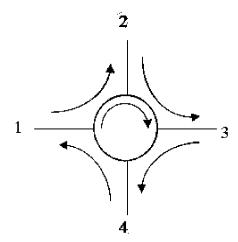

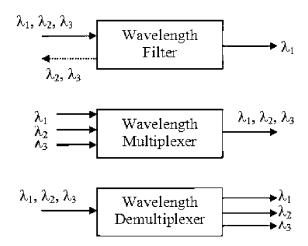

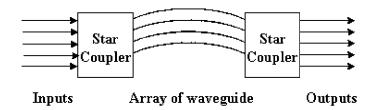

#### 2.3.3 Isolators and Circulators