Research Interests

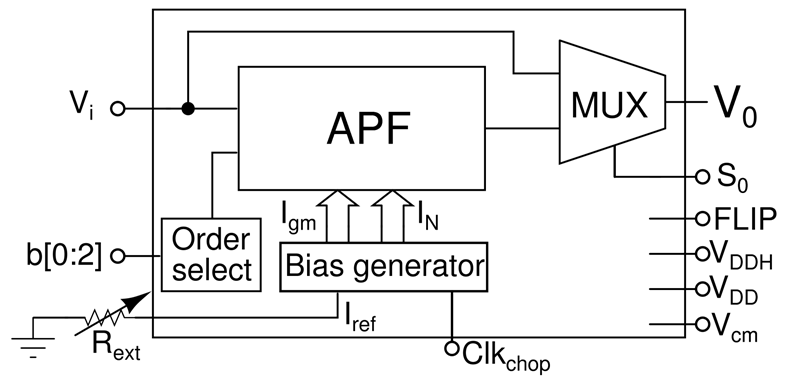

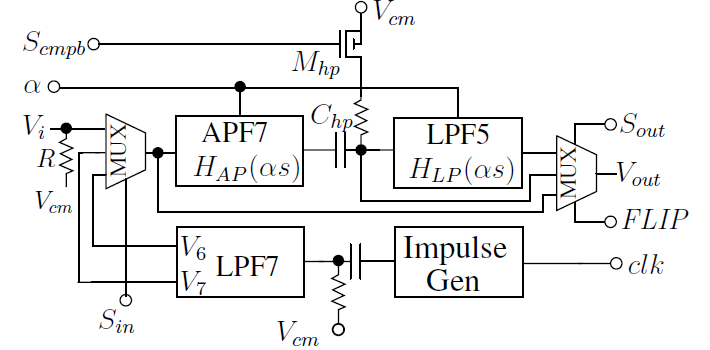

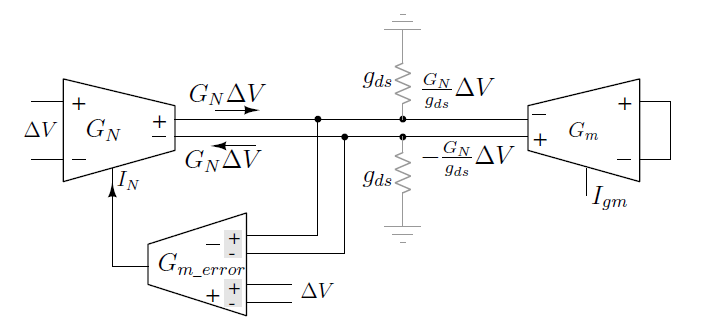

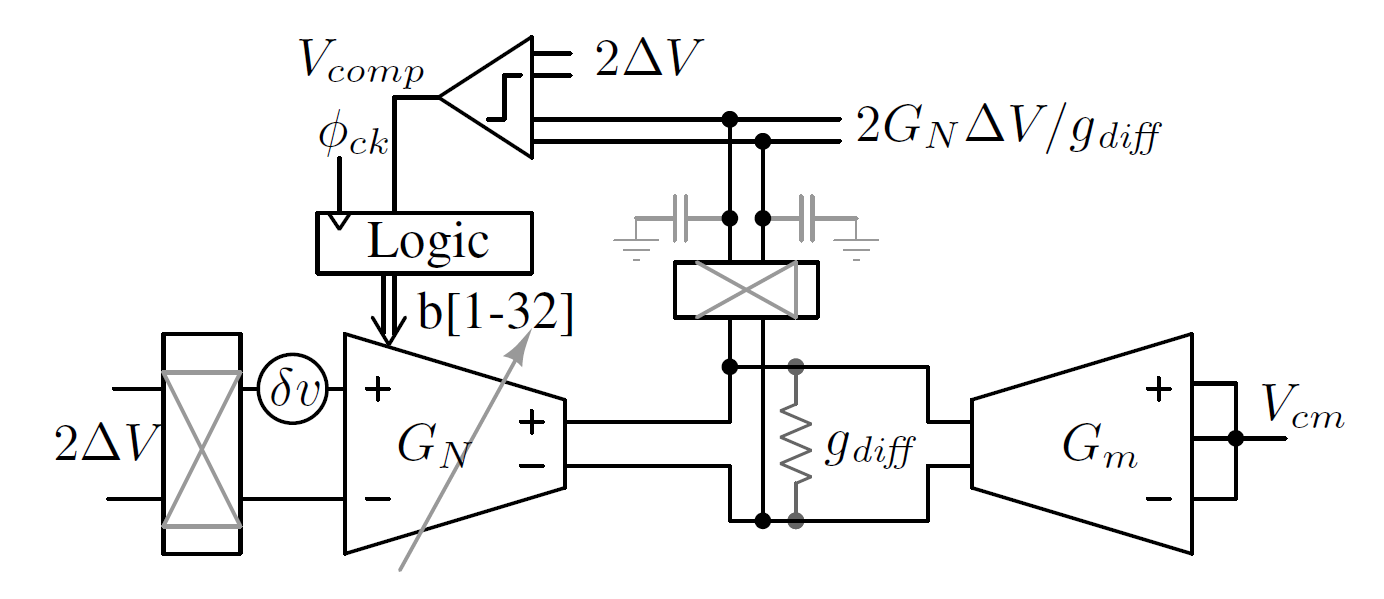

I work in the domain of analog circuit design for integrated circuits, primarilly aimed at signal processing. This involves conceptualization of the problem statement, designing an analog circuit solution, sending out the chip for fabrication (typically called tape-out), designing the PCB for testing the chip, and finally validating the simulation results through measurement results of the chip. My research work till date has concentrated on design of high frequency analog filters for various applications like design of true-time-delay elements for wideband beamformers on integrated circuits, and expansion and compression of wideband analog pulses.

If you are intersted in working with me, do apply for research positions through the IITK portal, and send me your C.V. There are open research positions both for M.S. and Ph.D. candidates. You can learn more about the programs here.