Research

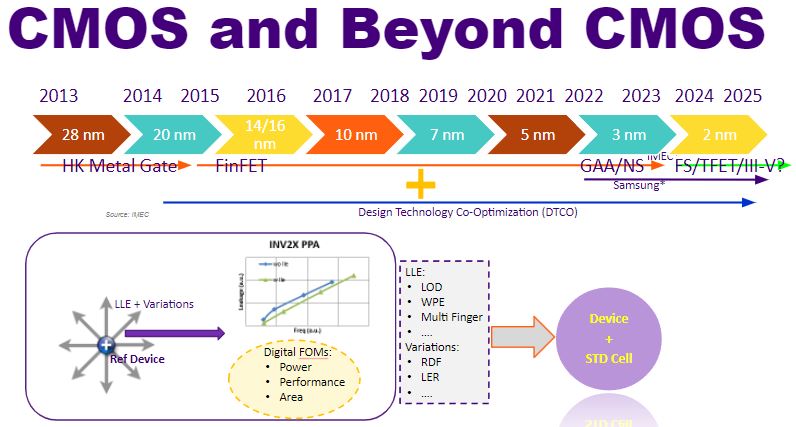

CMOS and Beyond CMOS

The continuity of Moore’s law drives the technological advancement from mainframe

computers to mobile devices that fit in our pockets. Moreover, to enhance computing performance,

a transistor with a small feature size is required to perform better at higher speeds. However, the aggressive

scaling of CMOS results in increased short channel effects (SCEs), which restricts the scaling of the CMOS in

the sub-10 nm regime. Also, the ever-increasing role stress engineering effect due to scaling raises a major

concern regarding the local layout effect (LLE). The LLE has a strong impact on the device and circuit

performance in advanced technology nodes. Therefore, these challenges need to be investigated in greater

detail. In this area, we would like to address the scaling and LLE challenges of the CMOS. Broadly,

our research efforts are:

- Developing novel devices and circuits for more-of-Moore and more-than-Moore applications

- Investigating emerging device architecture incorporating new materials that will enable aggressive operating voltage scaling for energy efficient computing applications

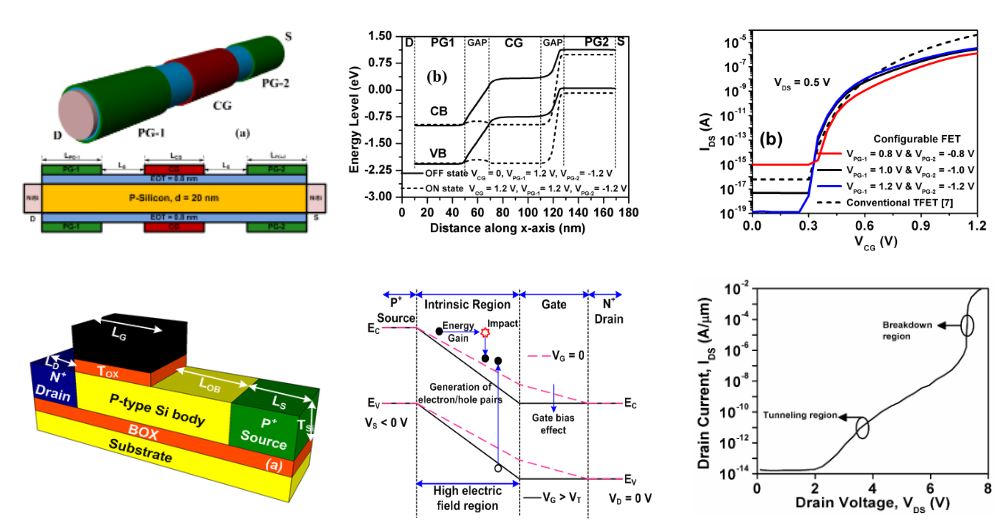

Steep Sub Threshold Slope FET

CMOS scaling has fueled innovations that led to an era of the internet of things (IoT) and big

data. However, the incessant scaling of the MOSFETs has attained its physical limits particularly due to the

Boltzmann tyranny of 60mV/decade sub-threshold swing (SS) which is difficult to scale down below

60mV/decade. Thus, the static power consumption in integrated circuits (ICs) is progressively increasing with

conventional MOSFET scaling. The probable solution to overcome this CMOS scaling bottleneck is to enable

an alternate conduction mechanism i.e. band-to-band-tunneling or impact ionization based on steep sub-threshold

swing devices such as Tunnel FETs (TFETs) and impact ionization MOS (IMOS). In this area, we would like to address the limitation of TFET and IMOS devices.

Broadly, our research objectives are:

- Develop a new TFET and IMOS device platform to demonstrate highly scaled and high performance

for von-Neumann computing systems

- Explore circuit level implementation of TFET and IMOS device in ULSI logic using device-circuit cosimulation approach

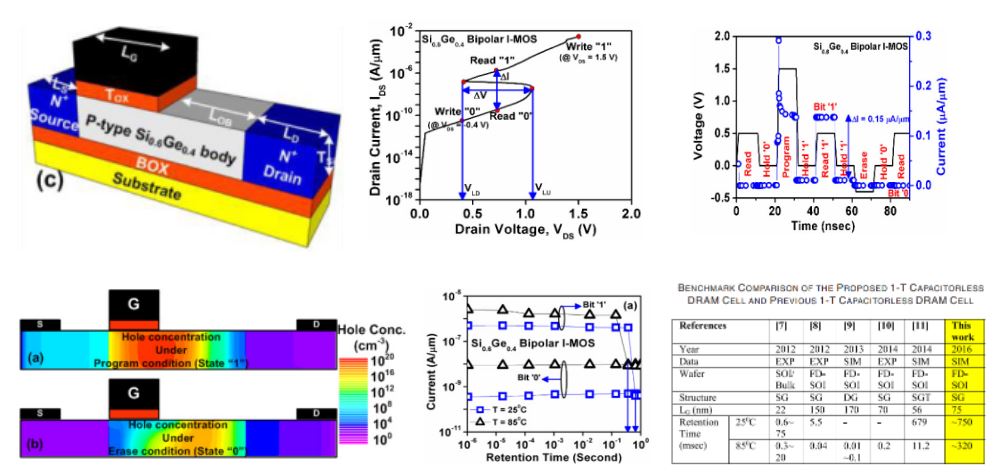

Single Transistor Dynamic Random Access Memory

In today’s era, DRAM chips are extensively used in electronic devices such as in main memories of mainframes, workstations, and personal computers and recently in working memories of mobile phones and digital electrical home appliances, thanks to high-speed operations, large integration density, and excellent reliability. Furthermore, we have eye-witnessed an exponential growth in the number of DRAM memory cells per chip due to its inherent simple structure. However, the DRAM scaling has reached its bottleneck in particular due to the capacitor which has become harder to scale, as MOSFET geometries scale. In this area, we would like to address the scaling constraints of the DRAM using single transistor DRAM. The single transistor DRAM exploits tunneling and impact ionization conduction mechanism for memory operations. The key research objectives are:

- Investigation of the proposed TFET and IMOS devices for single transistor DRAM application

- Cell array level implementation of TFET and IMOS based single transistor DRAM for PPA analysis

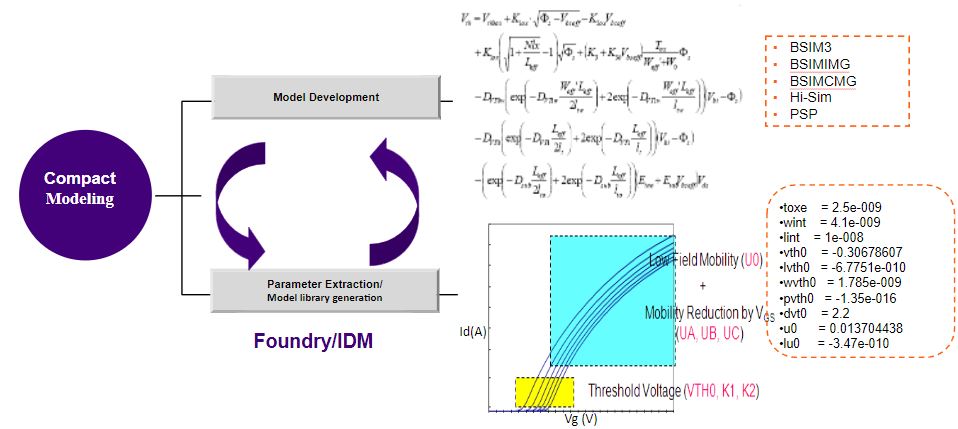

Compact Modeling

A compact model is a mathematical representation of all the physical phenomena encountered in semiconductor devices as shown by technology for Computer-Aided Design.

The compact model helps to anticipate circuit functionality, performance, and even yield prior to wafer processing. It allows circuit sensitivity analysis such as temperature, voltage supply, or process variations. With the continuous miniaturization of technology nodes, several new effects are coming into the actions, which need to be modeled. In this regard, the key research objectives are:

- Develop a compact model for novel CMOS devices and circuits

- Develop a compact model for statistical effects

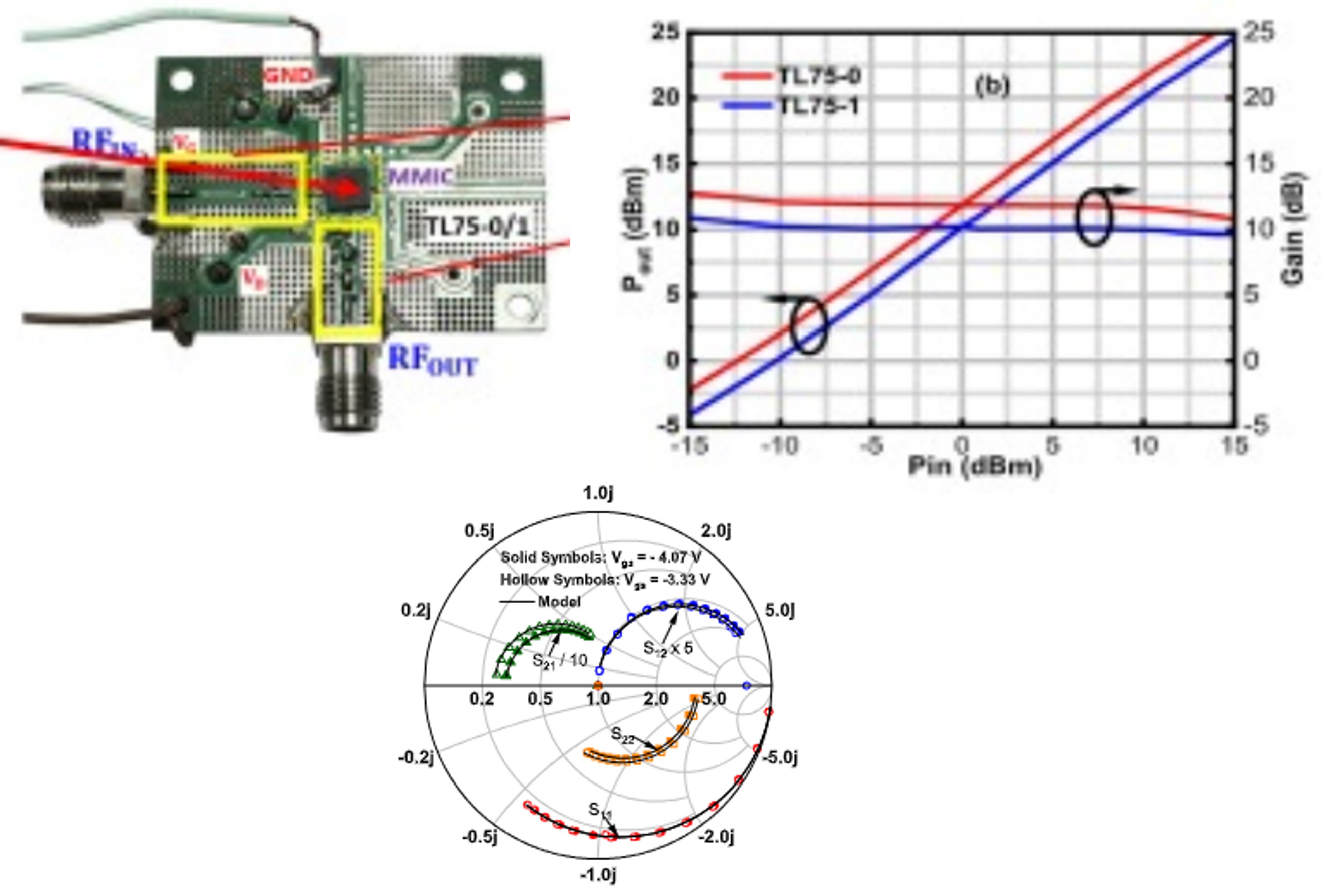

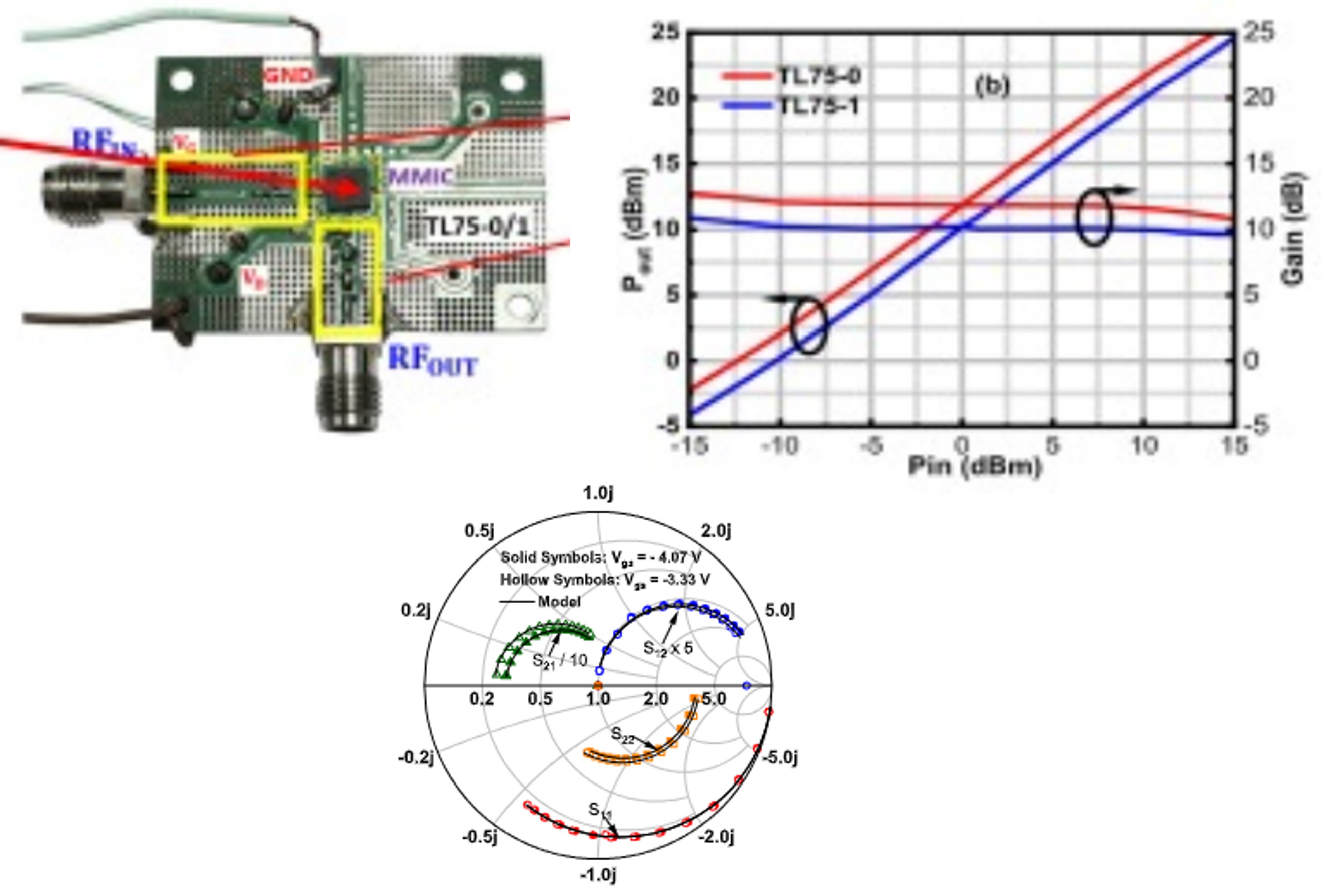

GaN HEMT based RF Circuits

The growing demand for the millimeter-wave (mmW) band (30-300 GHz) is driven by its shorter wavelengths and wider frequency bands, enabling the development of smaller components with enhanced performance. Monolithic microwave integrated circuits (MMICs) based on GaN technology play a critical role in fulfilling the requirements of the mmW range. Our reserach interest focused on:

- Develop a compact model for D-model and E-mode Gan HEMT devices.

- Examination of GaN-based devices for mmW applications, such as high-power amplifiers, and low noise amplifiers

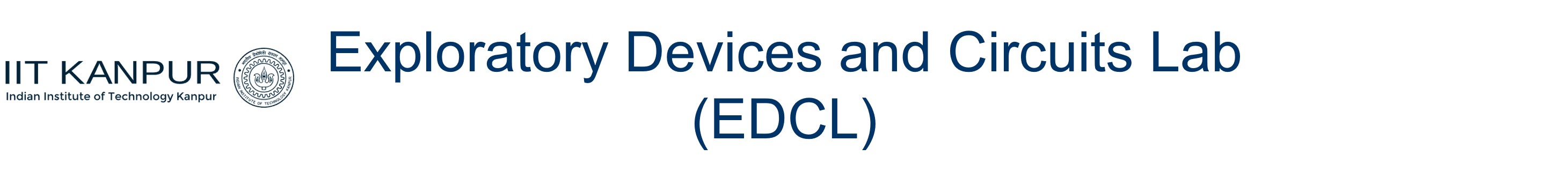

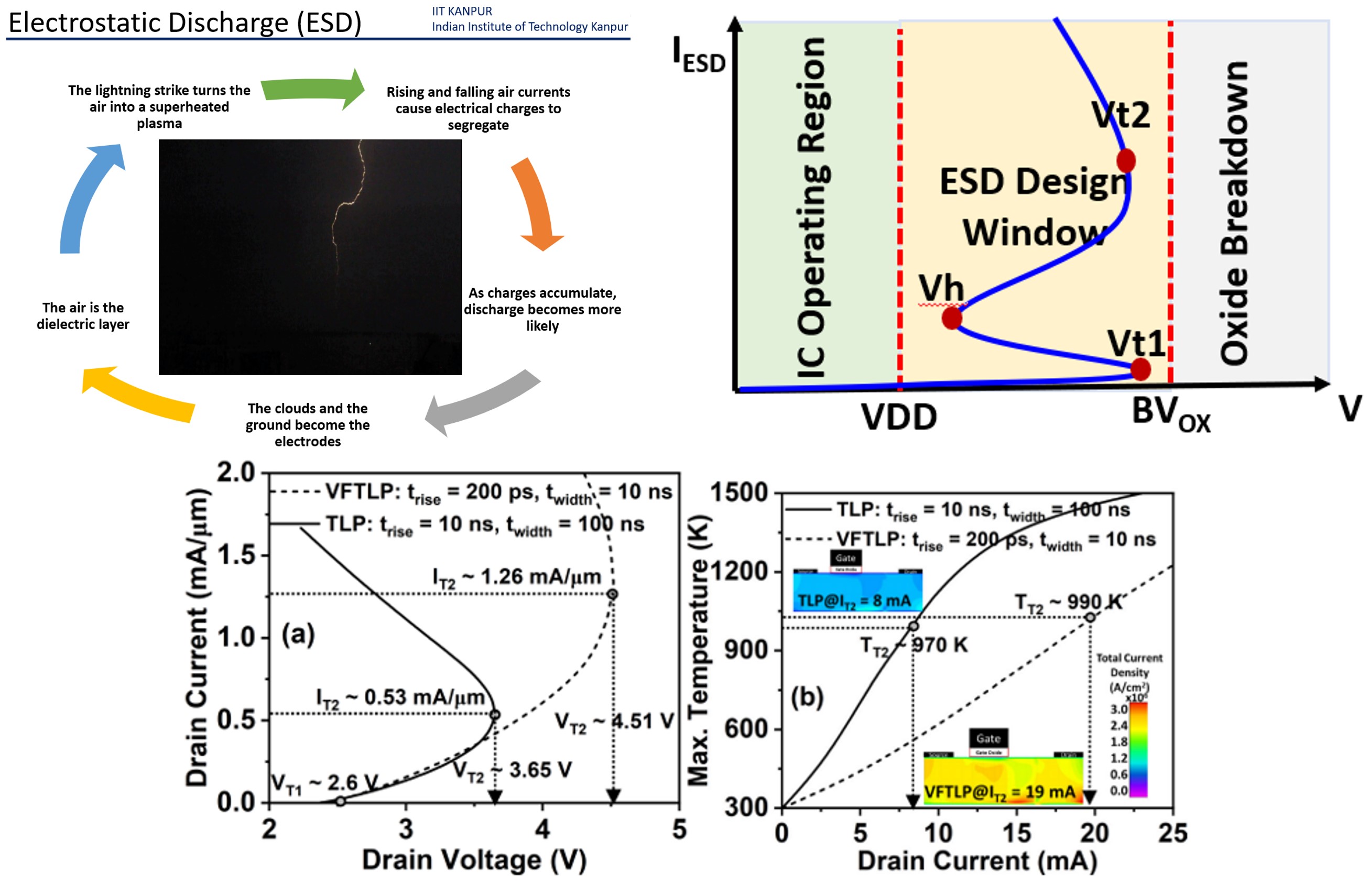

ElectroStatic Discharge (ESD) Protection

Electrostatic discharge (ESD) is a serious threat in the semiconductor industry, capable of

causing failures and damage in electronic devices due to rapid electrical charge transfer.

Voltages during ESD incidents can exceed device limits, resulting in failures like dielectric

breakdown and thermal damage etc. Therefore, our reserach interest focused on:

- Develop a compact model for ESD protection devices.

- Investigation novel device architectures for ESD design.

On-Going Project

1. PI : Reliability Characterization and Modeling of CMOS Devices; Agency: IIT Kanpur; Amount: Rs. 25 Lacs; Duration: 2022 - 2024.

2. PI : Evaluation of Radiation Resiliency on Emerging Single Transistor Dynamic Random Access Memory; Agency: Science and Engineering Research Board (SERB); Amount: Rs. 41 Lacs; Duration: 2023 - 2026.

3. PI : Reliability Characterization of CMOS Devices Measurement Lab: IIT Kanpur; Amount: Rs. 1.05 Crore Duration: 2023 - 2024

4. Co-PI : RF Characterization and Compact Modeling of Wide Band-Gap Gallium Nitride (GaN) Devices for the Next Generation Wireless Communication: Science and Engineering Research Board (SERB); Approved

5. Co-PI : Design and Technology Co-optimization of Stacked Nanosheet RF for 6G Applications(Indo-Taiwan Joint Research); Approved

The growing demand for the millimeter-wave (mmW) band (30-300 GHz) is driven by its shorter wavelengths and wider frequency bands, enabling the development of smaller components with enhanced performance. Monolithic microwave integrated circuits (MMICs) based on GaN technology play a critical role in fulfilling the requirements of the mmW range. Our reserach interest focused on:

The growing demand for the millimeter-wave (mmW) band (30-300 GHz) is driven by its shorter wavelengths and wider frequency bands, enabling the development of smaller components with enhanced performance. Monolithic microwave integrated circuits (MMICs) based on GaN technology play a critical role in fulfilling the requirements of the mmW range. Our reserach interest focused on:

Electrostatic discharge (ESD) is a serious threat in the semiconductor industry, capable of

causing failures and damage in electronic devices due to rapid electrical charge transfer.

Voltages during ESD incidents can exceed device limits, resulting in failures like dielectric

breakdown and thermal damage etc. Therefore, our reserach interest focused on:

Electrostatic discharge (ESD) is a serious threat in the semiconductor industry, capable of

causing failures and damage in electronic devices due to rapid electrical charge transfer.

Voltages during ESD incidents can exceed device limits, resulting in failures like dielectric

breakdown and thermal damage etc. Therefore, our reserach interest focused on: